SIDesigner is dedicated to comprehensively addressing the signal integrity challenges faced by DDR

-

2025.02.11

引言:内存(DRAM-Random Access Memory)作为现代数字系统的核心组件之一,在计算机、汽车与消费电子产品上可谓无所不在。

其中 DDR SDRAM(双数据率同步动态随机存取存储器,Double Data Rate SDRAM)是最常用的存储器设计技术之一,DDR技术自推出以来,经历了多次迭代,包括DDR2、DDR3、DDR4以及最新的DDR5,每一代都在速度、容量和能效方面有所提升。随着移动互联网时代的到来,海量数据的爆发、AI和深度学习的兴起,以及5G技术的推动,DDR4标准在个人信息终端上已显得力不从心。

如今,DDR5正与PCIE5.0 32Gbps等第5代高速I/O数据传输技术共同迈向市场。传输速度加快使得此类存储器的验证难度呈指数上升。随着DDR技术的不断发展,信号完整性问题变得越来越重要。

DDR的工作机制与其信号的组成介绍

一、DDR的基本工作原理

DDR内存的工作原理可以概括为以下几个关键点:

1. 双倍数据速率

在传统的SDR内存中,数据只在时钟的上升沿传输。而在DDR内存中,数据在时钟的上升沿和下降沿都传输,因此每个时钟周期可以传输两次数据,从而实现双倍的数据速率。

2.预取机制(Prefetch)

DDR内存采用预取技术来提高数据传输效率。预取是指内存控制器一次从内存阵列中读取多个数据位,然后分批次传输。例如:DDR1采用2n预取(每次预取2位数据),DDR2采用4n预取,DDR3和DDR4采用8n预取,DDR5采用16n预取。

3. 差分时钟信号

DDR使用差分时钟信号(CLK和CLK#)来提高抗噪声能力和信号完整性。差分时钟信号通过比较CLK和CLK#的电压差来确定时钟边沿。

4. 数据选通信号(DQS)

DQS信号用于同步数据信号的采样。在写入操作时,DQS由内存控制器发出;在读取操作时,DQS由内存芯片发出。DQS也是差分信号(DQS和DQS#),确保数据在正确的时刻被采样。

DDR的信号组成

1. 时钟信号(CLK)

作用:时钟信号是DDR数据传输的核心,用于同步所有操作。

特点:DDR使用差分时钟信号(CLK和CLK#),以提高抗噪声能力。数据在时钟的上升沿和下降沿都被采样,从而实现双倍数据速率。

2. 数据信号(DQ)

作用:用于传输实际的数据。

特点:数据信号是双向的,既可以写入内存,也可以从内存读取。数据信号的宽度通常为64位(8字节),但也支持更宽的配置(如72位,带ECC校验)。

3. 数据选通信号(DQS)

作用:用于同步数据信号的采样。

特点:DQS也是差分信号(DQS和DQS#),与数据信号(DQ)一一对应。在写入操作时,DQS由控制器发出;在读取操作时,DQS由内存芯片发出。

重要性:DQS信号确保数据在正确的时刻被采样,避免时序错误。

4. 地址信号(ADDR)

作用:用于指定内存中数据的存储位置。

特点:地址信号是单向的,由内存控制器发出。地址信号的宽度决定了内存的容量(例如,DDR4支持最多16Gb的单个内存芯片)。

5. 控制信号(CMD)

作用:用于控制内存的操作,如读取、写入、刷新等。常见控制信号:RAS#(行地址选通):选择行地址。CAS#(列地址选通):选择列地址。WE#(写使能):控制写入操作。CS#(片选):选择特定的内存芯片。

特点:控制信号通常是低电平有效(以“#”表示)。

6. 电源和地信号(VDD/VSS)

作用:为内存芯片提供电源和地。

特点:DDR4和DDR5采用更低的电压(如DDR4为1.2V,DDR5为1.1V),以提高能效。电源信号的稳定性对信号完整性至关重要。

7. 其他信号

ODT(On-Die Termination,片上终端):用于匹配阻抗,减少信号反射。

CKE(Clock Enable,时钟使能):控制时钟信号的启用和禁用。

ZQ(校准信号):用于调整驱动强度和终端电阻。

二、DDR工作机制与信号组成的关系

DDR的工作机制依赖于其信号组成,各类信号协同工作以实现高效的数据传输:

1. 写入操作:内存控制器发出写入命令,并发送地址信号(ADDR)和数据信号(DQ)。控制器同时发出数据选通信号(DQS),用于同步数据信号的采样。数据在DQS的上升沿和下降沿被写入内存阵列。数据信号(DQ)和DQS信号由控制器驱动。写入操作需要满足建立时间和保持时间的要求。

2. 读取操作:内存控制器发出读取命令,并发送地址信号(ADDR)。内存芯片根据地址从内存阵列中读取数据。内存芯片发出数据信号(DQ)和数据选通信号(DQS),用于同步数据传输。控制器在DQS的上升沿和下降沿采样数据。数据信号(DQ)和DQS信号由内存芯片驱动。读取操作需要满足时序要求,确保数据在正确的时刻被采样。

DDR的时序控制是其工作机制的核心,主要包括以下几个关键时序参数:

1. 时钟周期(tCK)决定了DDR的数据传输速率。

2. CAS延迟(CL,Column Address Strobe Latency)从发出读取命令到数据输出的延迟时间,影响读取操作的响应速度。

3. RAS到CAS延迟(tRCD,RAS to CAS Delay)从行地址选通(RAS)到列地址选通(CAS)的延迟时间,影响内存访问的效率。

4. 预充电时间(tRP,Row Precharge Time)指的是关闭当前行并准备打开新行所需的时间,其影响内存的切换效率。

5. 刷新周期(tREF,Refresh Interval)定期刷新以保持数据的时间间隔,确保数据不会因电容放电而丢失。

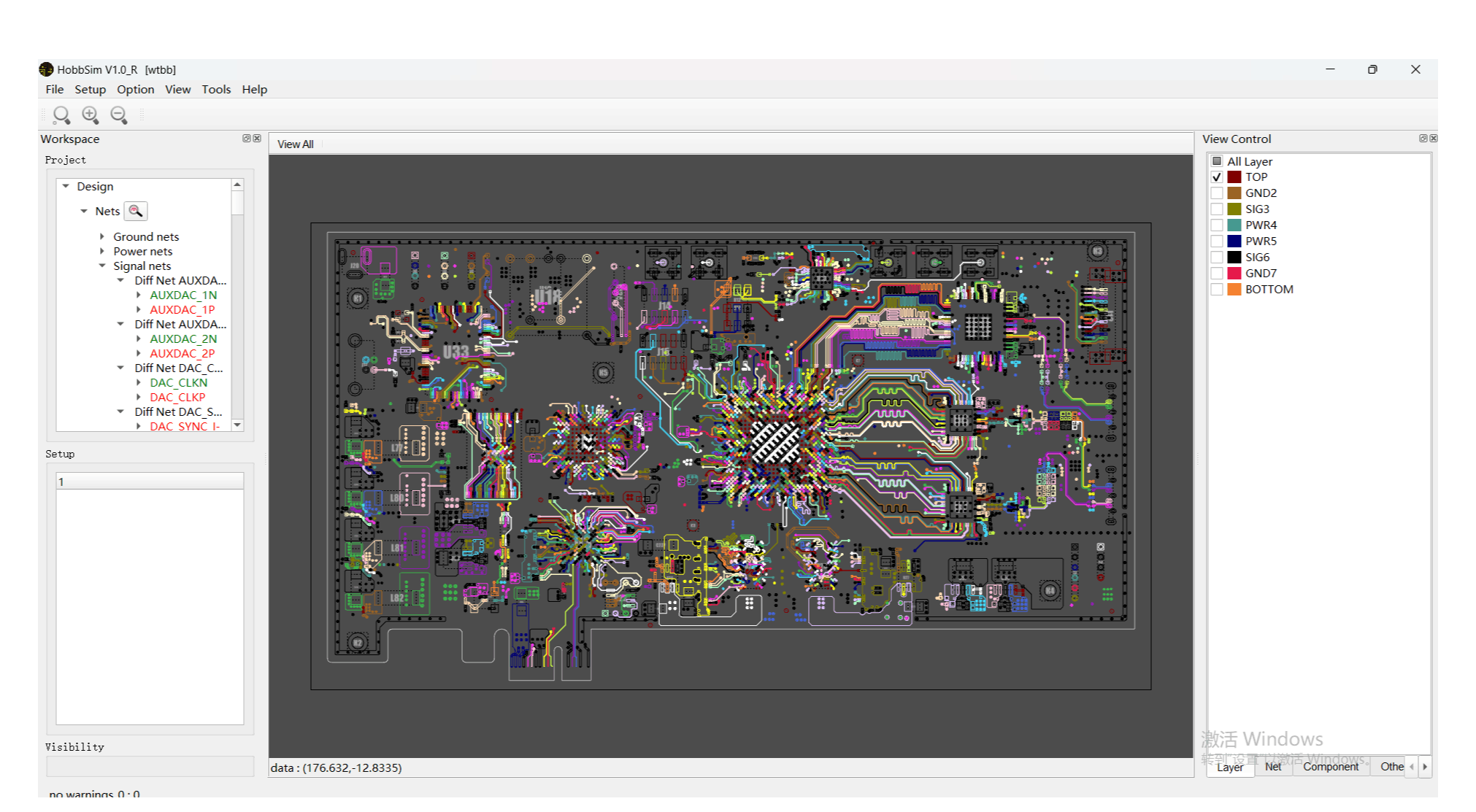

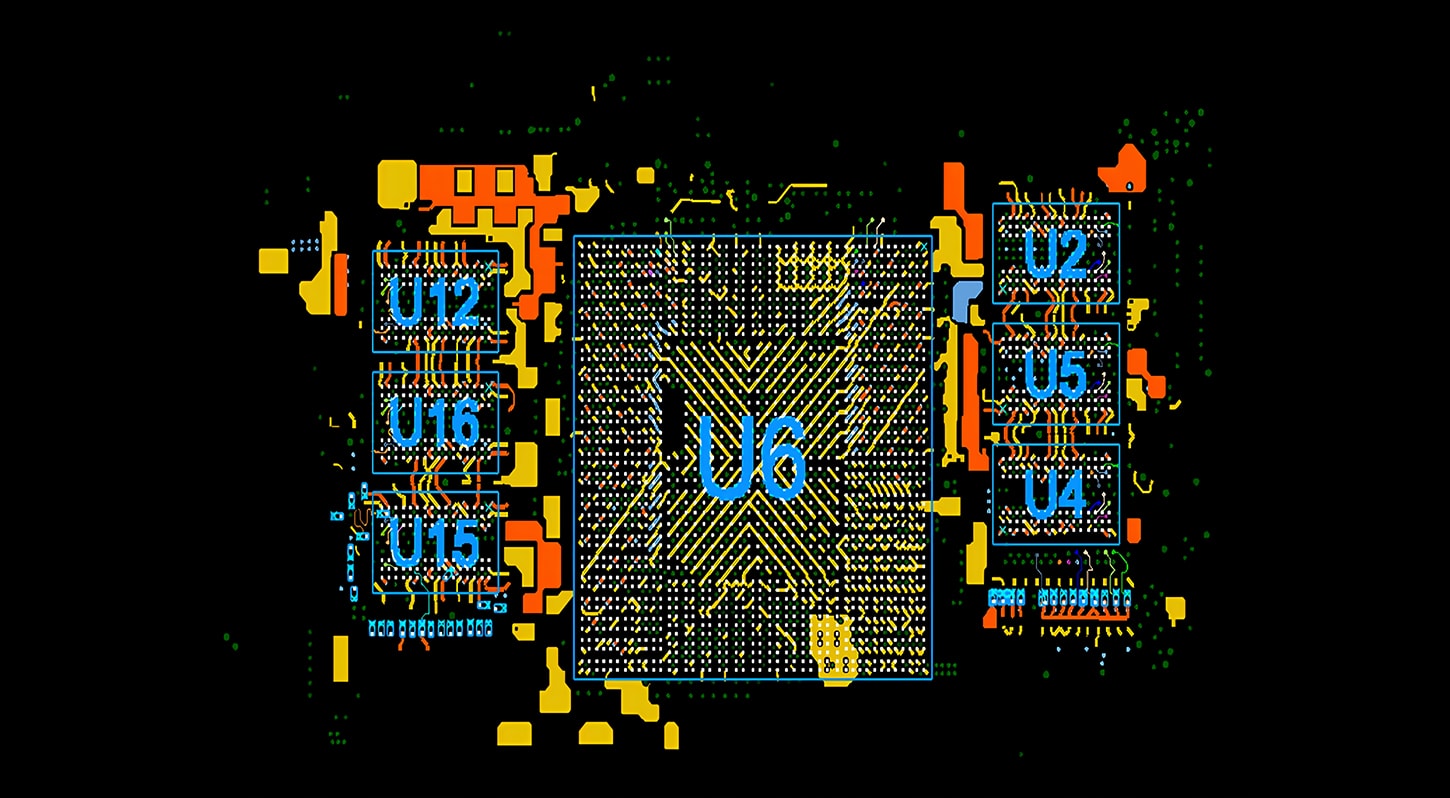

三、SIDesigner与DDR

SIDesigner致力于全方位解决DDR面临的信号完整性挑战

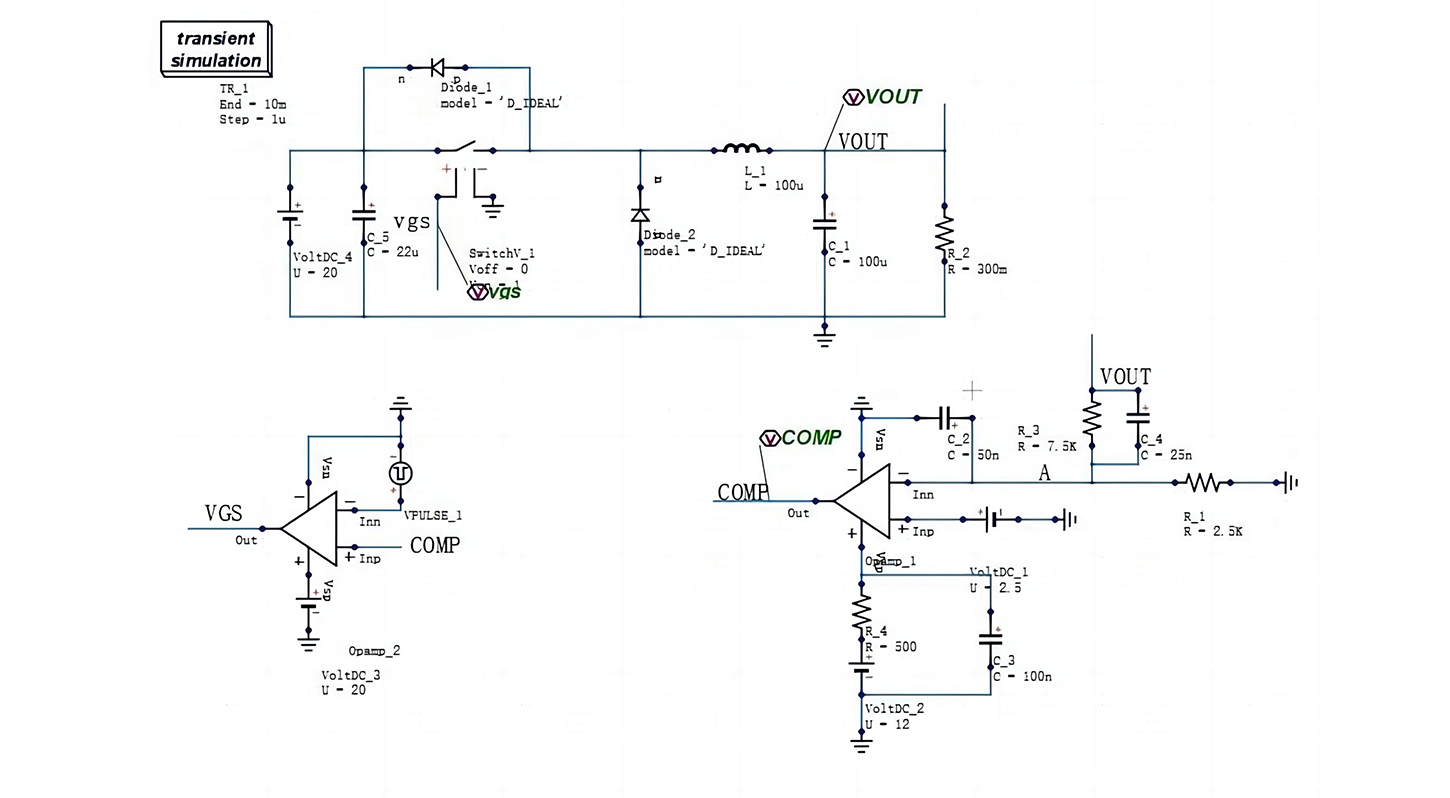

在高速数据传输中,信号可能会受到多种因素的影响,导致信号失真、时序错误或数据丢失。DDR信号完整性的主要挑战包括:信号在传输线末端或阻抗不匹配处反射,导致信号叠加和失真。相邻信号线之间的电磁干扰产生的串扰,导致信号质量下降。时钟信号的微小变化引起的时钟抖动可能导致数据采样错误。电源噪声会影响信号的稳定性和可靠性。

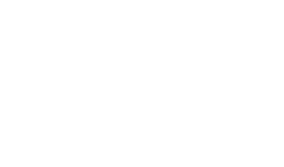

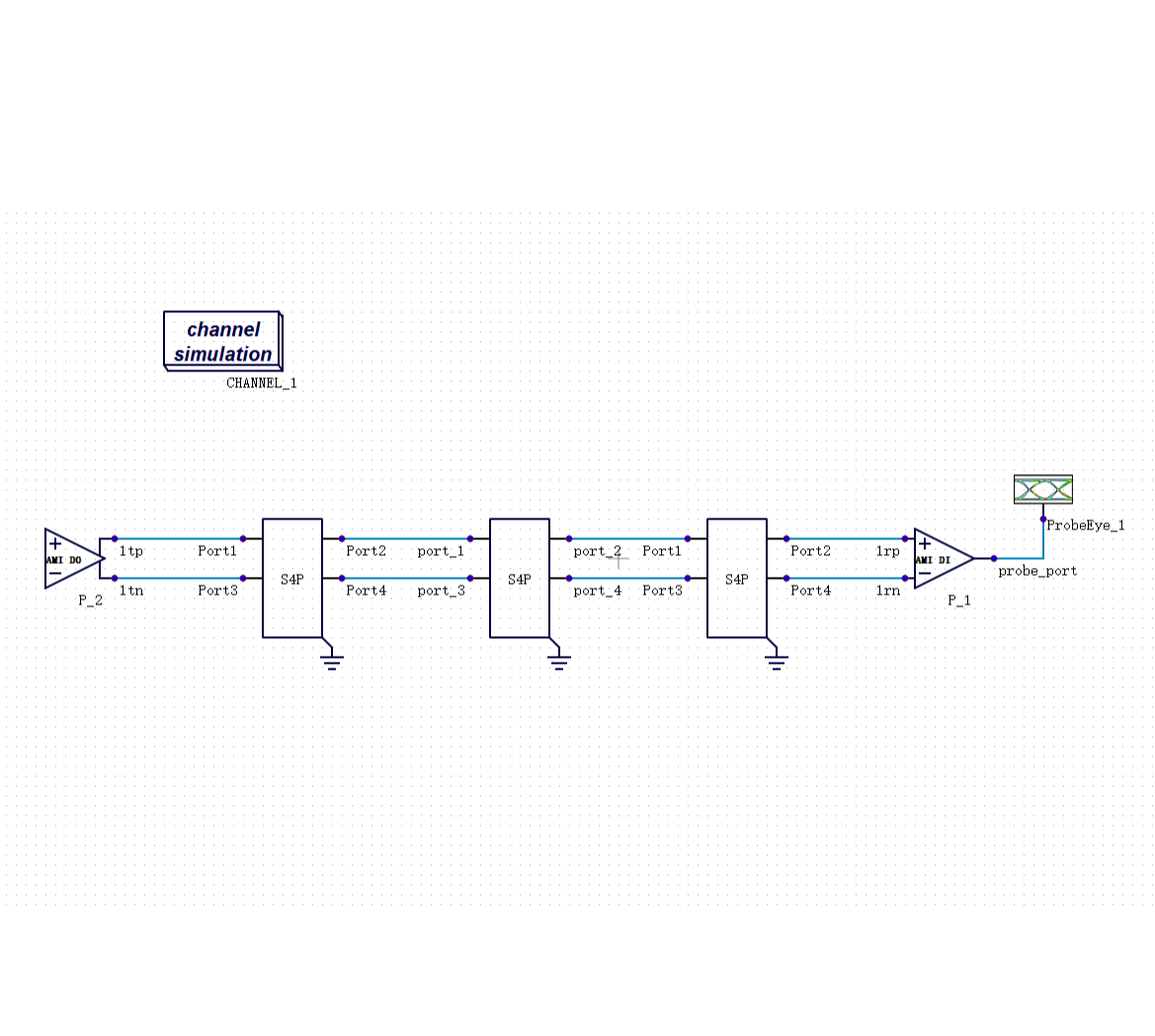

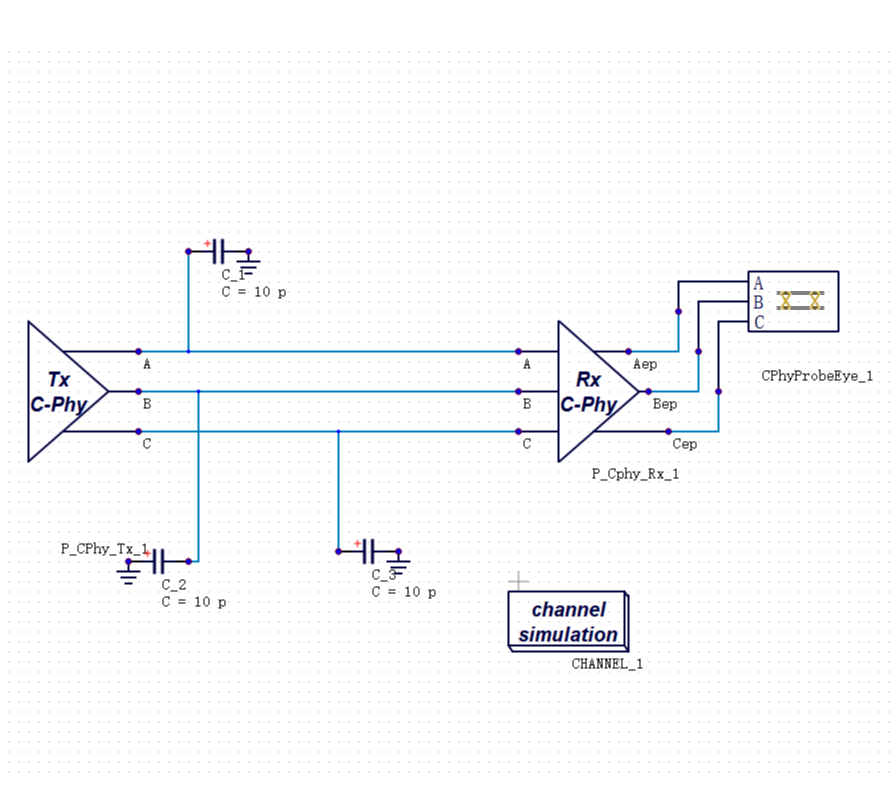

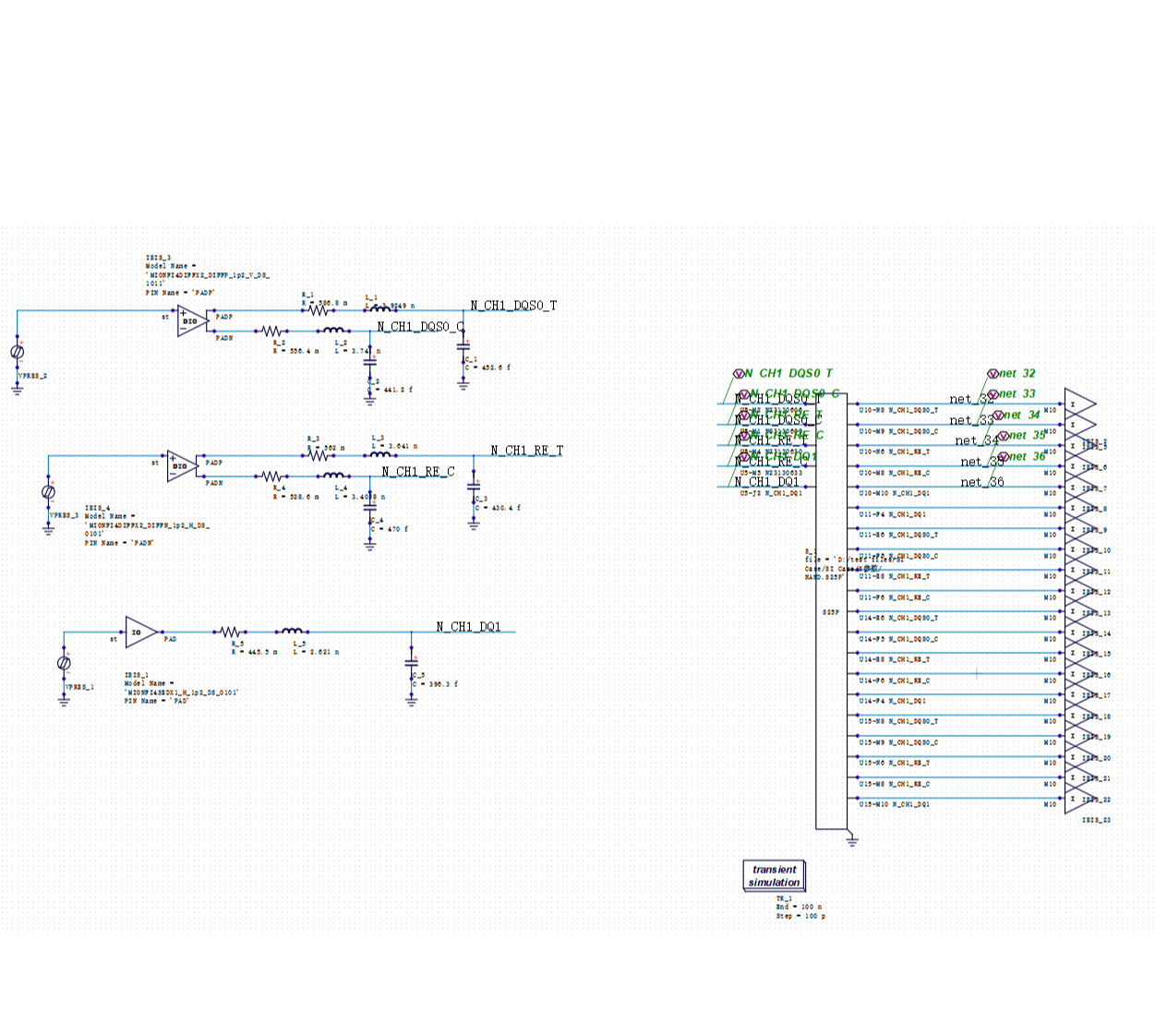

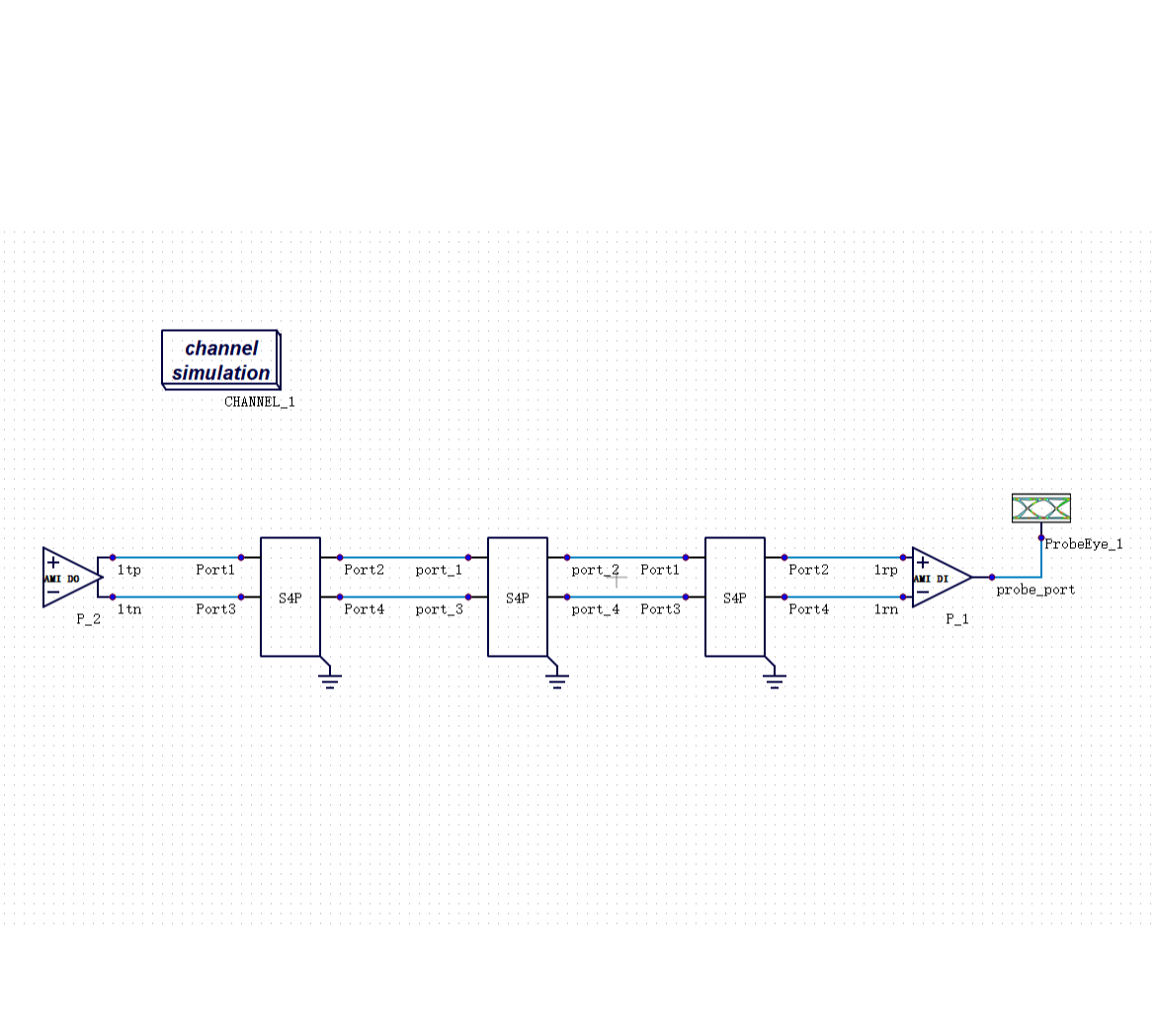

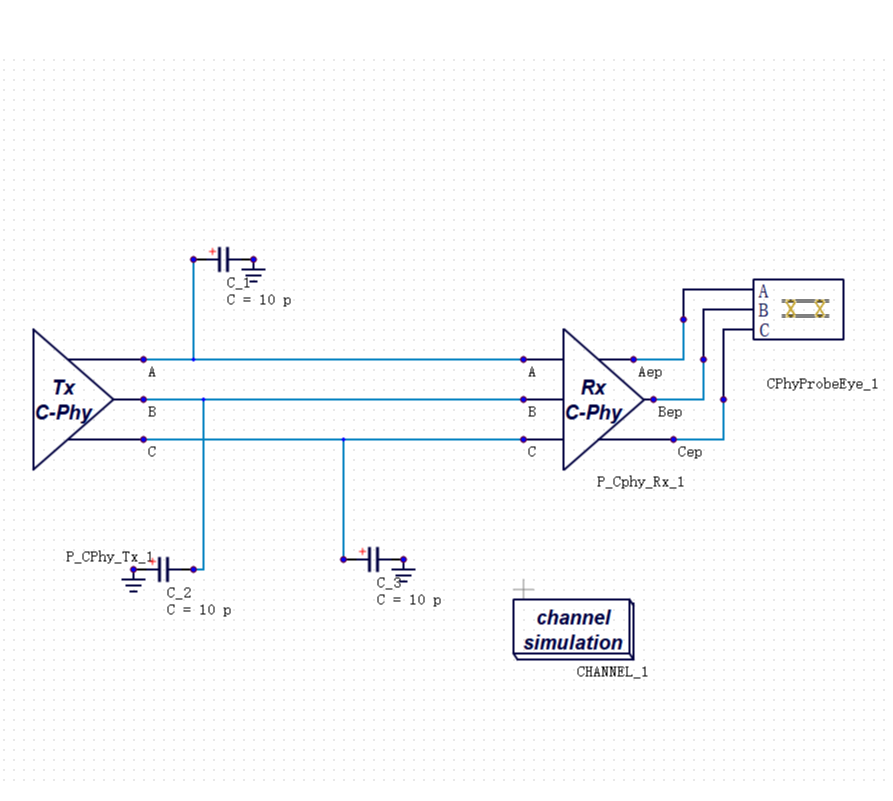

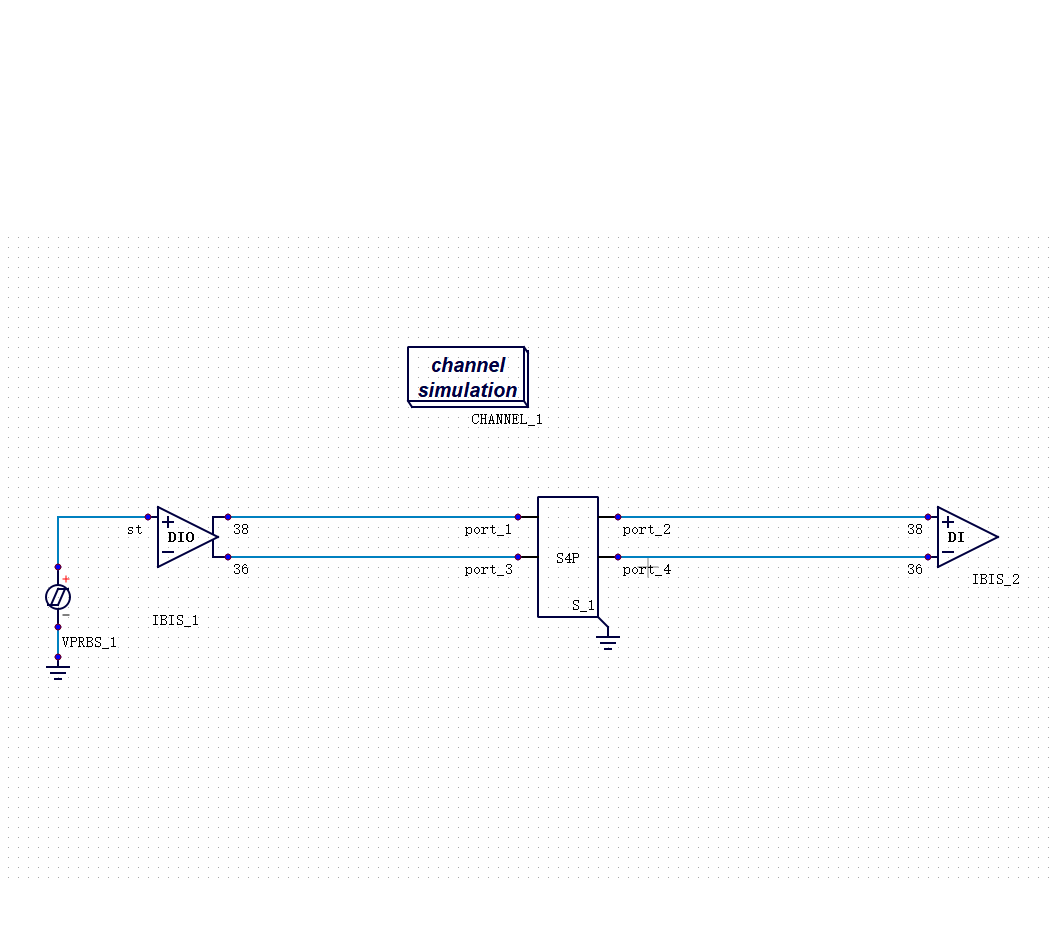

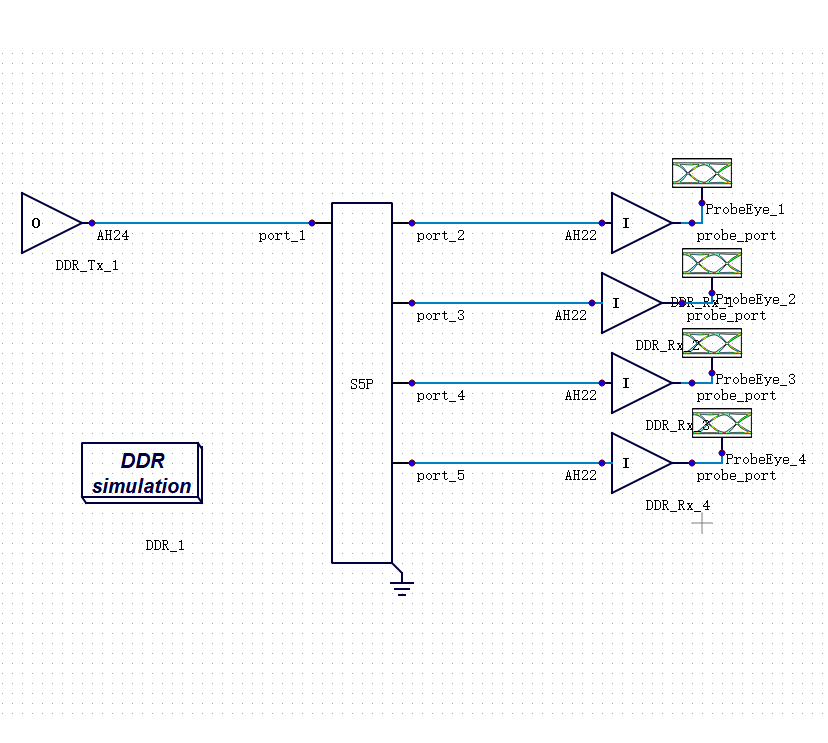

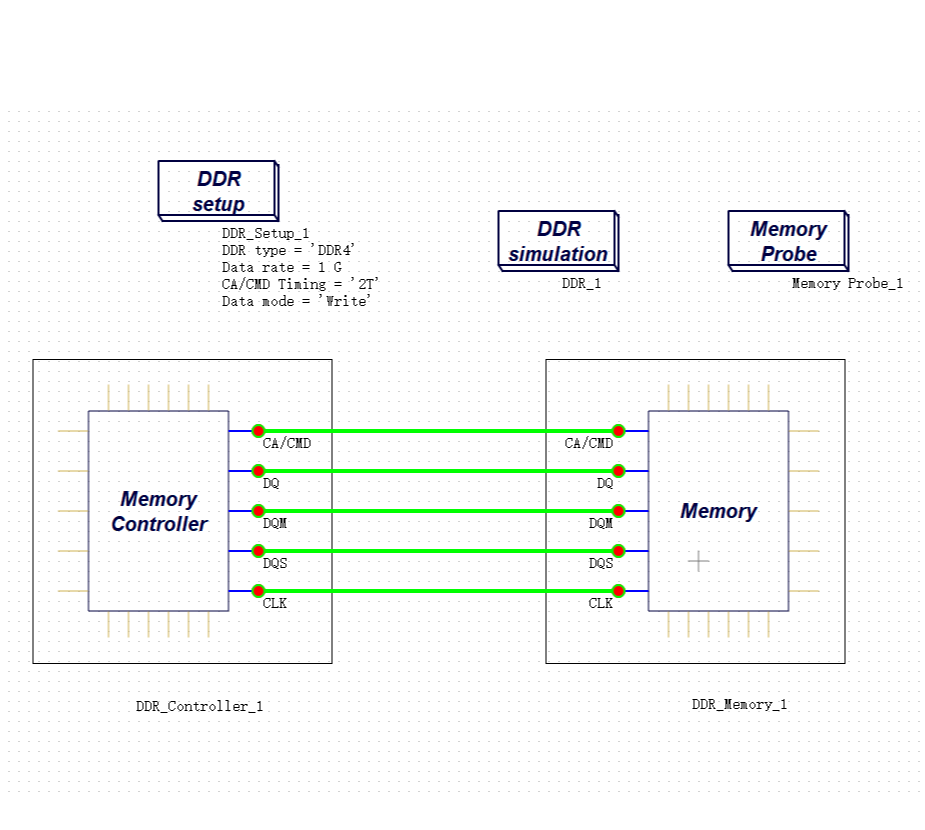

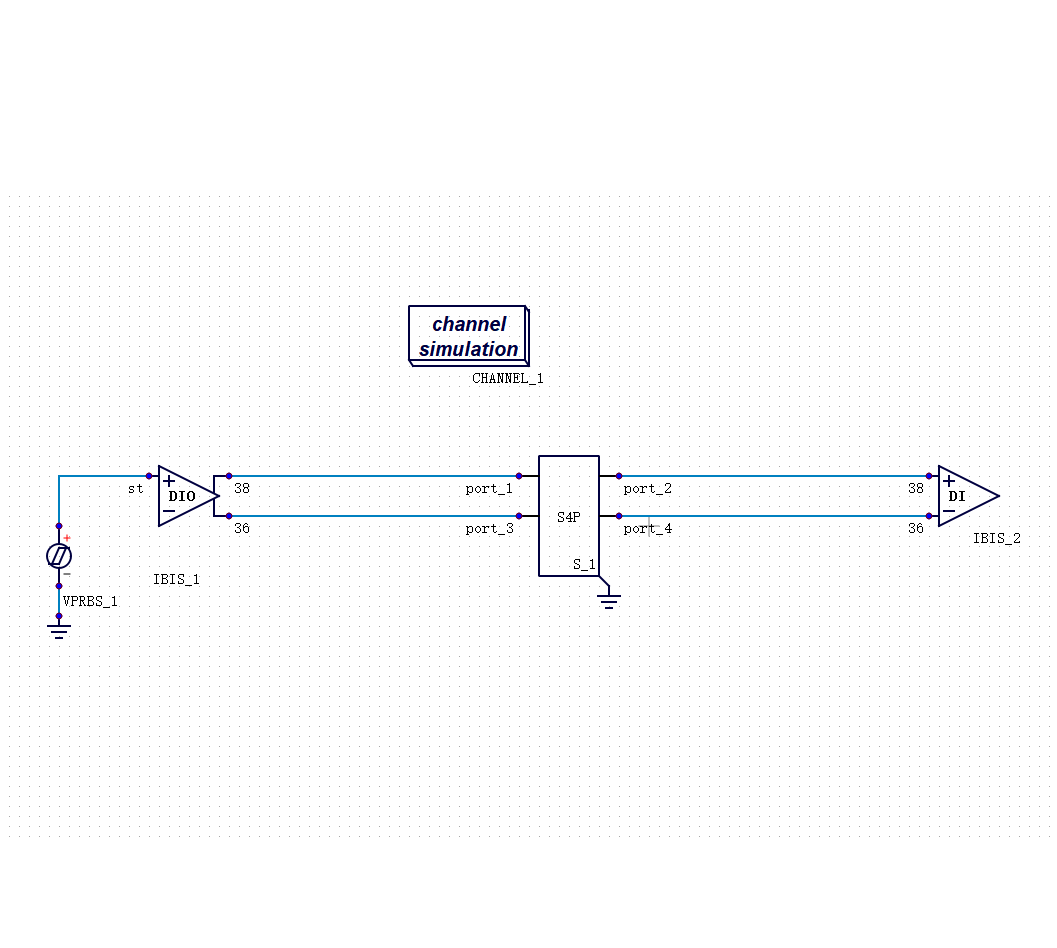

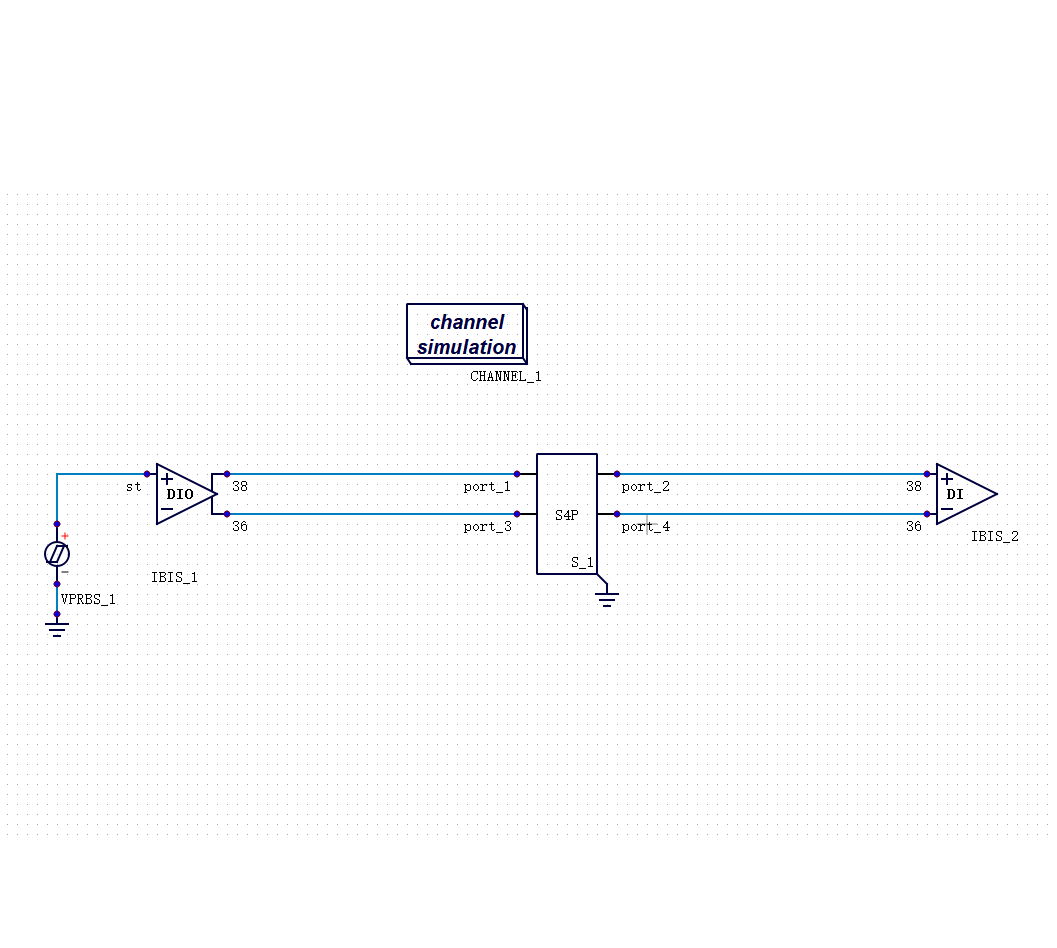

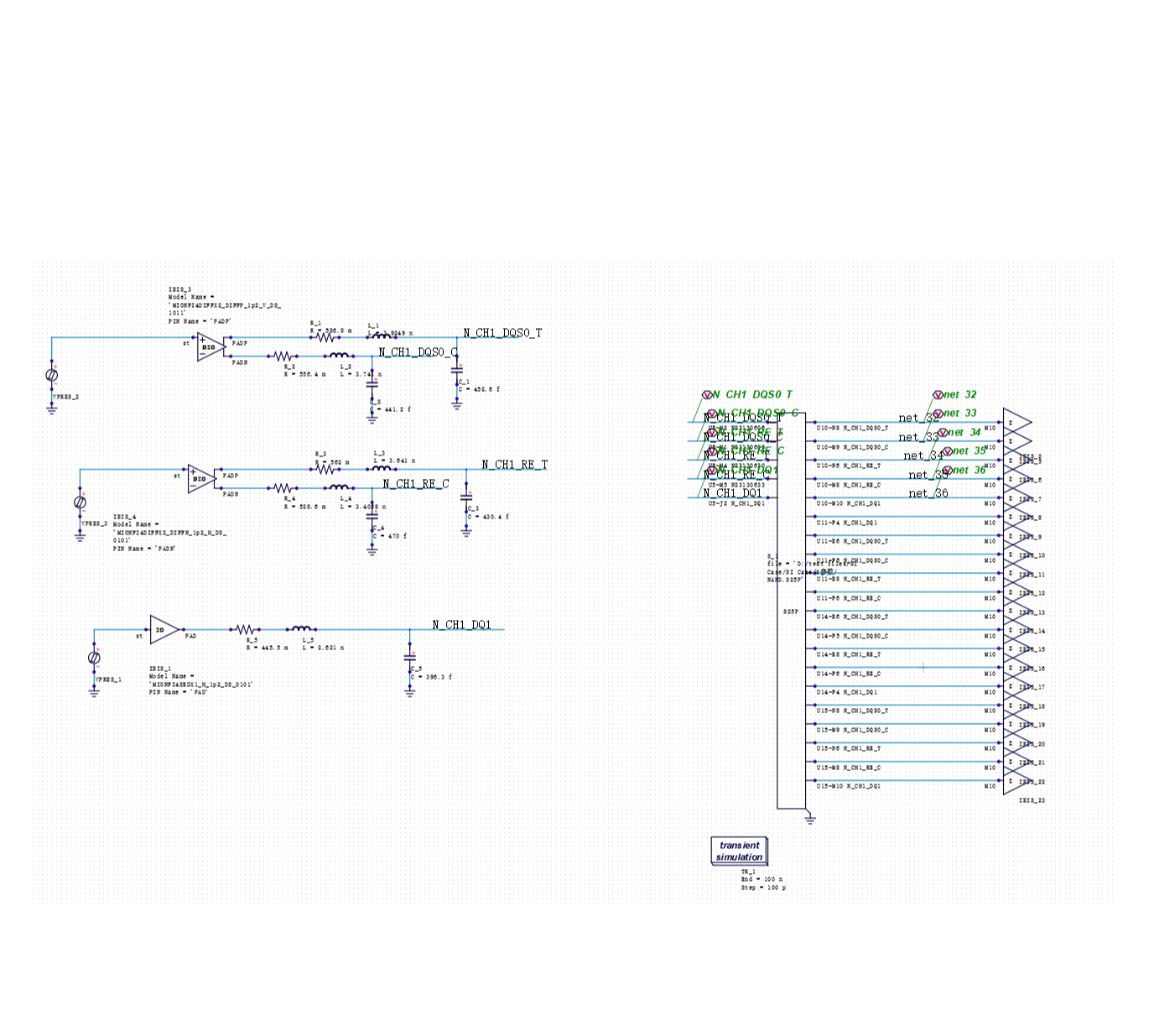

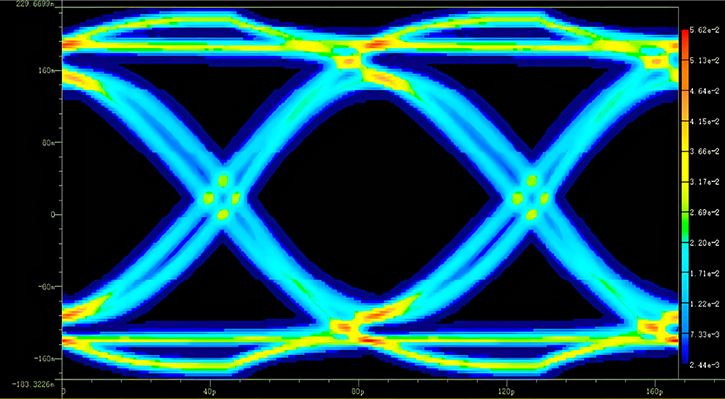

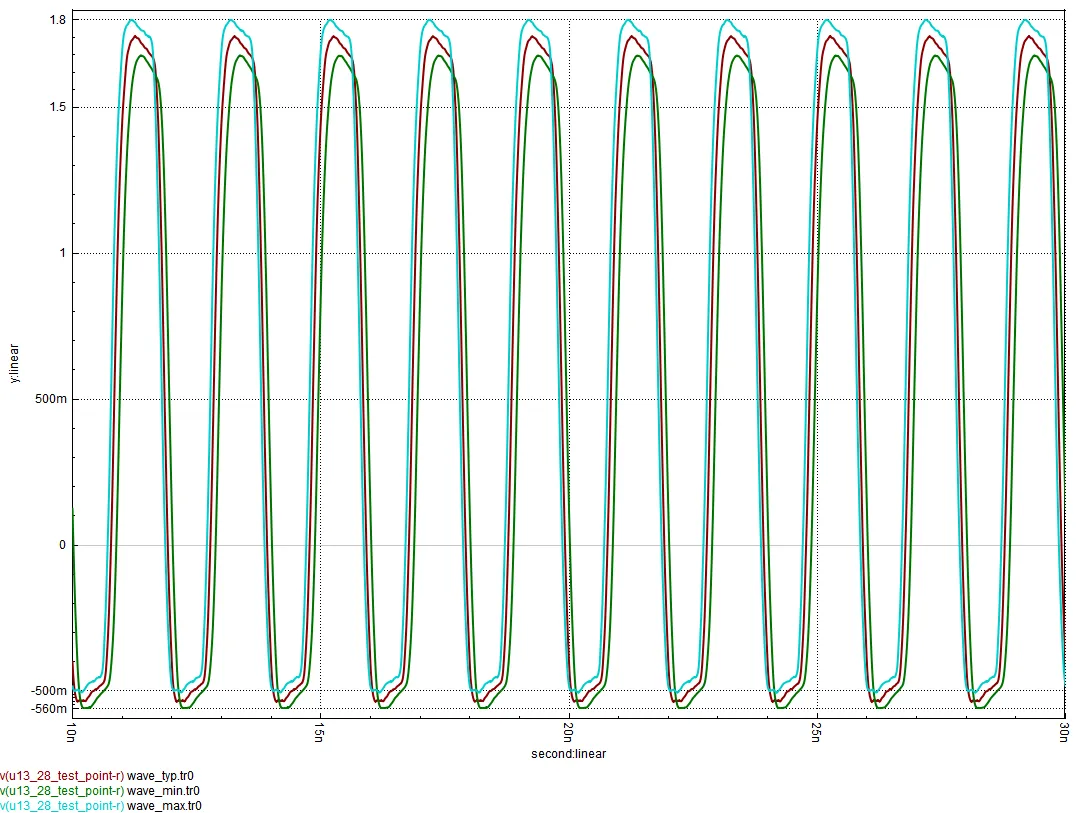

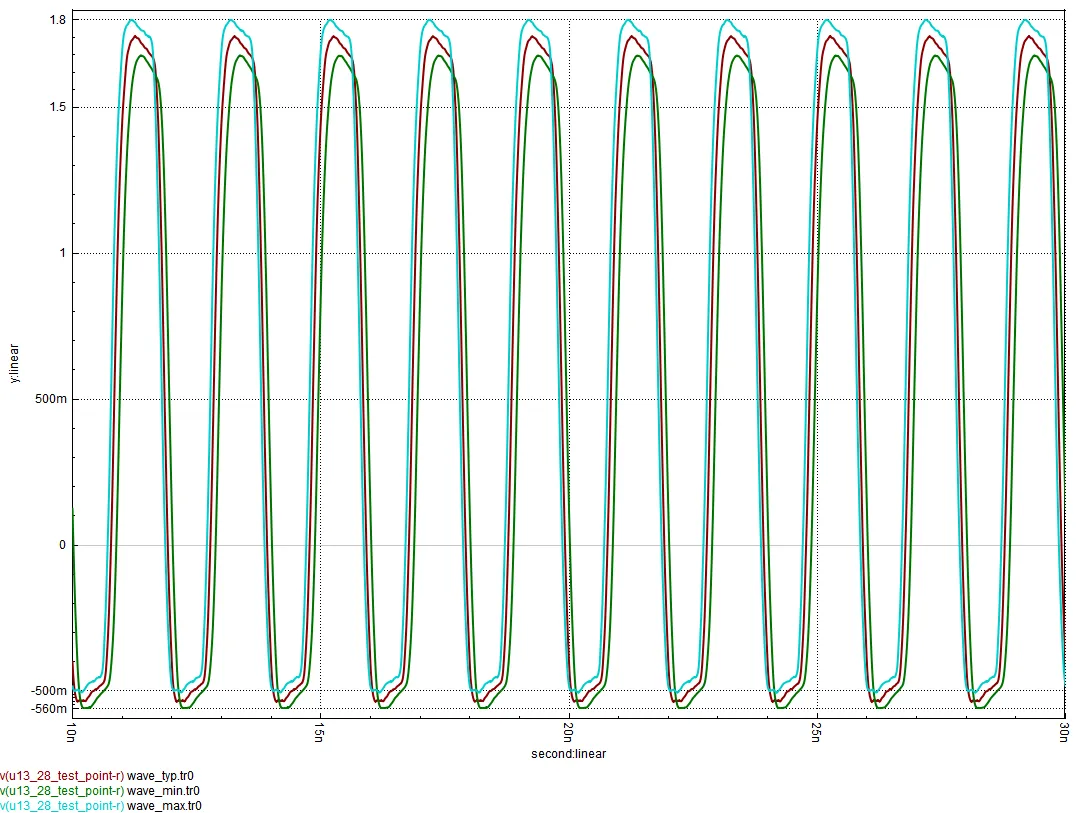

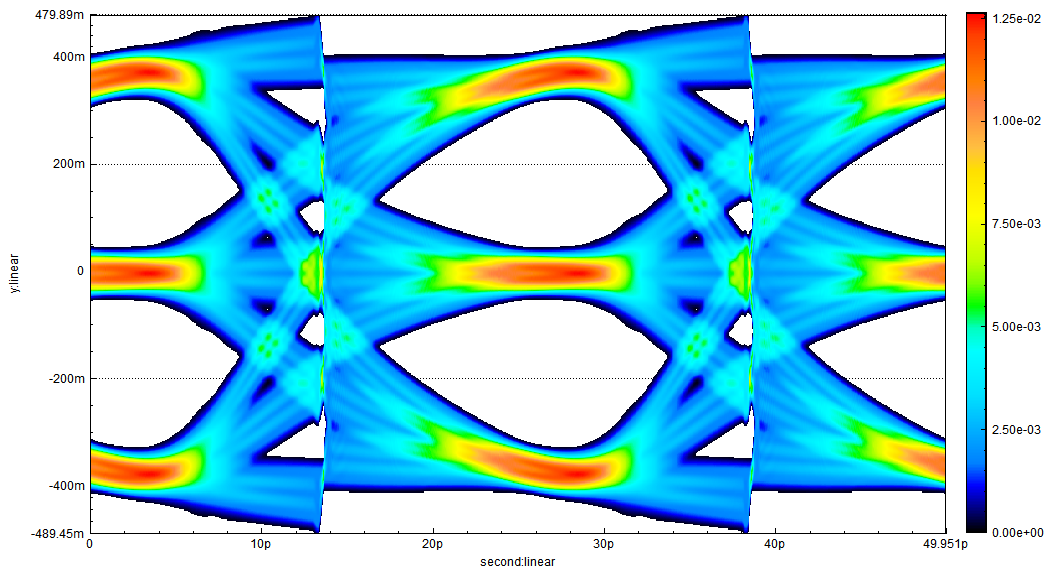

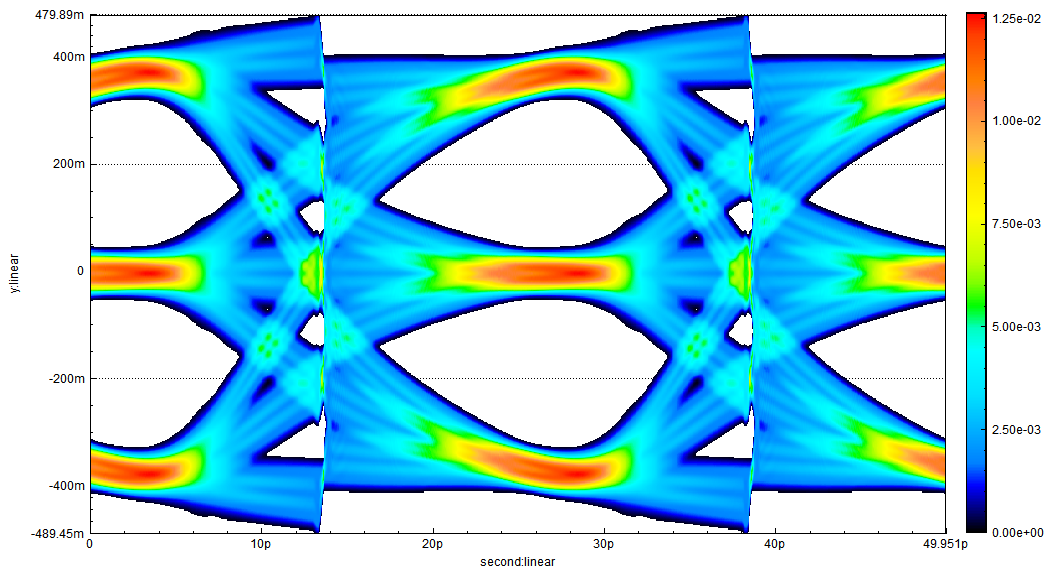

通过巨霖的SIDesigner进行高精度的DDR的仿真,可以预测信号在传输过程中各个端口之间的串扰和反射的行为。在仿真后得到眼图(Eye Diagram),通过观测眼图可以直观地显示信号的抖动、噪声和失真情况。

并且通过软件内置的测量工具来测量眼图来评估信号的质量,通过测量眼图的眼高来确定信号的幅度稳定性,测量眼宽来确定信号的时间裕量。同时可以导入对应的DDR眼图模板来进行多信号观测,看是否满足设计规范。

通过SIDesigner也可以计算得到眼图的误码率曲线来衡量信号质量,同时在仿真中可以通过使用ibis模型中自带的不同的ODT模型来进行阻抗匹配的分析来获取最优的信号质量,同时通过仿真clk信号,观测交叉点是否居中,验证时钟信号和数据信号之间的时序关系,确保数据在正确的时刻被采样。

SIDesigner也支持导入实际的电源噪声进行仿真来考虑电源对信号的影响。通过SiDesigner的高精度仿真工程师可以直观的观测到信号的质量问题,分析这些问题后,通过修改原理图继续仿真来获得符合预期设计规范的信号。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

Recommended

-

Process Corners and Applications in IBIS Modeling2025.04.23

Process Corners and Applications in IBIS Modeling2025.04.23 -

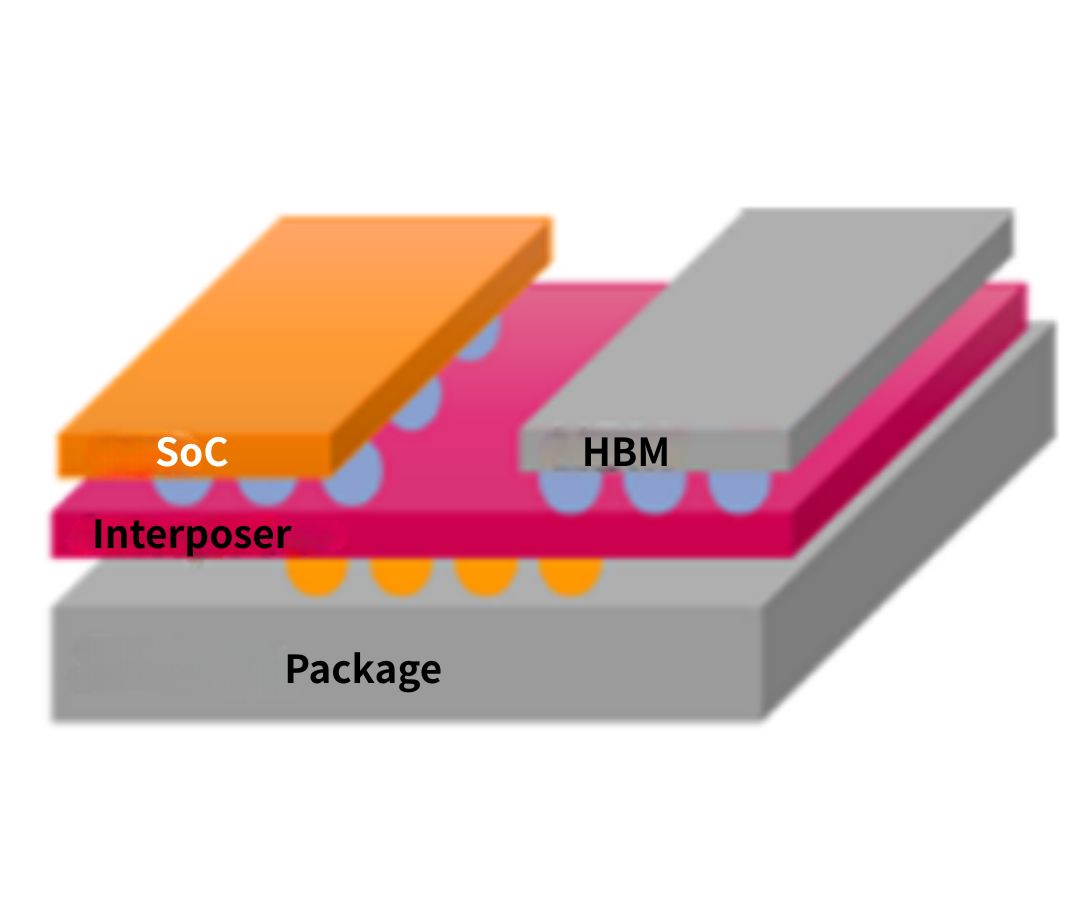

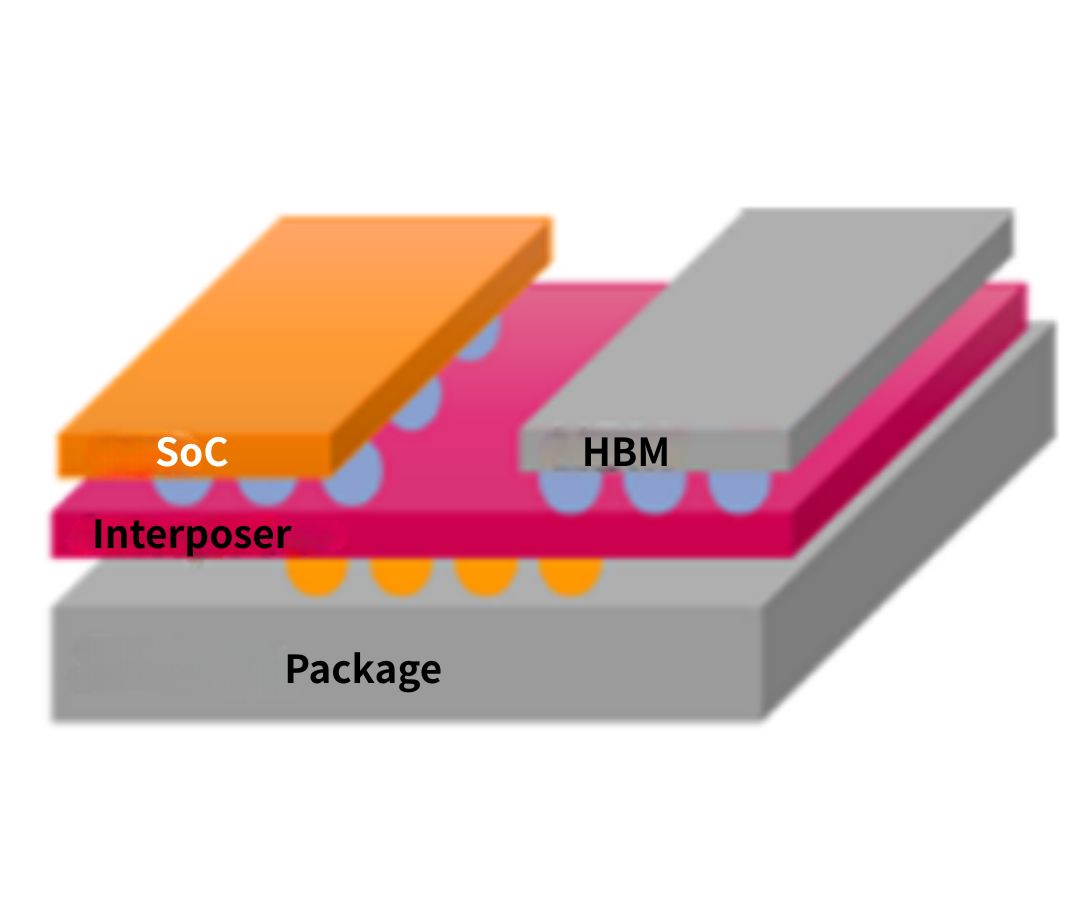

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (II)2025.04.21

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (II)2025.04.21 -

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (I)2025.04.11

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (I)2025.04.11 -

PAM3 Encoding and Simulating Verification in High-Speed Transmission2025.03.31

PAM3 Encoding and Simulating Verification in High-Speed Transmission2025.03.31