Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (I)

-

2025.04.11

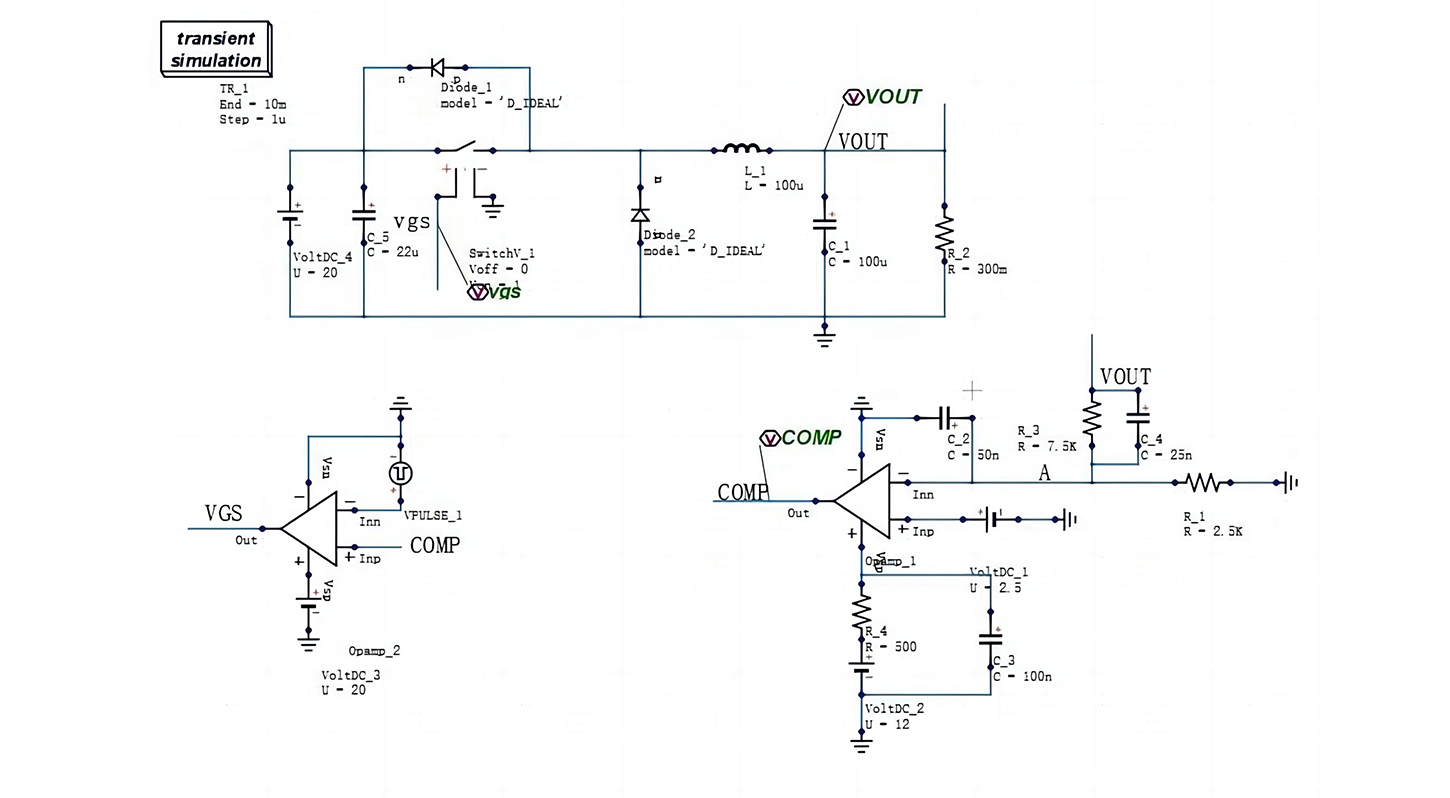

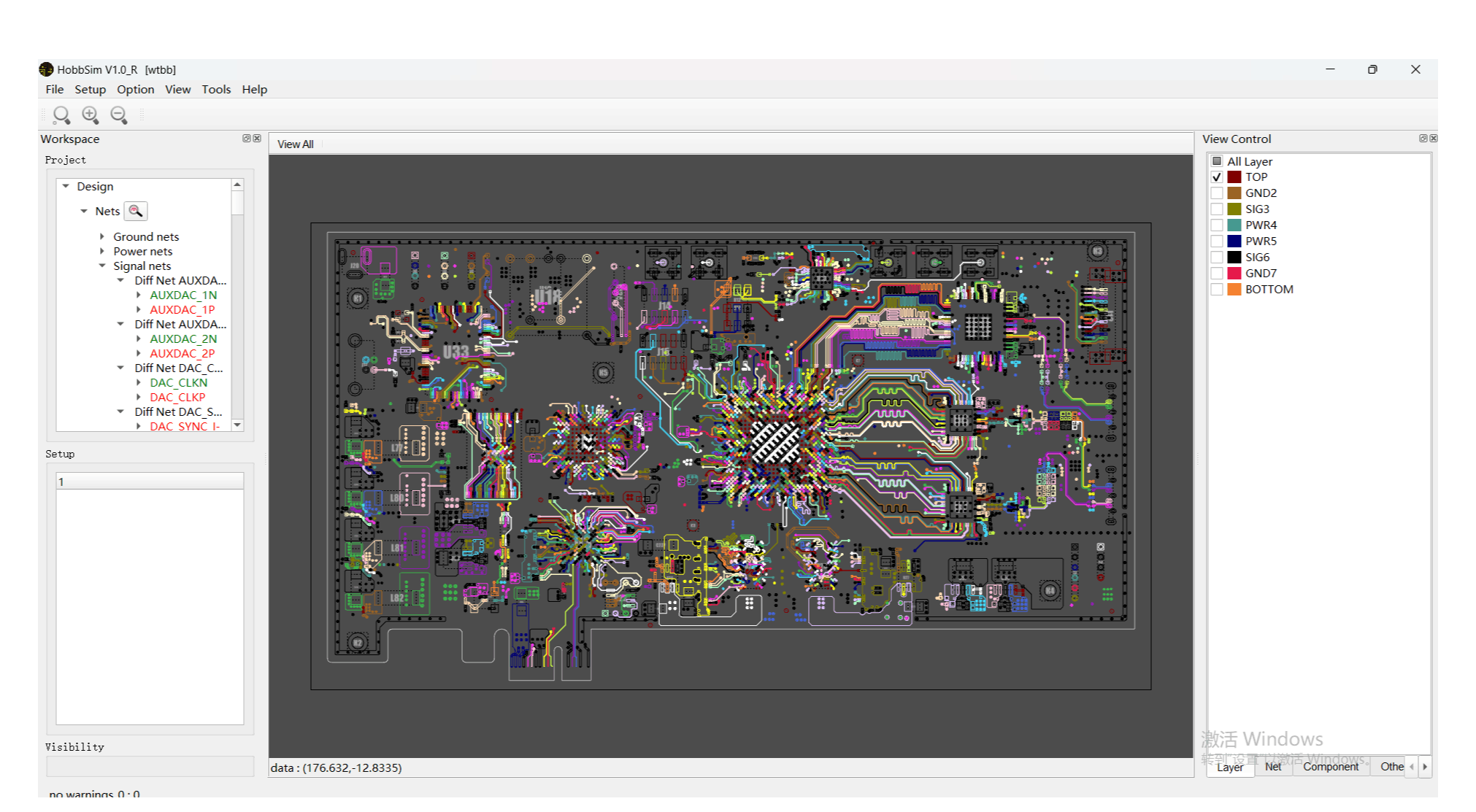

随着半导体行业的技术进步,尤其是摩尔定律的放缓,芯片设计和制造商们逐渐转向了更为灵活的解决方案,其中“Chiplet”和“先进封装”成为了热门的概念。它们不仅为解决传统单片集成芯片(SoC)面临的尺寸、成本和性能瓶颈提供了创新思路,也带来了全新的设计和制造挑战。特别是在这一过程中,EDA工具的角色变得尤为关键,但也面临着许多技术上的难题。该文从介绍Chiplet与先进封装入手,分析两者结合面临的挑战,并探索如何通过EDA工具去解决这些行业痛点。

一、Chiplet与先进封装的关系

1、什么是 Chiplet?

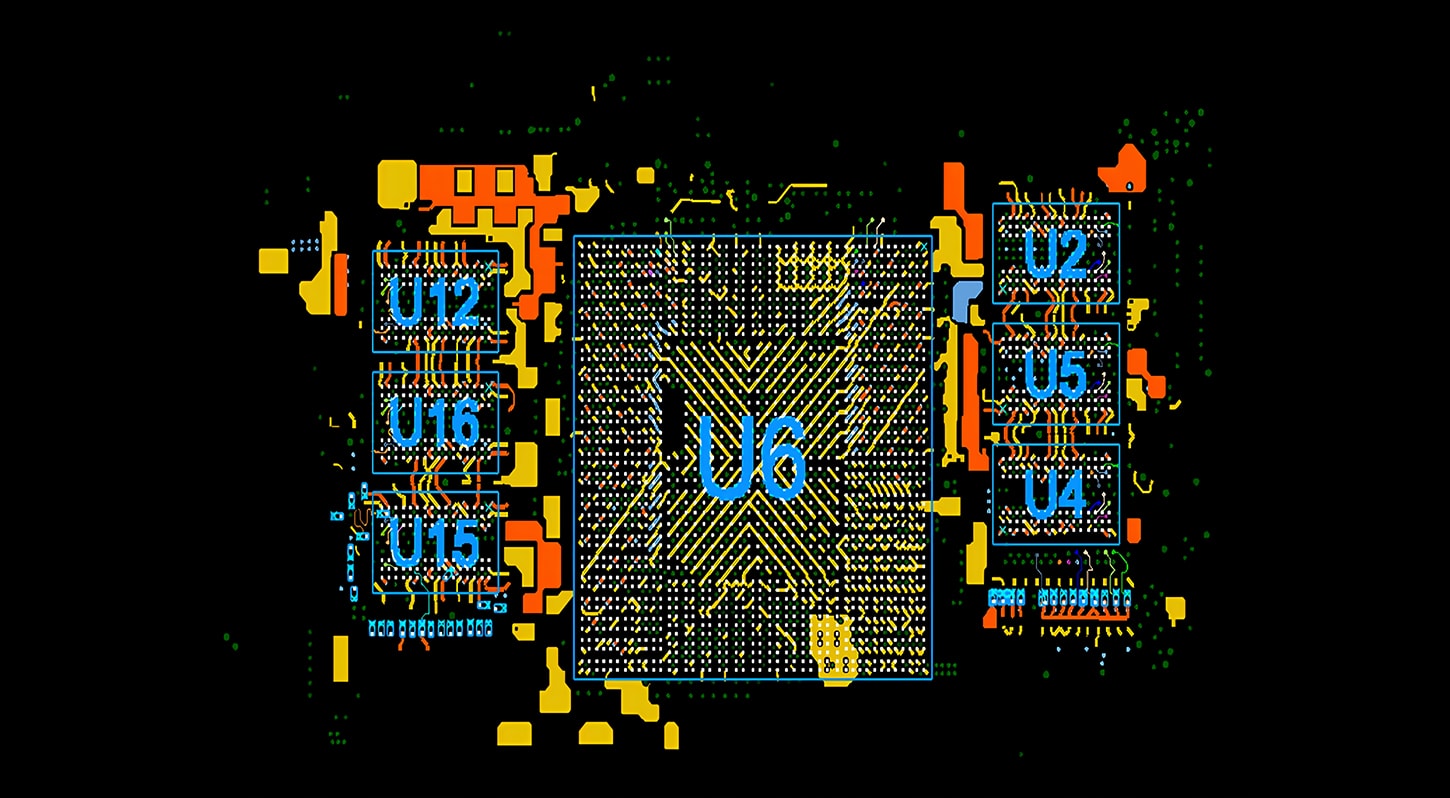

Chiplet是一种将复杂芯片系统分解为多个较小、相对独立的功能单元的设计方式。这些芯片模块可以在一个集成封装中以不同的方式组合,以构建出一个完整的系统。例如,一个高性能的计算平台可能包含多个处理核心、存储控制器、通信接口等,这些功能模块被拆分成不同的Chiplet。它们通过高速的互联方式(如高速串行总线、片内光互联等)连接在一起,以实现系统级的协同工作。

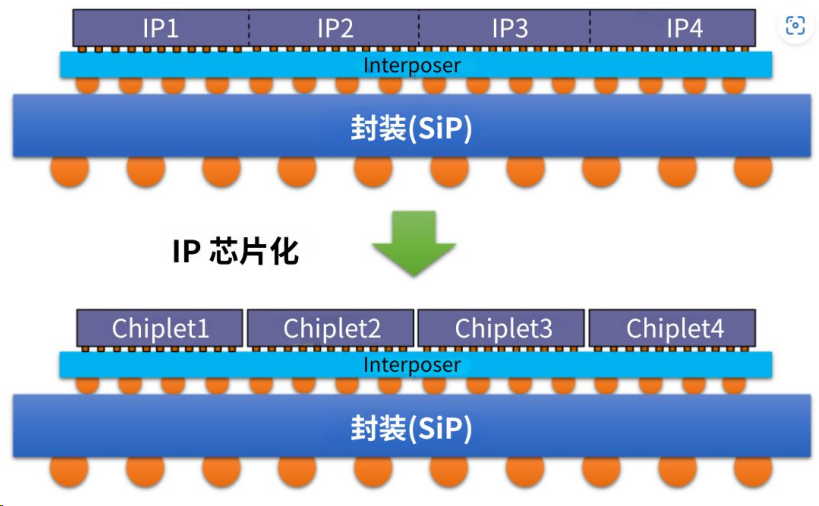

2、Chiplet 的变革

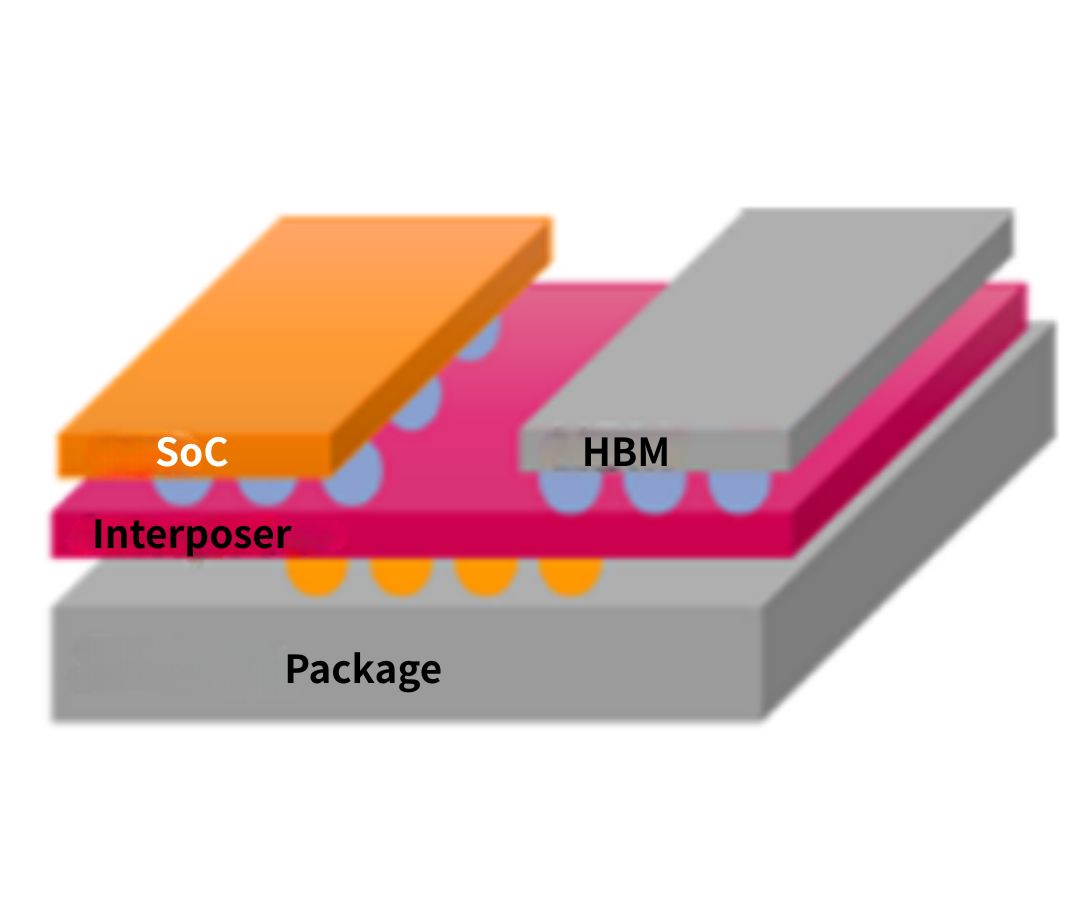

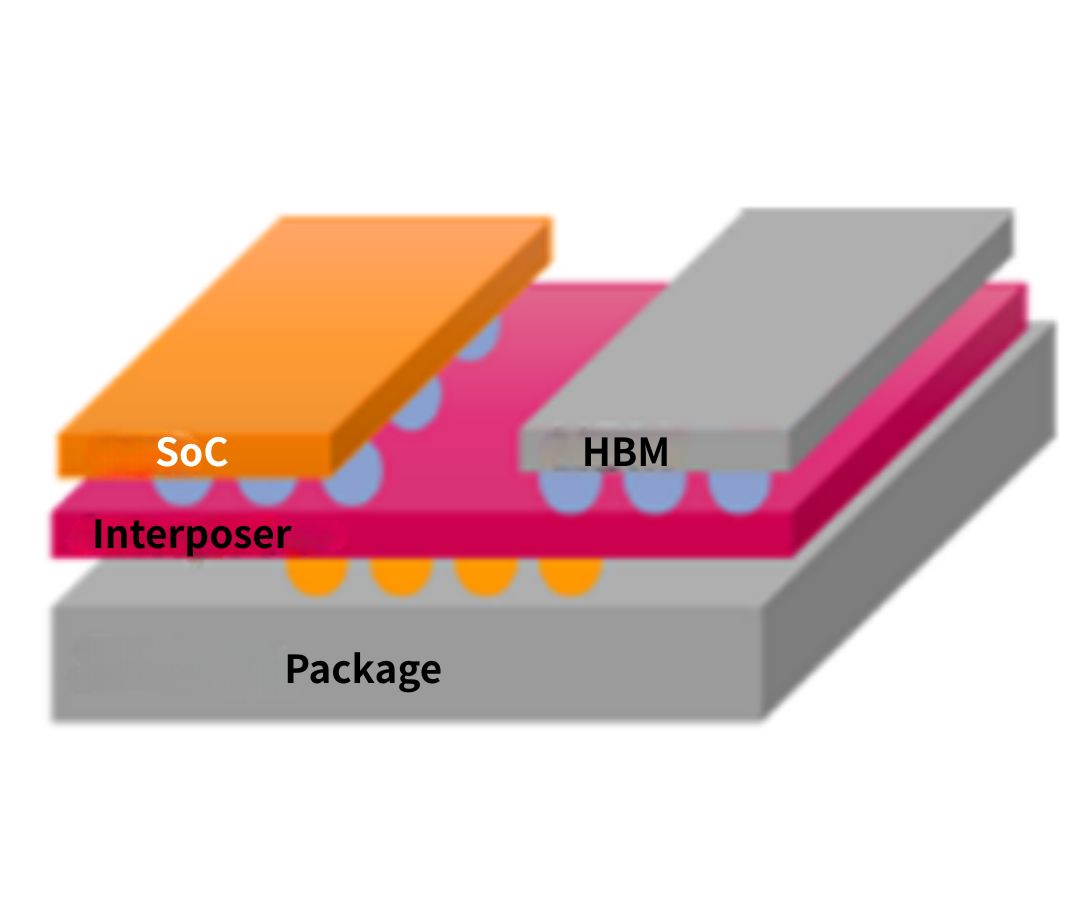

在传统SoC设计中,开发者通常需要从不同的IP供应商获取软核(RTL代码)、固核(门级网表)或硬核(GDSII版图),再结合自研模块,在特定工艺节点(如7nm、5nm)上完成芯片的集成、设计和制造。这种方案需要经历完整的流片过程,开发周期长,且大尺寸单芯片的良率问题可能导致成本上升。Chiplet技术将传统IP复用提升至硅片级:开发者无需自行设计或生产某些功能模块,而是直接采购已流片验证的Chiplet(如计算单元、I/O模块等),通过先进封装技术将这些硅片组合成完整系统。本质上,Chiplet是一种以裸片(Die)形式提供的“硬核IP”,其核心变革在于将系统集成从晶圆级转移到封装级。

3、Chiplet 的核心优势

1.模块化设计,灵活扩展

Chiplet将单芯片拆解为多个功能独立的裸片(Die),支持像“乐高积木”一样按需组合。例如,通过混合搭配计算、存储和通信Chiplet,可快速定制适应AI、HPC等不同场景的解决方案。AMD的EPYC处理器正是通过不同数量的CCD(核心复合裸片)和IOD(I/O裸片)组合实现产品系列化。

2.良率提升与成本优化

小尺寸Chiplet(如3mm×3mm)相比大尺寸SoC(如20mm×20mm)显著降低了晶圆缺陷的影响。根据行业数据,在相同缺陷密度下,Chiplet方案的良率可比传统SoC提高30%以上,从而减少废片损耗。

3.异构集成,性能突破

Chiplet打破工艺和材质的限制,允许将不同制程(如5nm逻辑芯片+28nm模拟芯片)、不同基底(硅、碳化硅)的裸片集成。例如,英特尔Ponte Vecchio GPU整合47个Chiplet,结合台积电5nm与Intel 7工艺,实现算力密度翻倍。

4.降低研发门槛

通过复用已验证的Chiplet(如HBM内存、SerDes接口),开发者可规避复杂模块的设计风险,将资源集中于核心功能开发。

4、什么是先进封装?

半导体封装技术经历了从传统到先进的演进历程。传统封装始于三极管直插时代,其典型流程包括:将晶圆切割成裸片(Die),将裸片贴装在引线框架的小岛上,通过引线键合(Wire Bond)实现电气连接,最后进行塑封保护。这一时期的代表封装形式包括DIP、SOP、TSOP、QFP等。随着技术进步,先进封装技术应运而生,突破了传统封装的局限。这类技术主要包括倒装芯片(Flip Chip)、凸块(Bumping)、晶圆级封装(WLP)、2.5D封装(中介层、RDL等)以及3D封装(TSV)等。通过3D堆叠、系统级封装(SiP)等创新方法,先进封装实现了多芯片和功能模块在单一封装体内的高度集成。相较于传统引线键合技术,先进封装凭借高密度互连和异构集成等先进工艺,在系统集成度、尺寸微型化、能效比和性能表现等方面实现了质的飞跃。最初,先进封装仅有WLP、2.5D和3D封装等几种形式,但近年来呈现爆发式发展态势。各大厂商纷纷推出具有自主知识产权的技术方案,如台积电的InFO和CoWoS、日月光的FoCoS、Amkor的SLIM和SWIFT等。先进封装不仅是半导体制造工艺的重大突破,更从根本上重构了芯片设计范式。特别是在Chiplet技术兴起后,先进封装已成为延续摩尔定律的关键技术路径之一,为半导体行业的持续发展提供了新的动力。

5、先进封装的关键要素

1.晶圆(Wafer):先进封装的基石

晶圆作为半导体制造的基础载体,其质量直接影响最终芯片性能。现代先进封装中,晶圆不仅承担传统电路加工功能,更成为异质集成和多芯片封装的关键平台。随着制程进步,300mm大尺寸晶圆已成为主流,其对表面平整度和材料纯度的要求也日益严苛,特别是在3nm以下制程中,晶圆缺陷控制精度需达到原子级水平。

2.凸点(Bump):芯片互连的核心枢纽

作为芯片与封装基板间的关键连接桥梁,凸点技术经历了从锡铅合金到铜柱结构的演进。现代铜柱凸点具有以下优势:1.导电性提升30%以上2.机械强度增加50%3.环保合规性更优,在倒装芯片技术中,凸点间距已缩小至20μm以下,其排布密度直接影响封装的信号完整性、散热效率和机械可靠性。

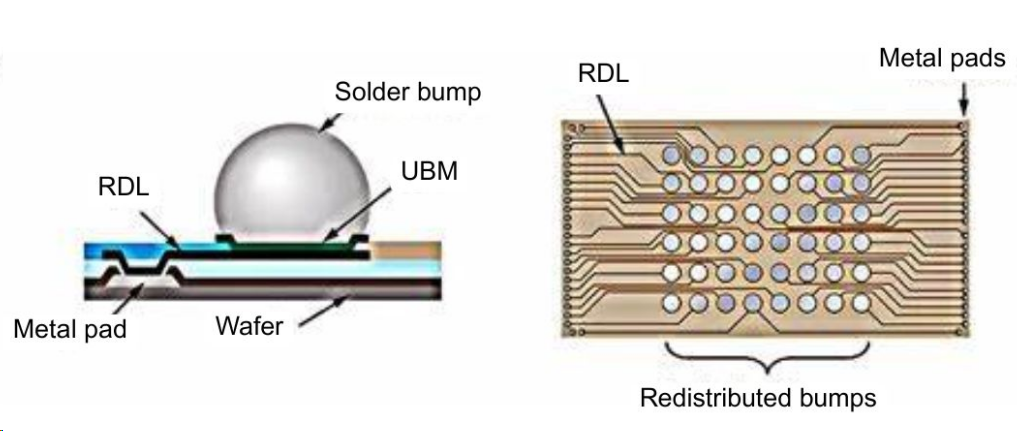

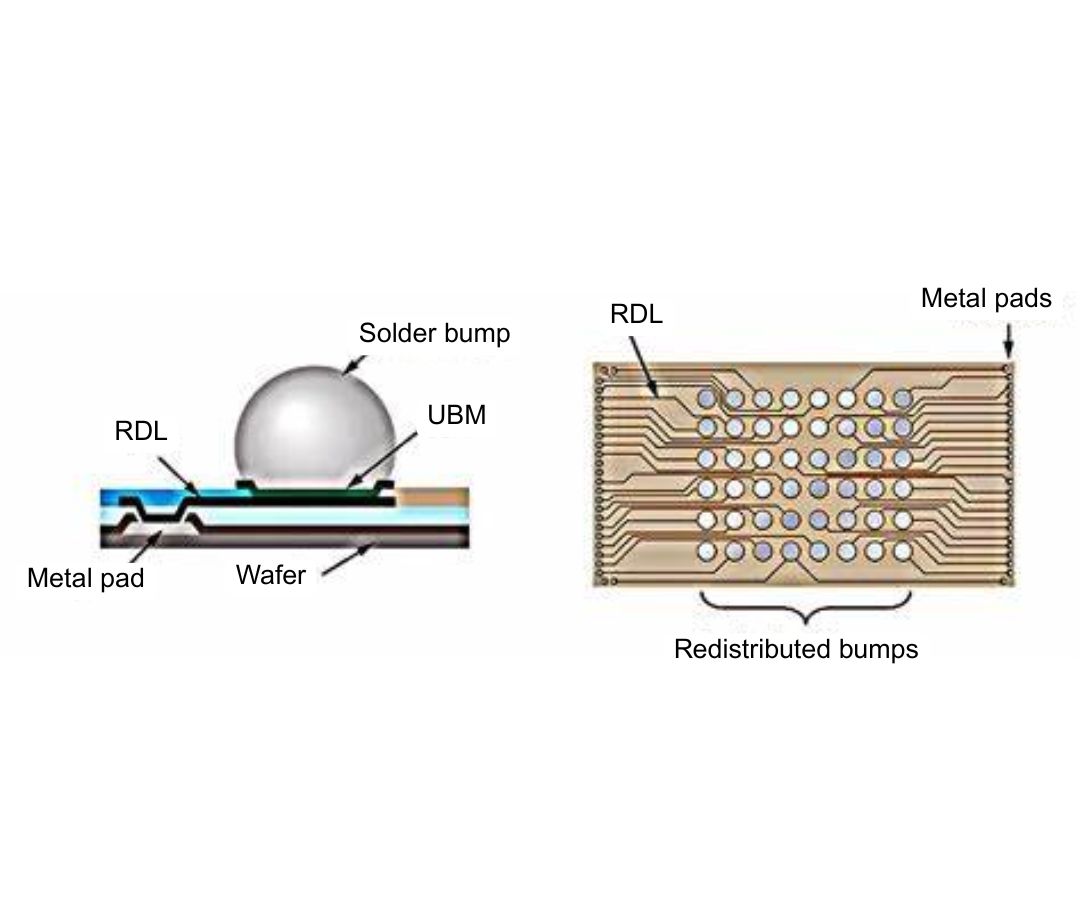

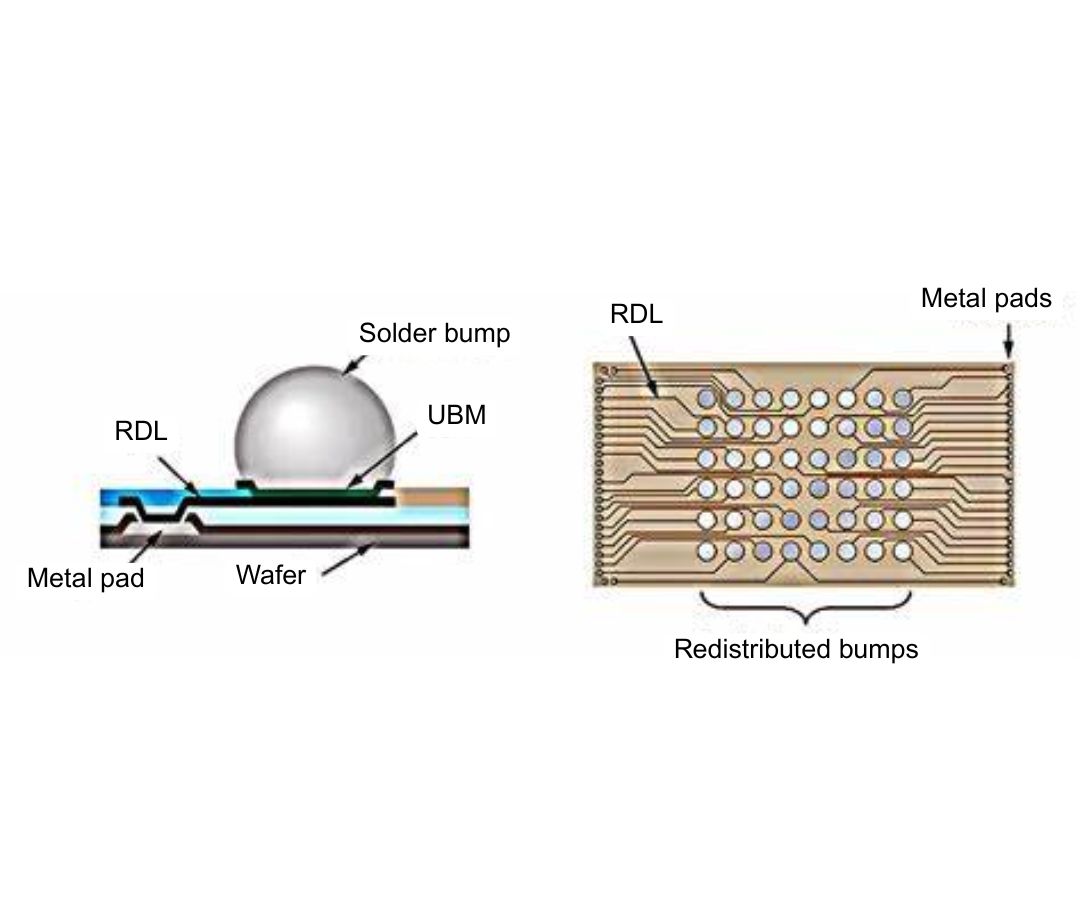

3.重布线层(RDL):信号优化的关键路径

RDL技术通过多层金属布线实现:I/O密度提升10倍以上,信号传输距离缩短40%,阻抗匹配精度提高60%,在扇出型封装中,RDL层数已发展至5层以上,线宽/线距达到2μm/2μm水平,有效支撑了高密度异质集成需求。

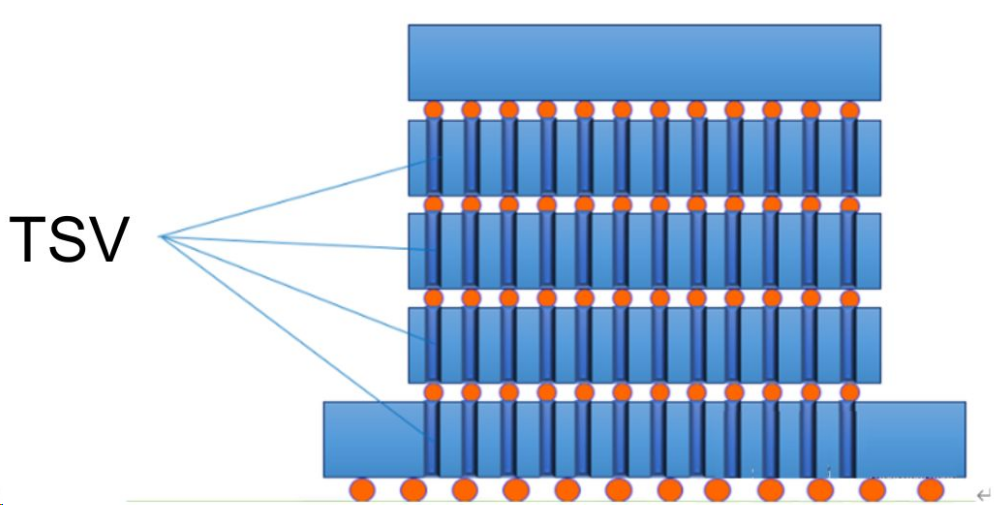

4.硅通孔(TSV):立体集成的技术突破

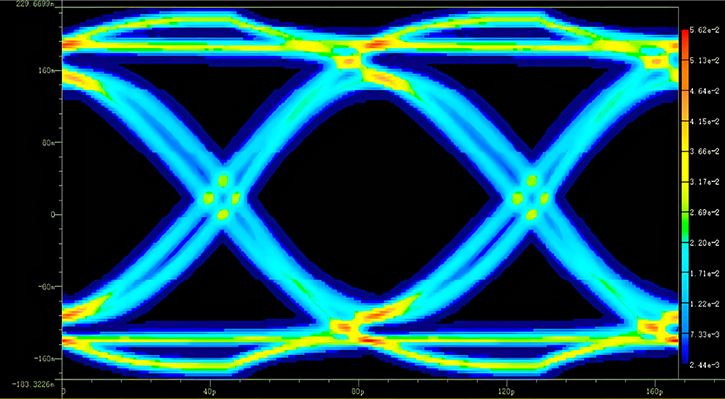

TSV技术的主要技术指标:深宽比突破10:1,导通电阻降低至毫欧级,信号延迟缩减至皮秒级,在3D IC应用中,TSV可实现超过10层的芯片堆叠,使互连密度达到传统封装的100倍,为高性能计算和AI芯片提供关键支撑。

这四大要素共同构成了先进封装的技术矩阵:晶圆提供制造基础,凸点实现可靠互连,RDL优化信号分布,TSV突破空间限制。

它们的协同创新推动着封装技术从平面集成向立体系统级集成的跨越式发展,为后摩尔时代的芯片性能提升开辟了新路径。当前最先进的封装方案已能实现单封装集成超过1000亿晶体管,信号传输带宽突破TB/s级,这些突破都依赖于这四大核心技术的持续演进。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

Recommended

-

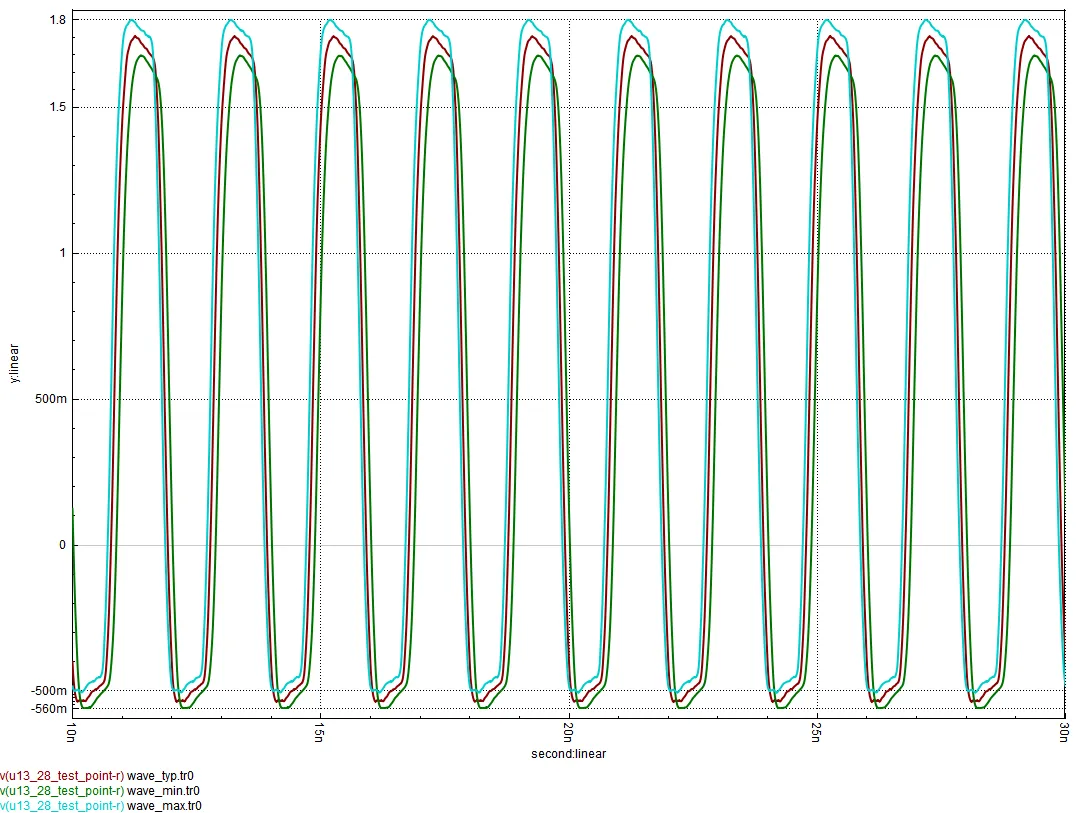

Process Corners and Applications in IBIS Modeling2025.04.23

Process Corners and Applications in IBIS Modeling2025.04.23 -

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (II)2025.04.21

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (II)2025.04.21 -

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (I)2025.04.11

Technical Synergy of Chiplet and Advanced Packaging and Challenges for EDA Simulation Tools (I)2025.04.11 -

PAM3 Encoding and Simulating Verification in High-Speed Transmission2025.03.31

PAM3 Encoding and Simulating Verification in High-Speed Transmission2025.03.31