PCIe 6.0 介绍与仿真应用

-

2025.03.20

引言:自2003年PCIe 1.0规范发布以来,PCI Express(PCIe)已成为计算、存储和通信领域最核心的高速互连标准。随着AI、5G、超算和数据中心对带宽需求的爆炸式增长,PCIe 6.0于2022年正式发布,将单通道速率提升至64 GT/s(Giga Transfers per second),较PCIe 5.0翻倍,同时引入多项革命性技术。本文将从技术架构、核心升级、应用场景三个维度,深度解析PCIe 6.0如何重塑数据互连生态。

一、PCIe 6.0的四大技术突破

1、PAM4调制:从NRZ到多电平信号的跨越

PCIe 6.0首次采用**PAM4(4-Level Pulse Amplitude Modulation)**编码,取代前几代的NRZ(Non-Return-to-Zero)技术。

· 原理:NRZ每个周期传输1 bit(0或1),而PAM4通过4个电平(-3, -1, +1, +3)编码2 bit信息,单位时间传输密度翻倍。

· 优势:在相同频率下,PAM4将有效带宽提升至64 GT/s(x16通道可达256 GB/s),同时减少信号路径的物理层复杂度。

· 挑战:PAM4的信噪比(SNR)要求更高,需配合均衡器(EQ)和前向纠错(FEC)技术实现可靠传输。

2、FLIT 模式:数据包传输的范式革新

PCIe 6.0引入FLIT(Flow Control Unit)模式,彻底重构数据链路层。

· 传统TLP模式:基于可变长度数据包(TLP),需复杂的流量控制和重传机制。

· FLIT模式:采用固定长度(256B)数据块,支持批量传输和硬件级CRC校验,显著降低延迟(<10 ns)和协议开销。

· 兼容性:FLIT与TLP模式可动态切换,确保与旧版本设备的互操作性。

3、前向纠错(FEC):为PAM4保驾护航

为应对PAM4的高误码率(BER),PCIe 6.0首次集成轻量级FEC(Forward Error Correction)。

· 机制:基于CRC和汉明码(Hamming Code),实时检测并纠正传输错误。

· 效率:FEC纠错延迟仅增加2-3 ns,对系统级性能影响可忽略。

· 场景适配:FEC可动态启用,在短距离(如芯片内互连)或低噪声环境中可关闭以节省功耗。

4、低功耗设计:能效比提升50%

PCIe 6.0通过以下优化实现能效跃升:

· L0p/L1.2电源状态:快速进入/退出低功耗模式,空闲时功耗降低80%。

· 自适应均衡:根据信道质量动态调整EQ强度,减少无效功耗。

· 工艺支持:兼容5nm及以下先进制程,降低PHY层功耗。

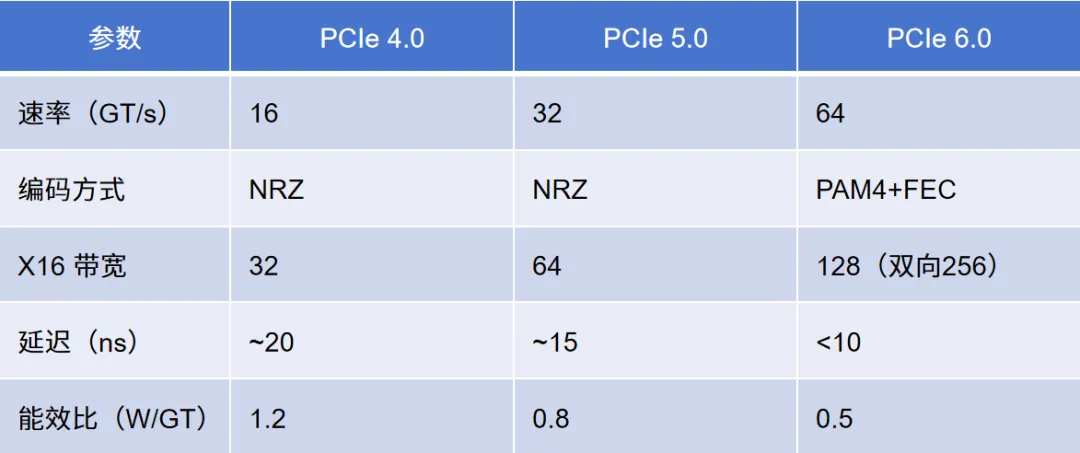

二、PCIe 6.0与前代技术的关键对比

三、PCIe 6.0的三大应用场景

1、人工智能与超算

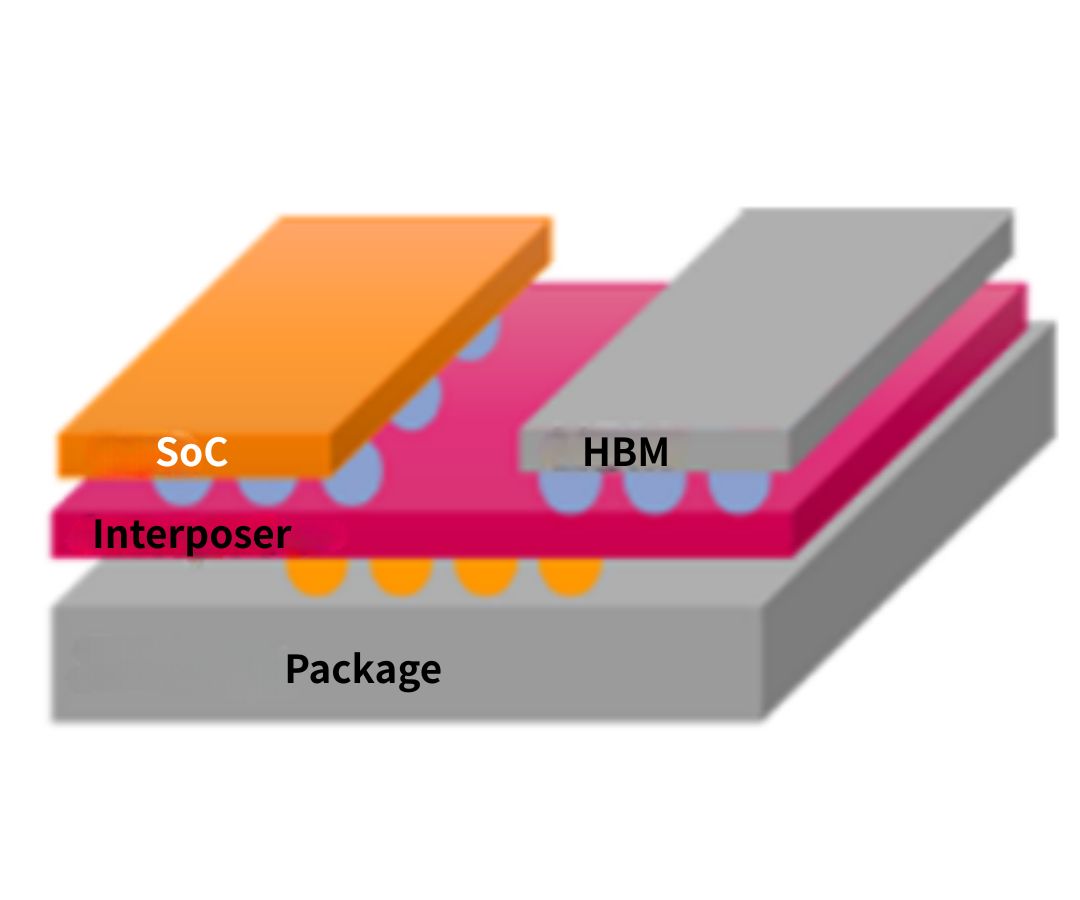

· GPU/TPU集群:PCIe 6.0 x16提供256 GB/s双向带宽,满足多GPU间参数同步需求(如NVIDIA NVLink替代方案)。

· 近存计算:通过CXL 3.0协议,支持GPU直接访问分布式内存池,突破“内存墙”瓶颈。

2、数据中心与云存储

· 全闪存阵列(AFA):PCIe 6.0 SSD(如三星PM1751)可提供28 GB/s持续读写速度,比PCIe 5.0 SSD快2倍。

· 分解式存储:通过NVMe over Fabrics(NVMe-oF)实现跨节点存储资源池化,延迟低于1μs。

3、5G与边缘计算

· 基站前传:PCIe 6.0用于CPRI/eCPRI接口,支持毫米波 Massive MIMO 的实时信号处理。

· 边缘AI推理:在车载计算平台(如NVIDIA DRIVE Thor)中,PCIe 6.0连接多传感器与中央处理器,实现低延迟决策。

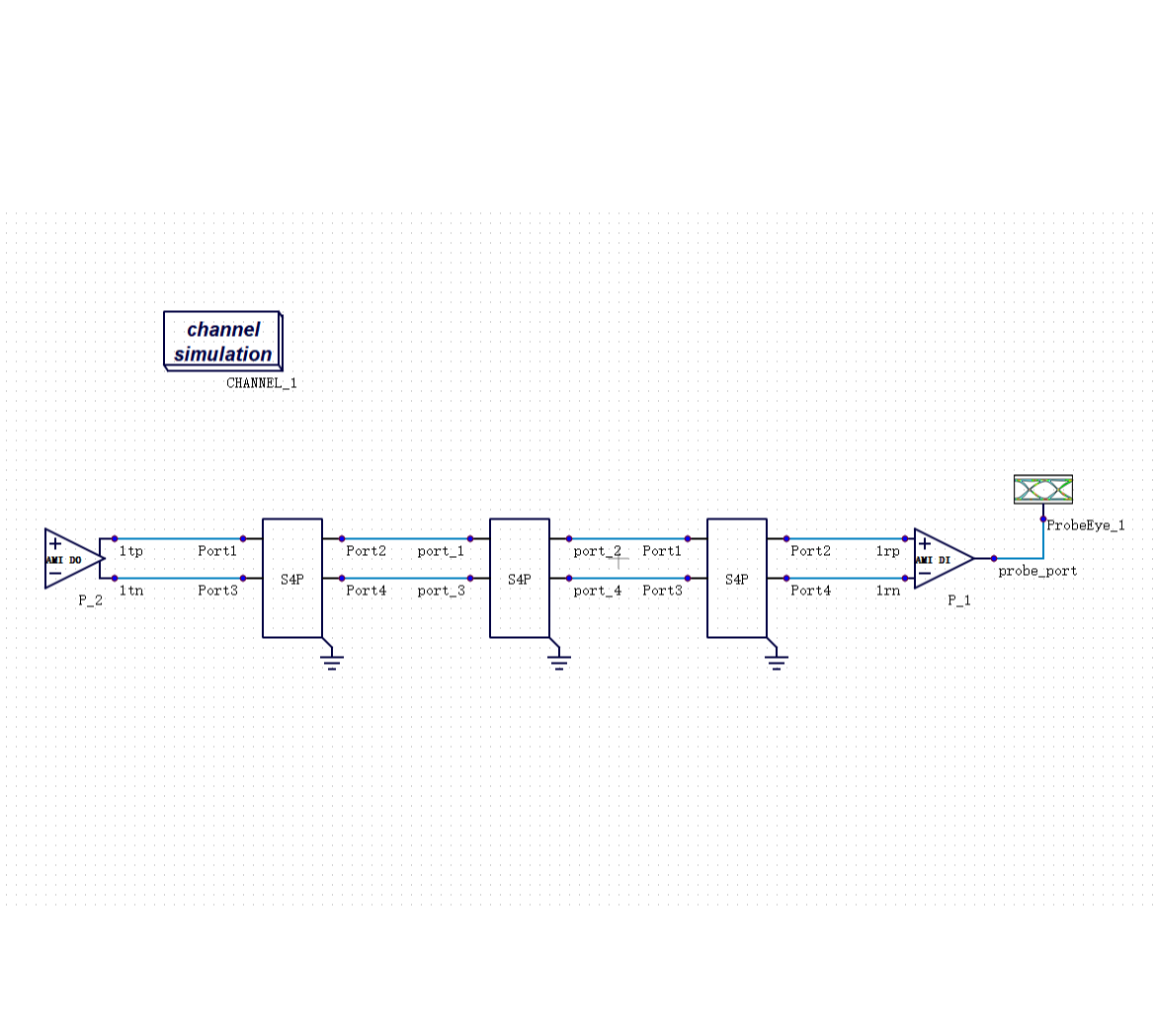

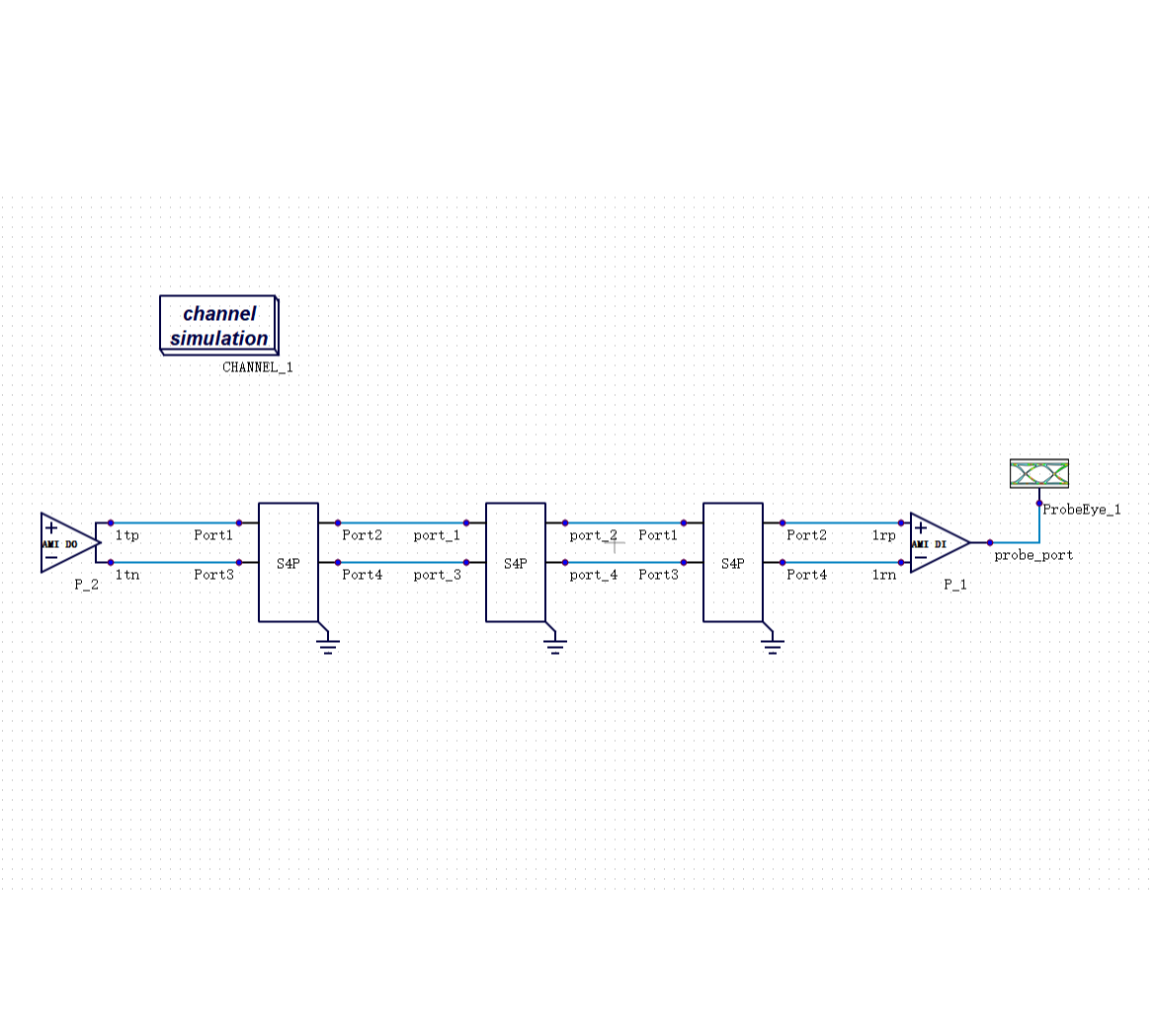

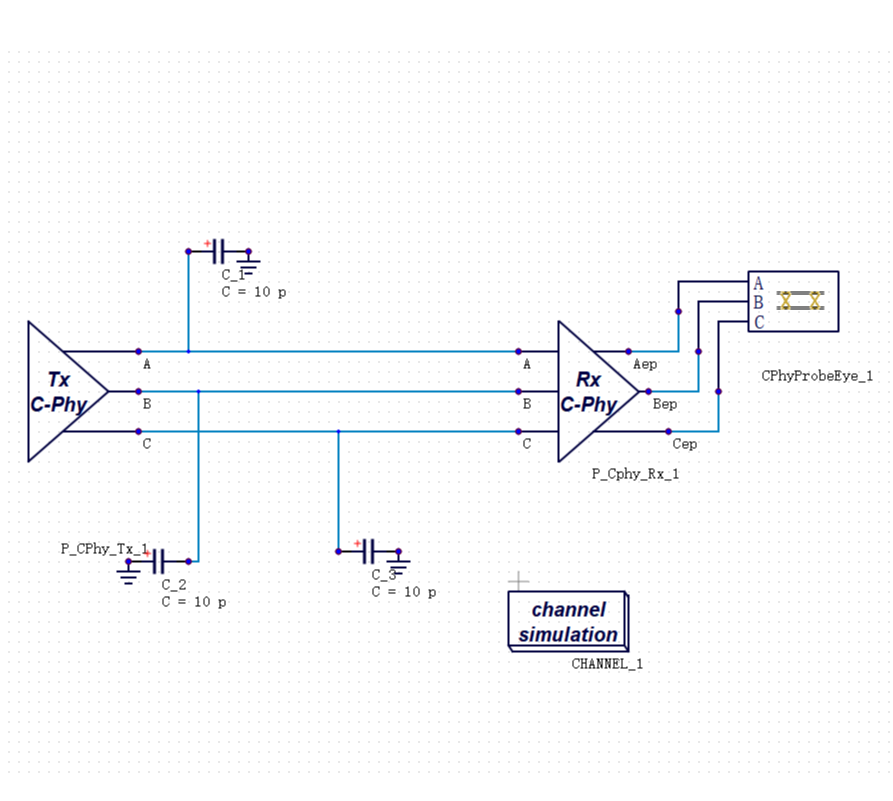

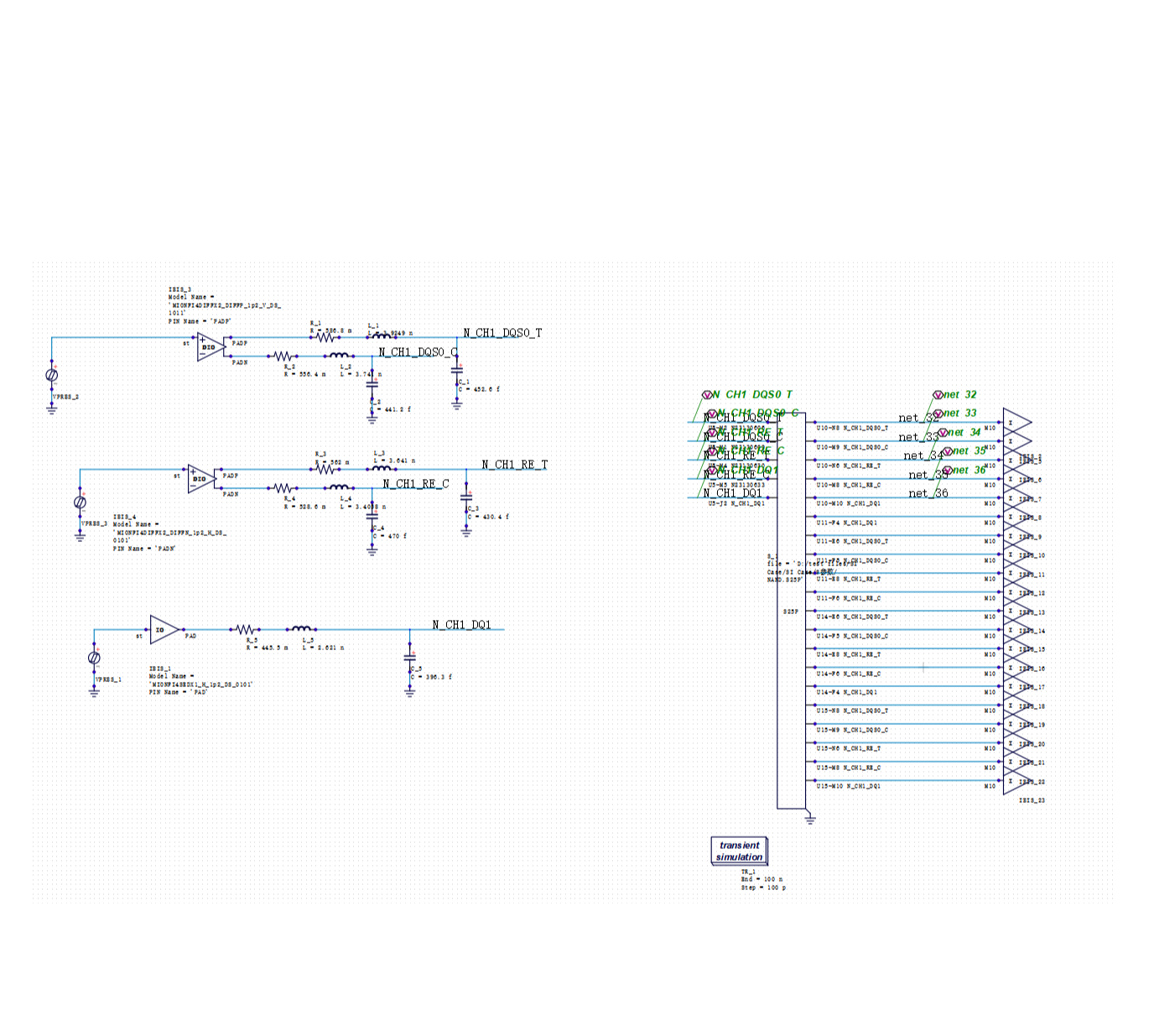

四、使用SIDesigner进行仿真

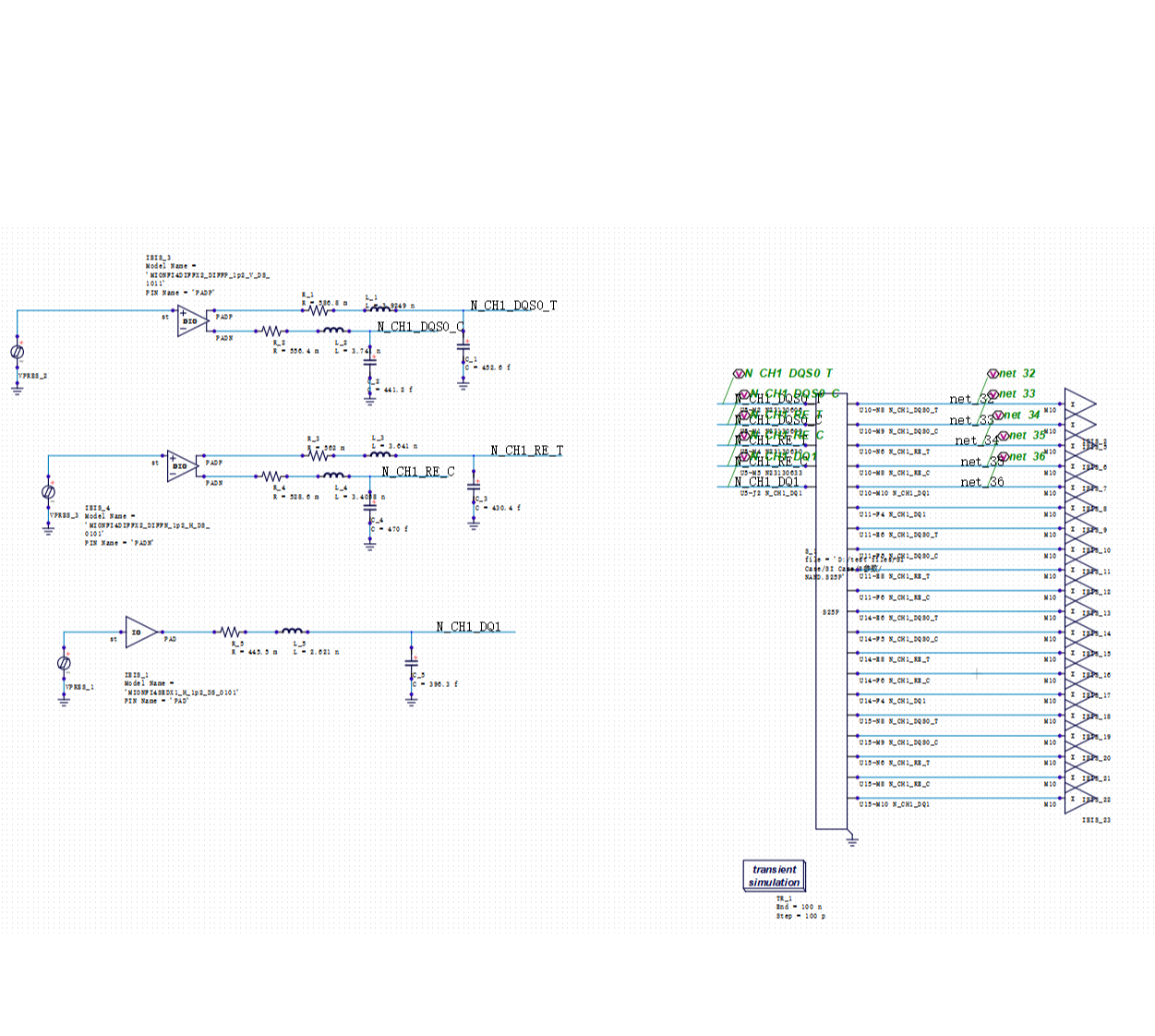

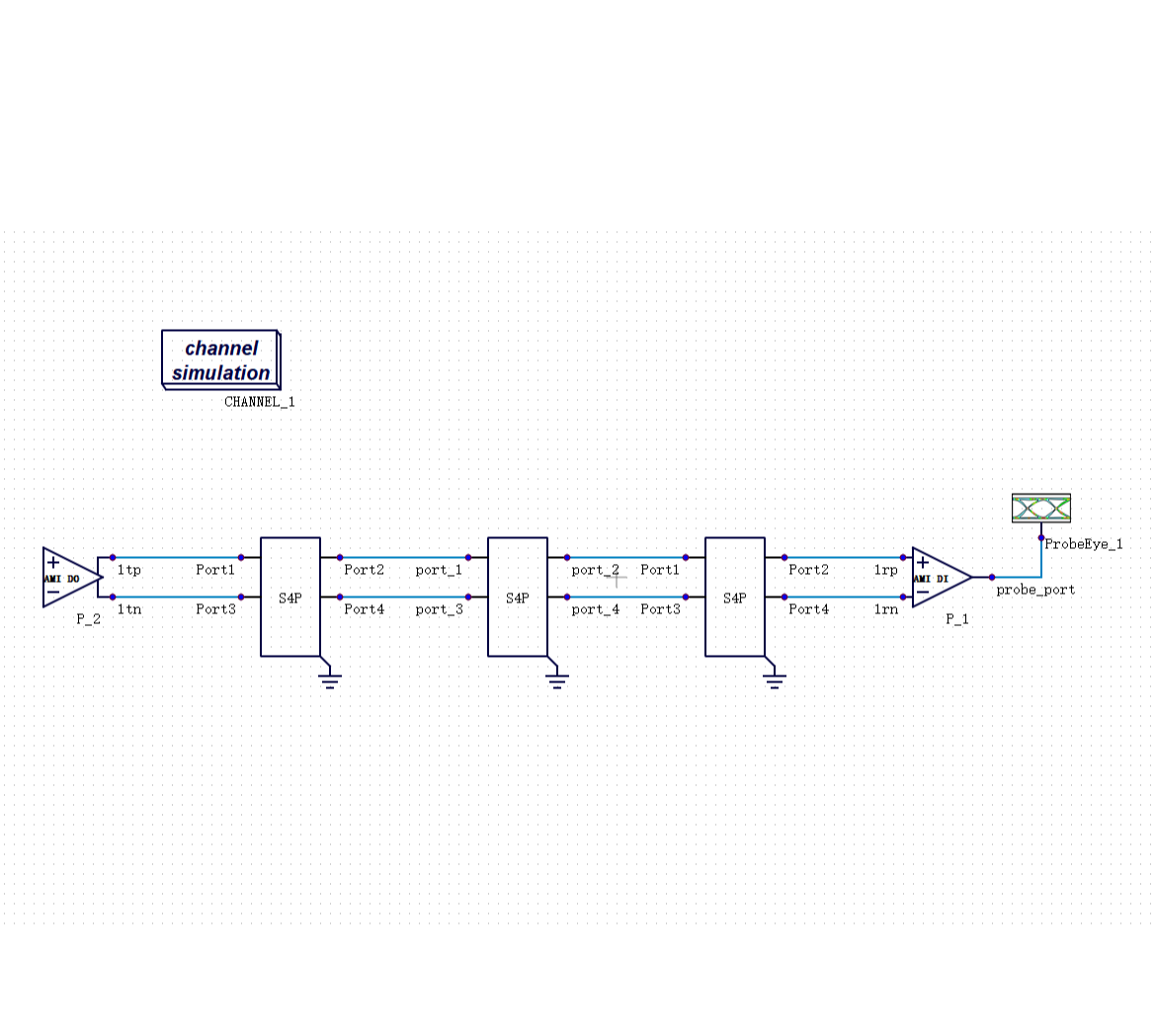

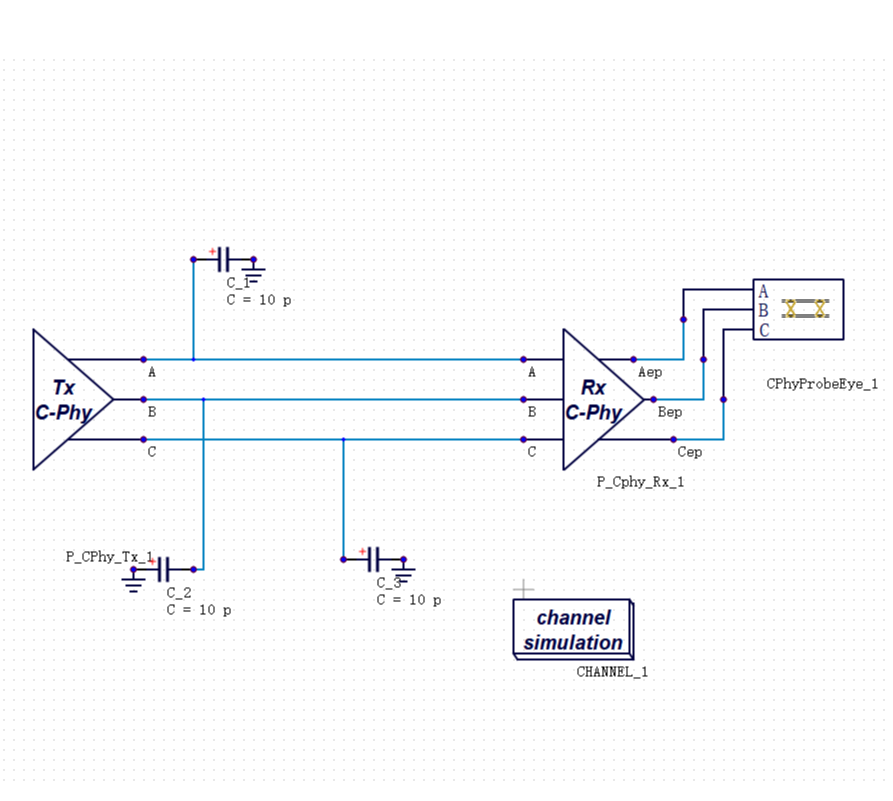

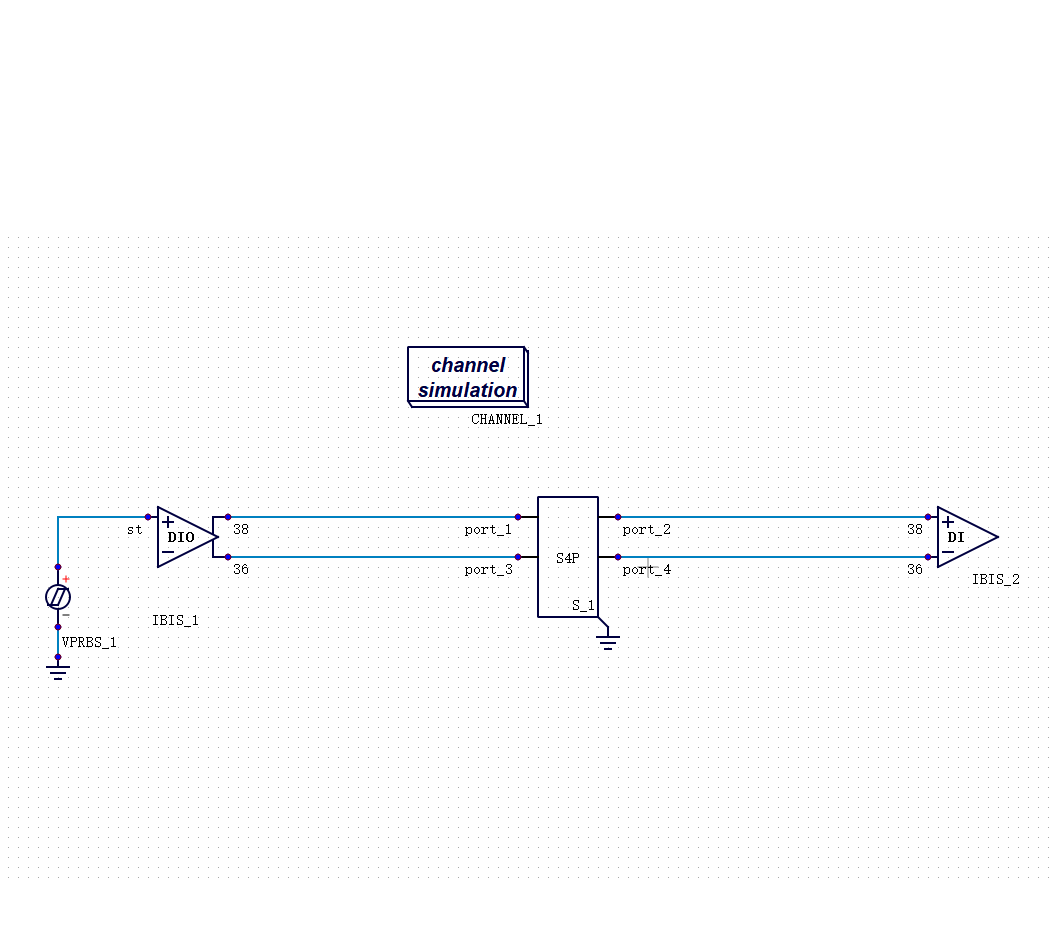

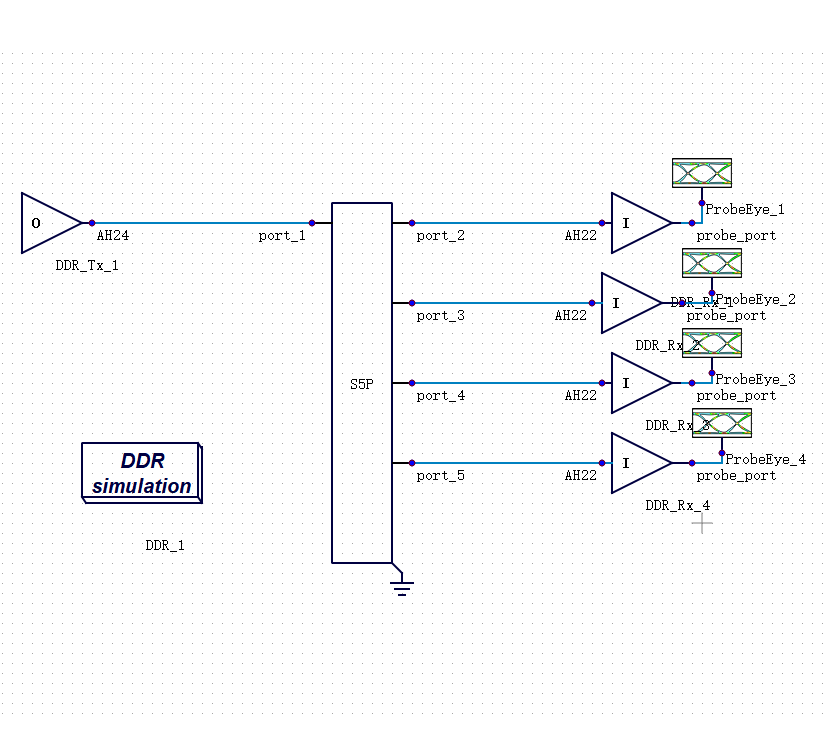

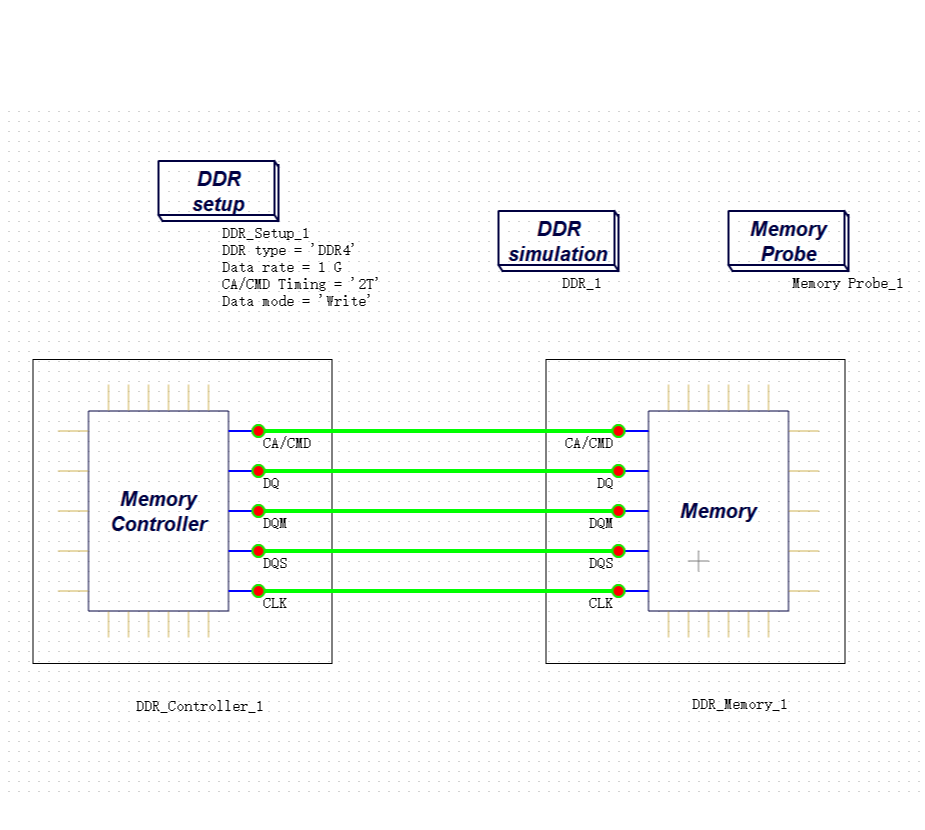

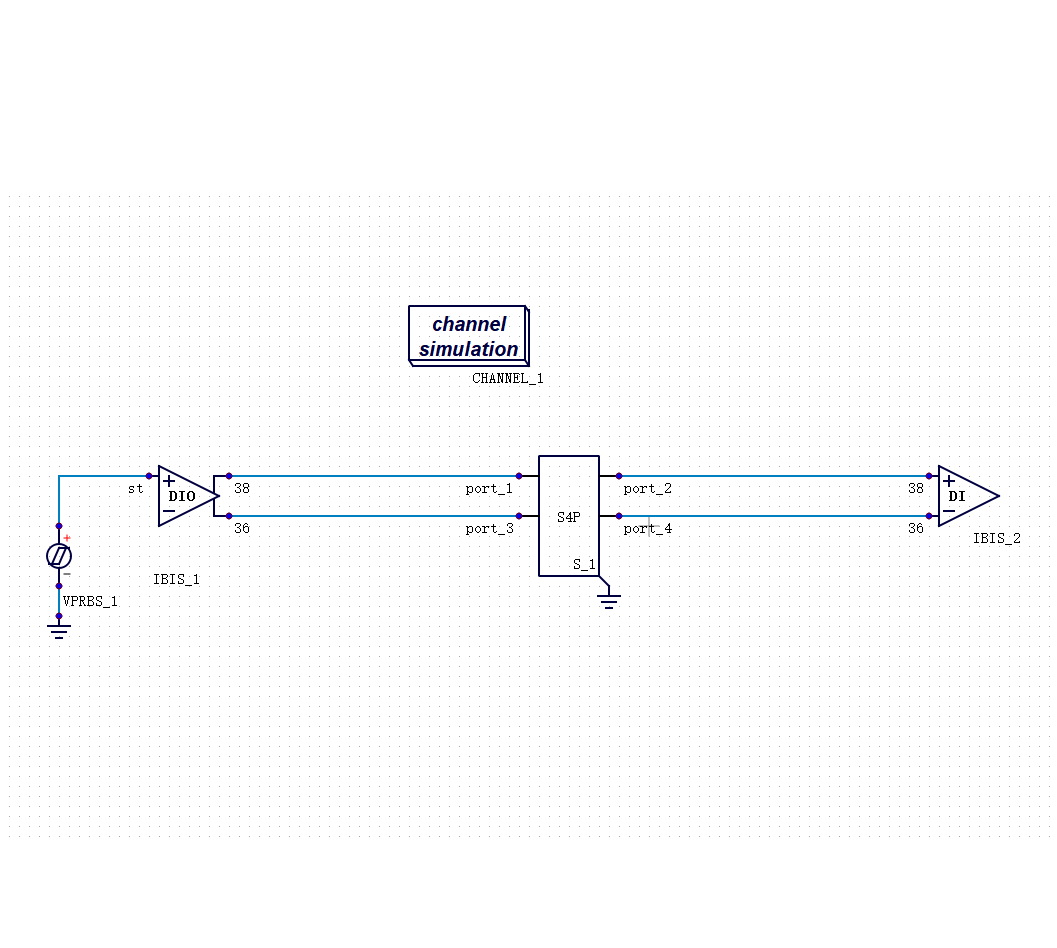

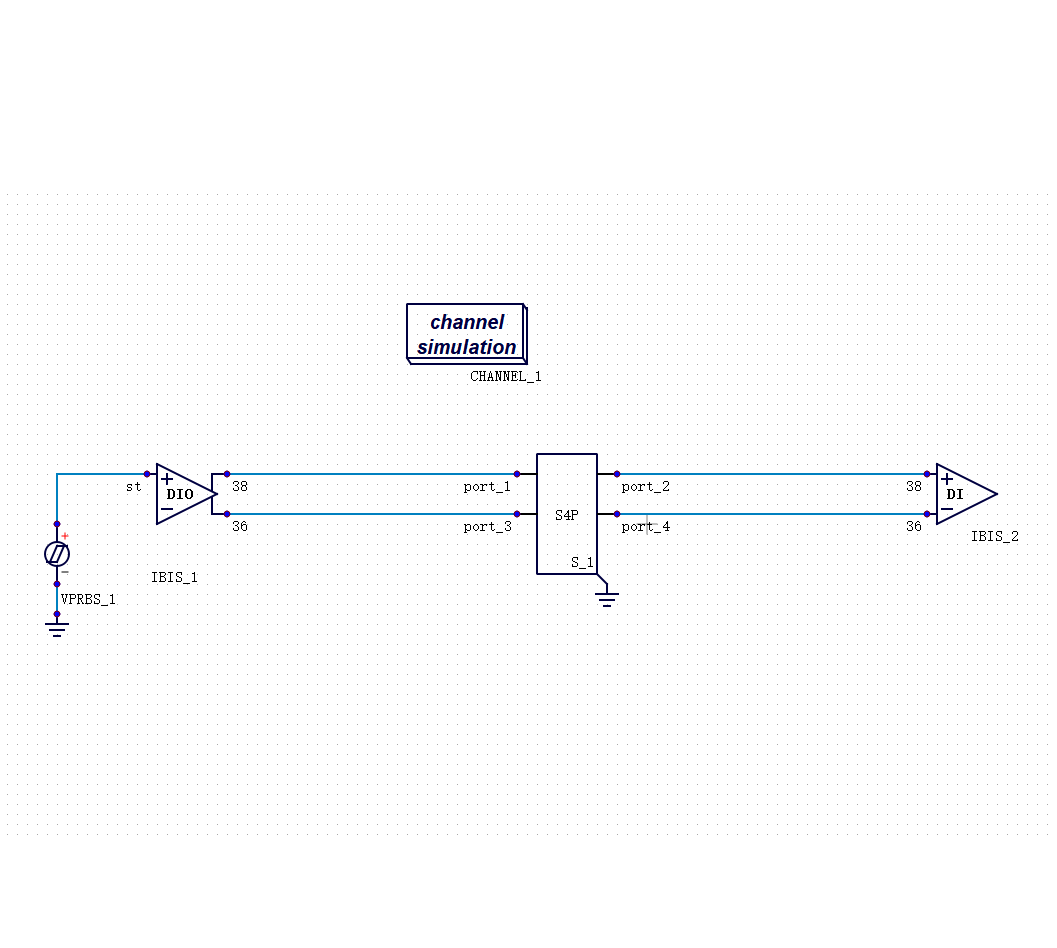

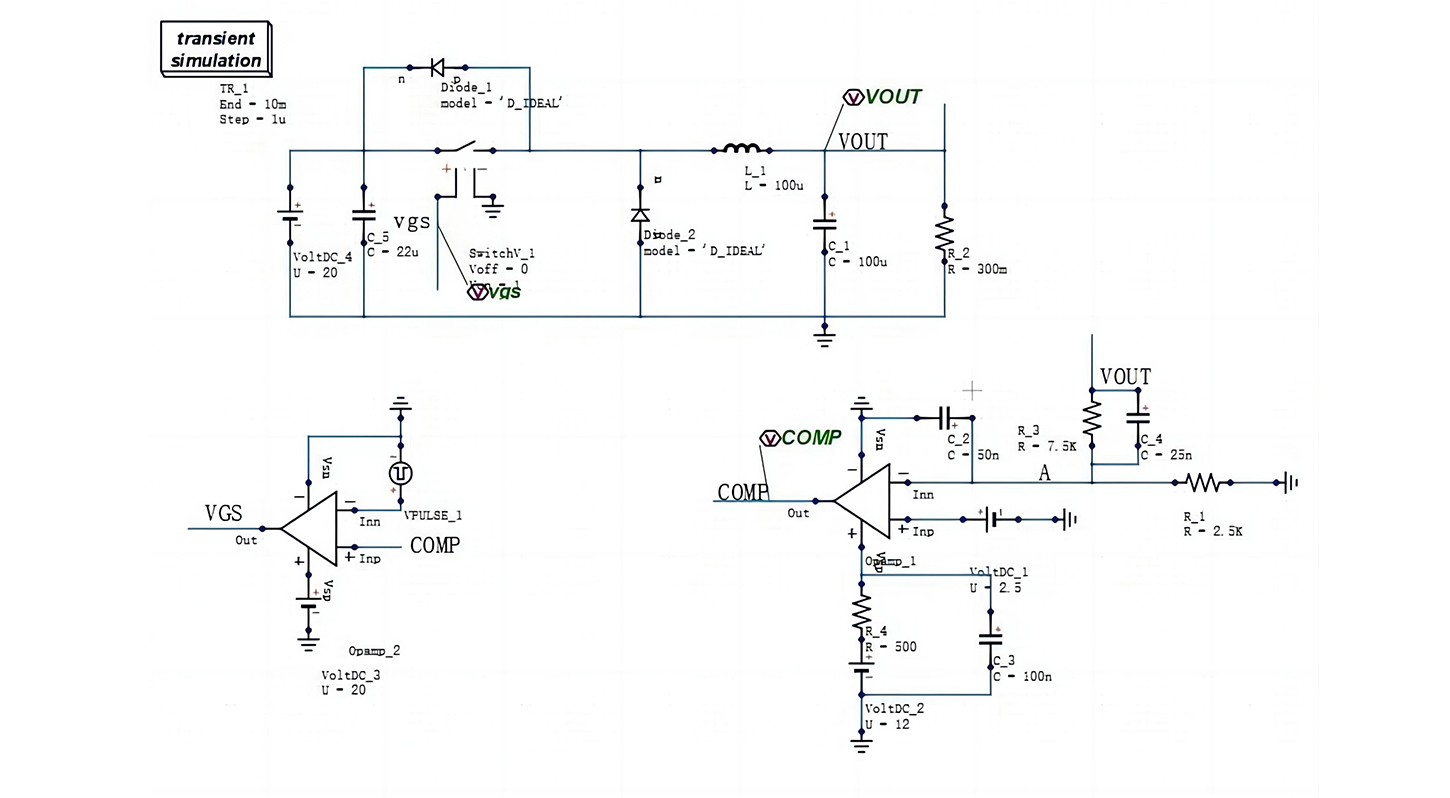

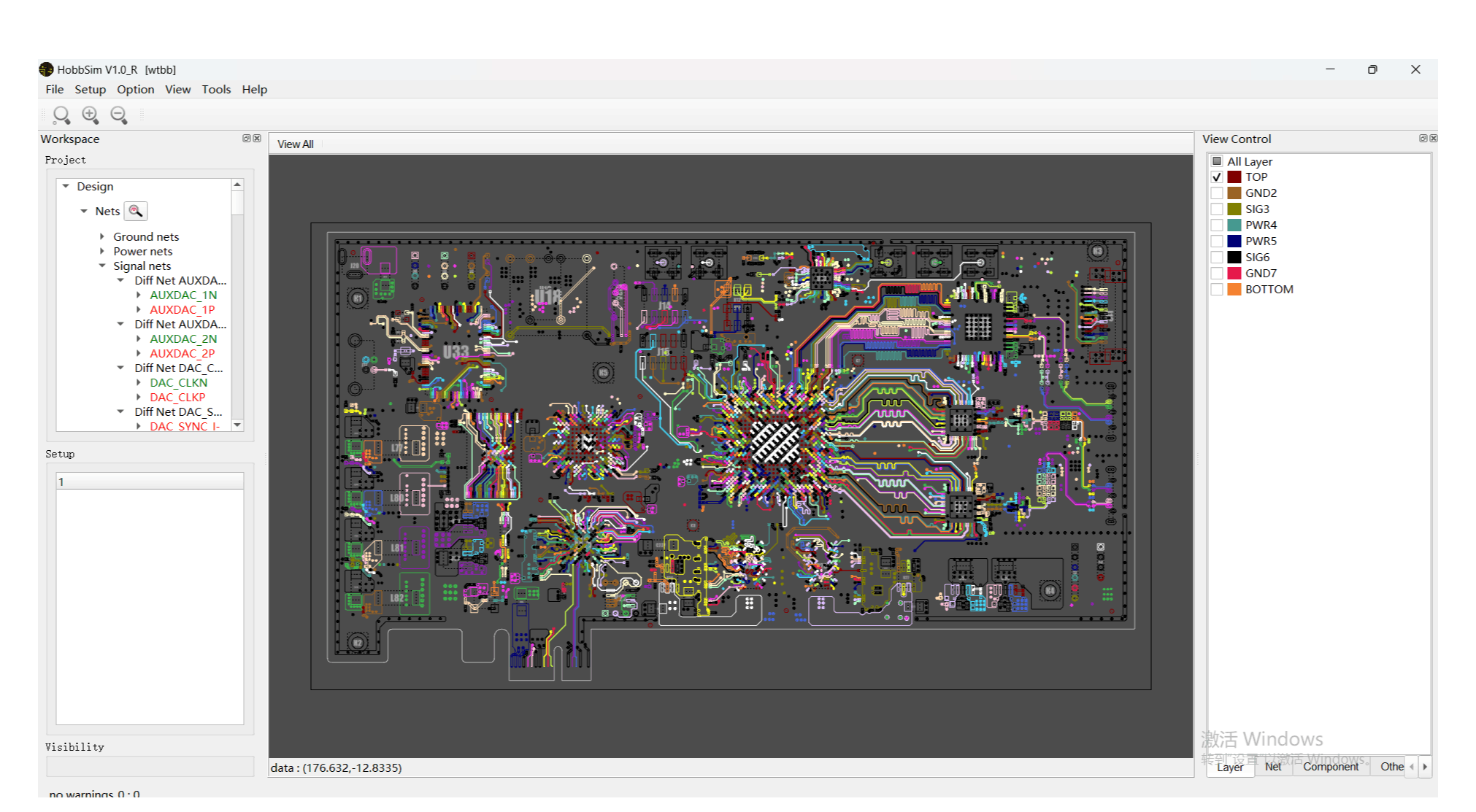

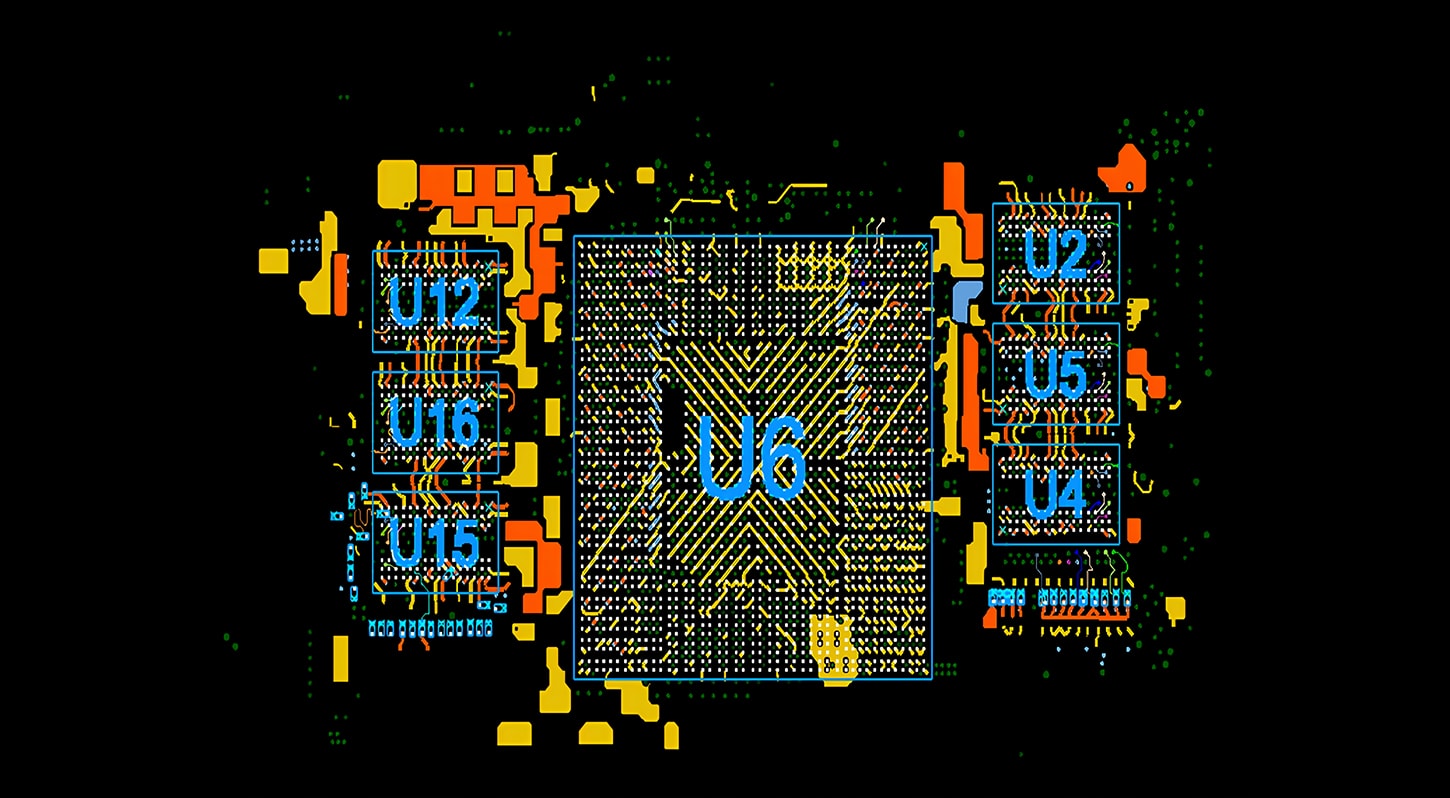

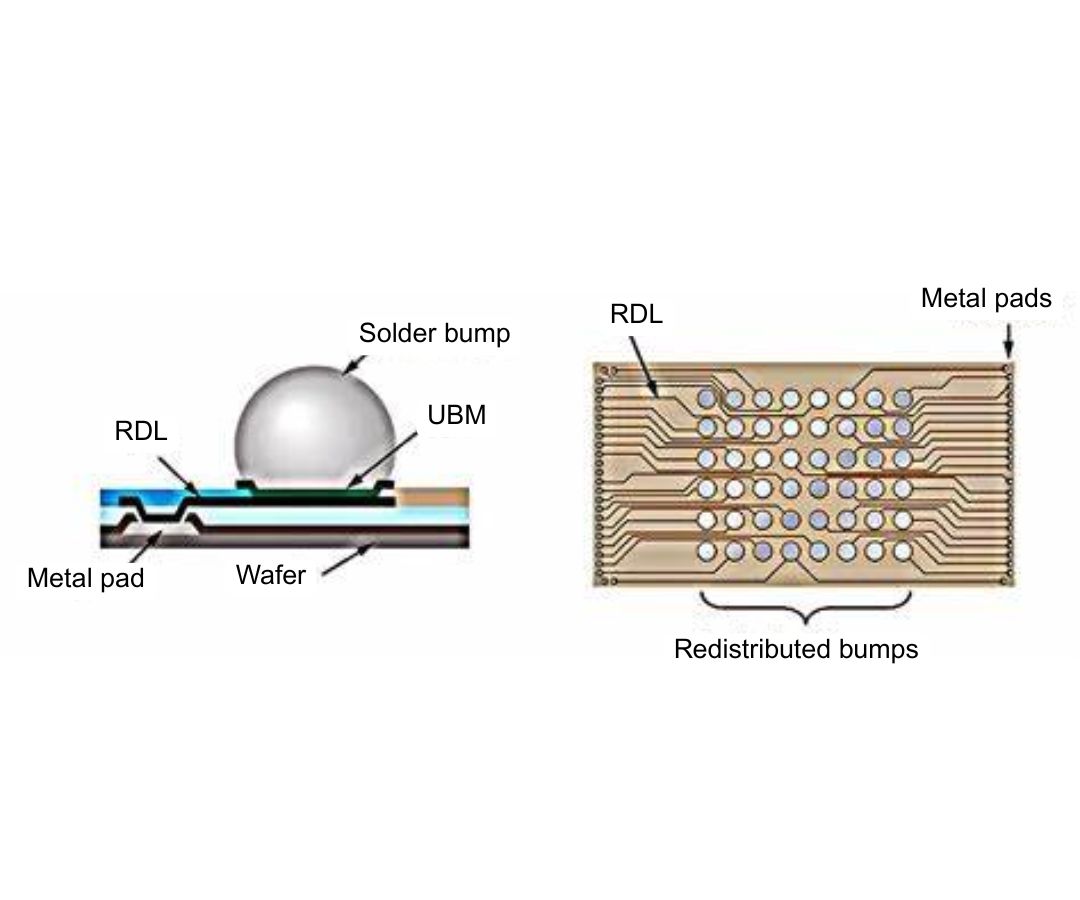

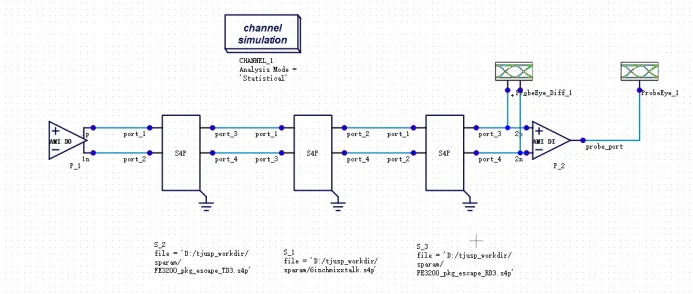

使用巨霖仿真软件SIDesigner搭建PCIe 6.0的仿真电路,原理图如下:

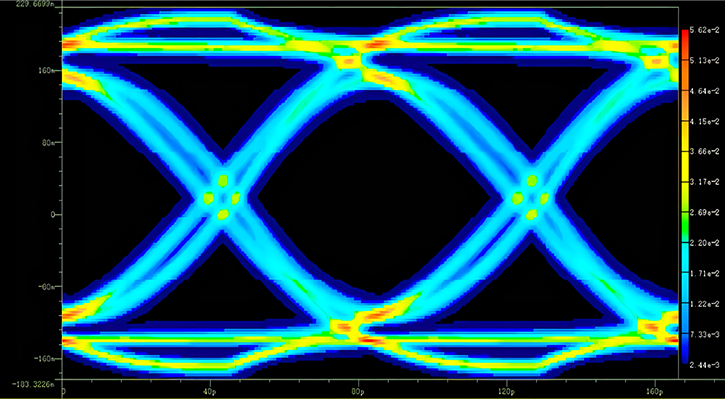

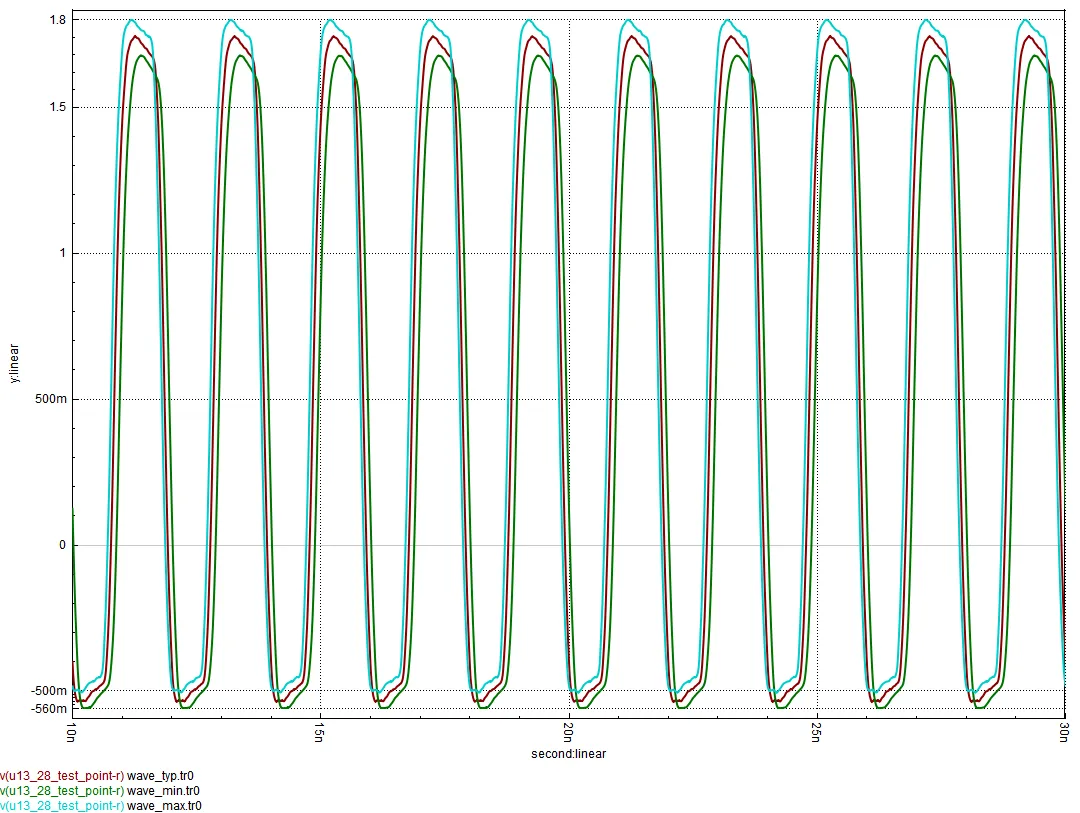

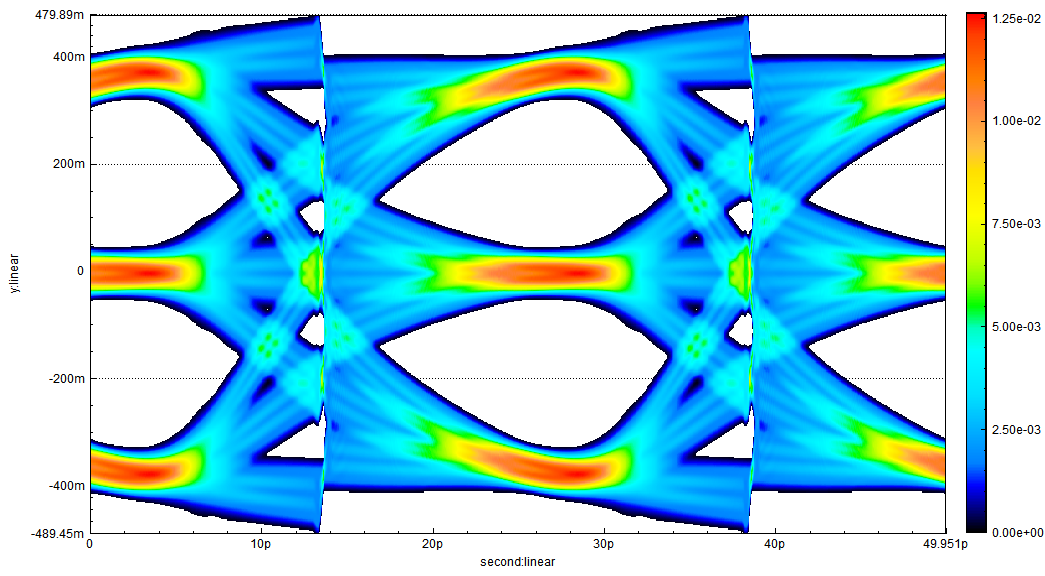

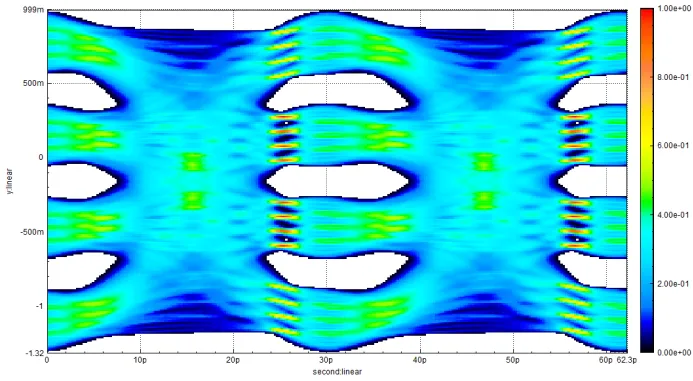

仿真结果如下:

工程师可以对电子系统进行全面的系统性能评估、优化系统可靠性及稳定性,加速产品研发、迭代过程。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!