Chiplet与先进封装的技术协同及EDA仿真工具面临的挑战 (二)

-

2025.04.18

一、Chiplet与先进封装的结合

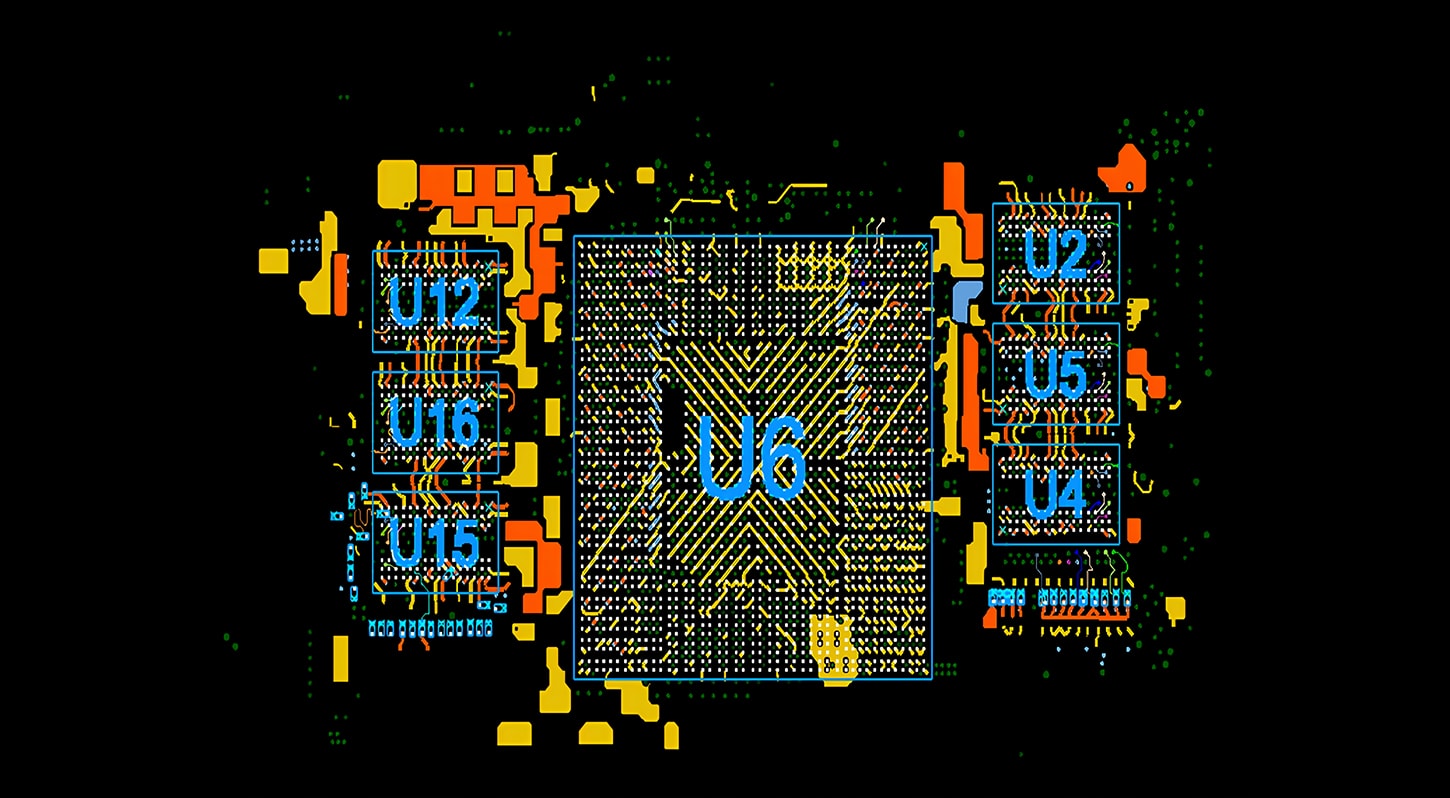

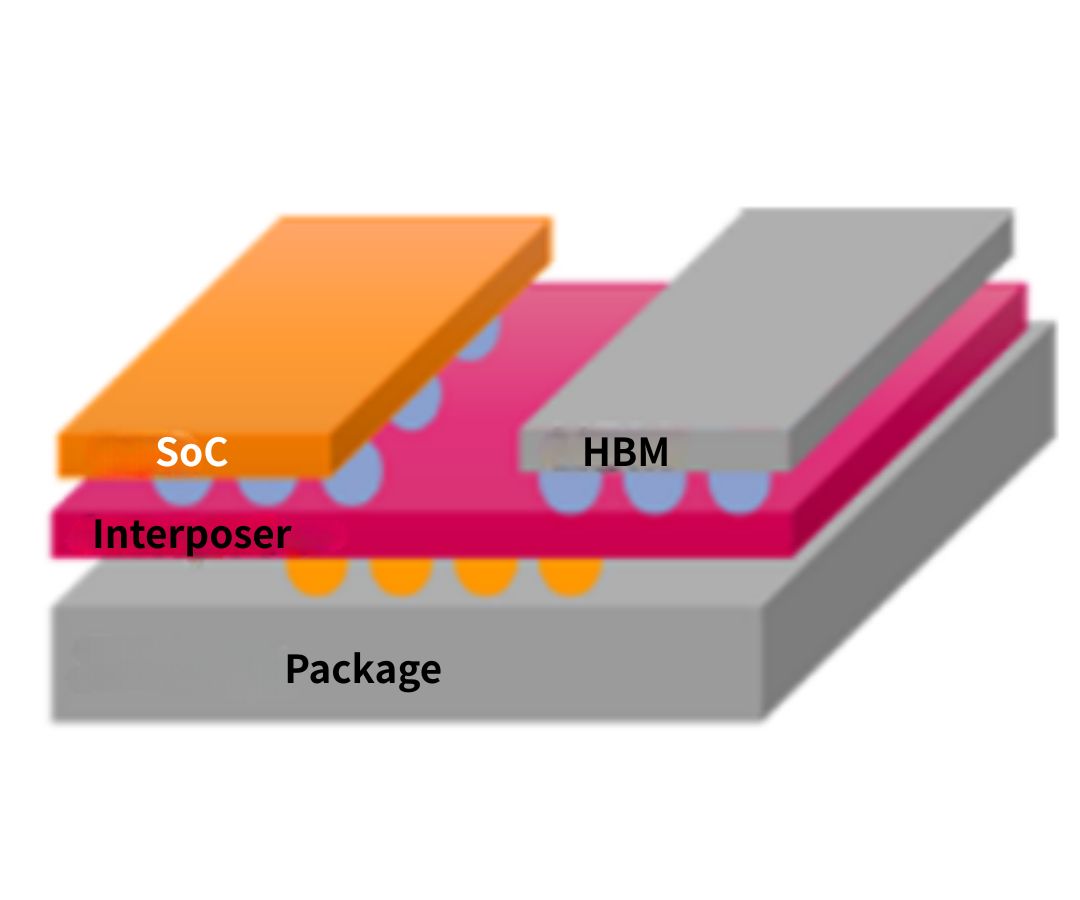

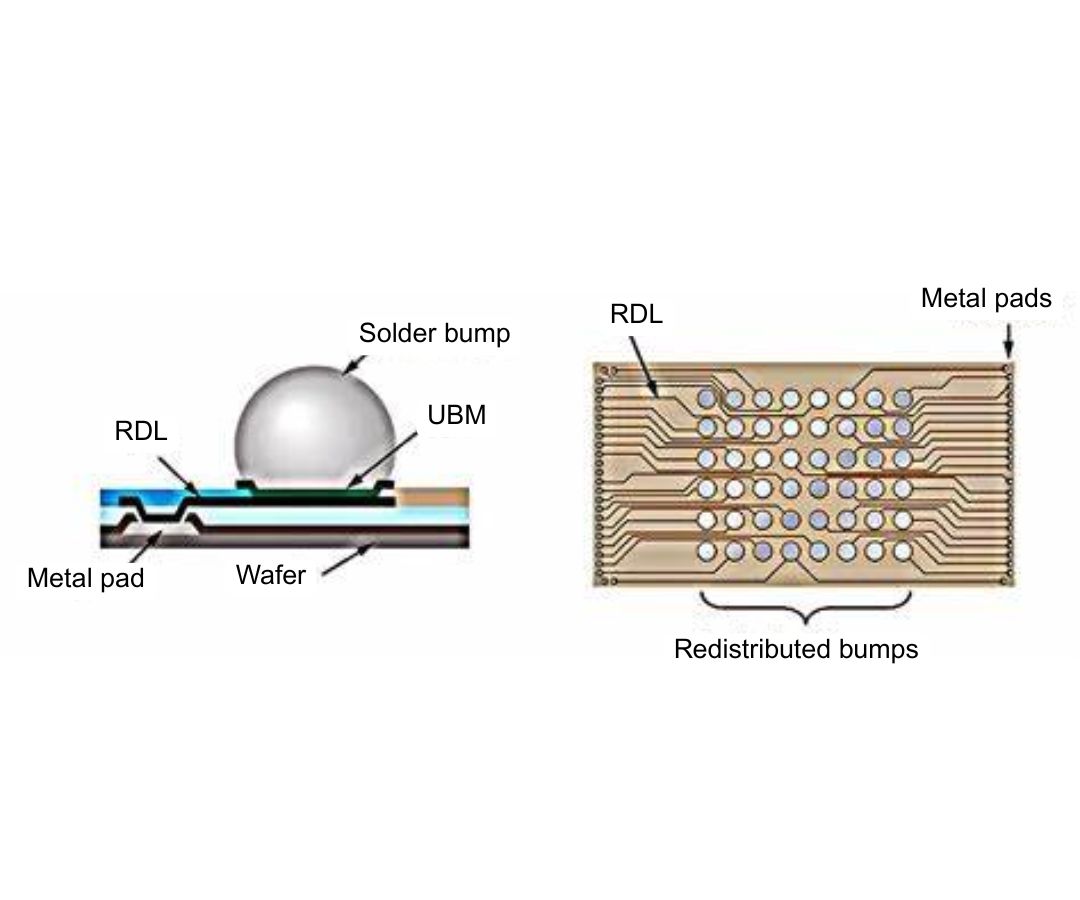

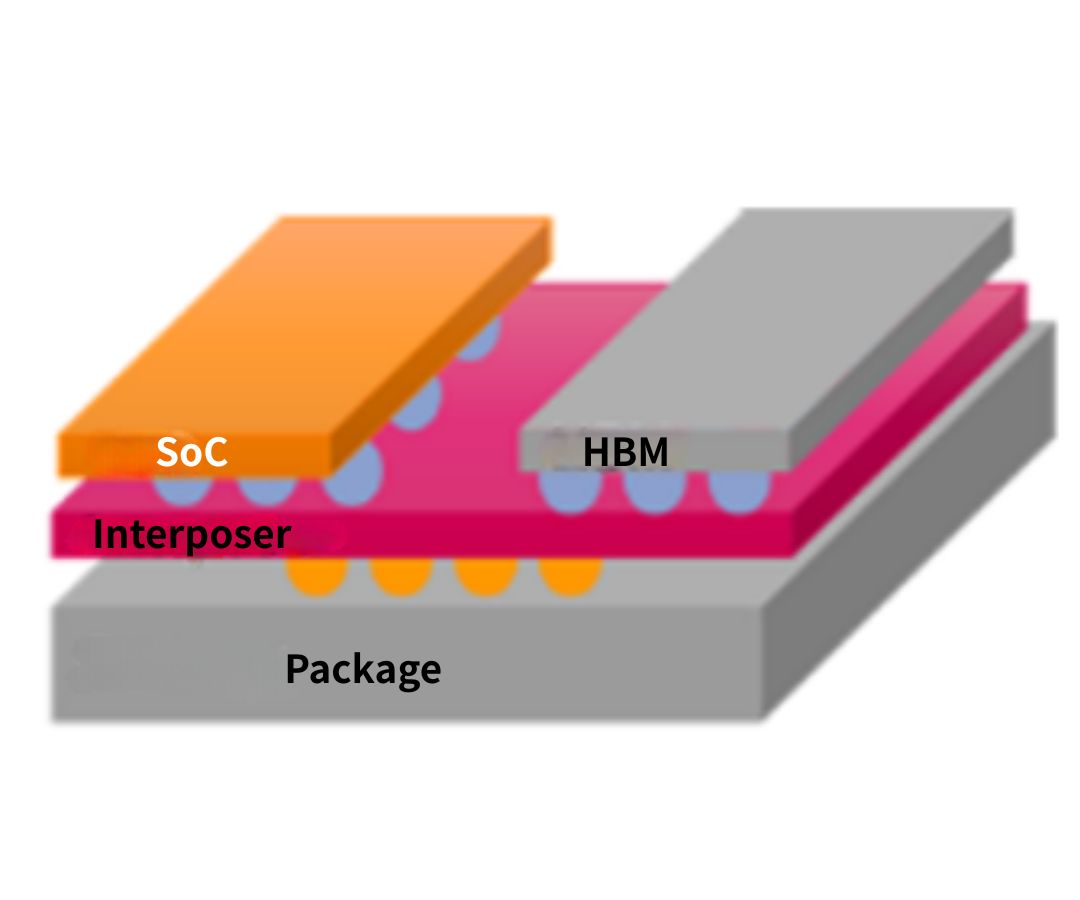

Chiplet和先进封装通常是互为补充的。Chiplet技术使得复杂芯片可以通过多个相对较小的模块来实现,而先进封装则提供了一种高效的方式来将这些模块集成到一个封装中。通过这种组合,设计师可以在不需要完全重新设计每个组件的情况下,轻松地实现芯片的定制化、升级以及性能优化。例如,某些应用可能需要特定的高带宽内存(HBM)或专用加速器(如AI加速器),这些可以作为独立的Chiplet与主处理器Chiplet共同组成系统。在封装级别,设计者使用先进封装技术,将这些Chiplet通过高密度互联(如微凸点、硅通孔、封装内光互联等)连接起来,从而优化整体性能、带宽和功耗。

二、EDA工具面临的挑战

随着Chiplet和先进封装技术的广泛应用,EDA工具在设计、验证、优化这些新型结构时面临着一系列挑战。

1、设计复杂性增加

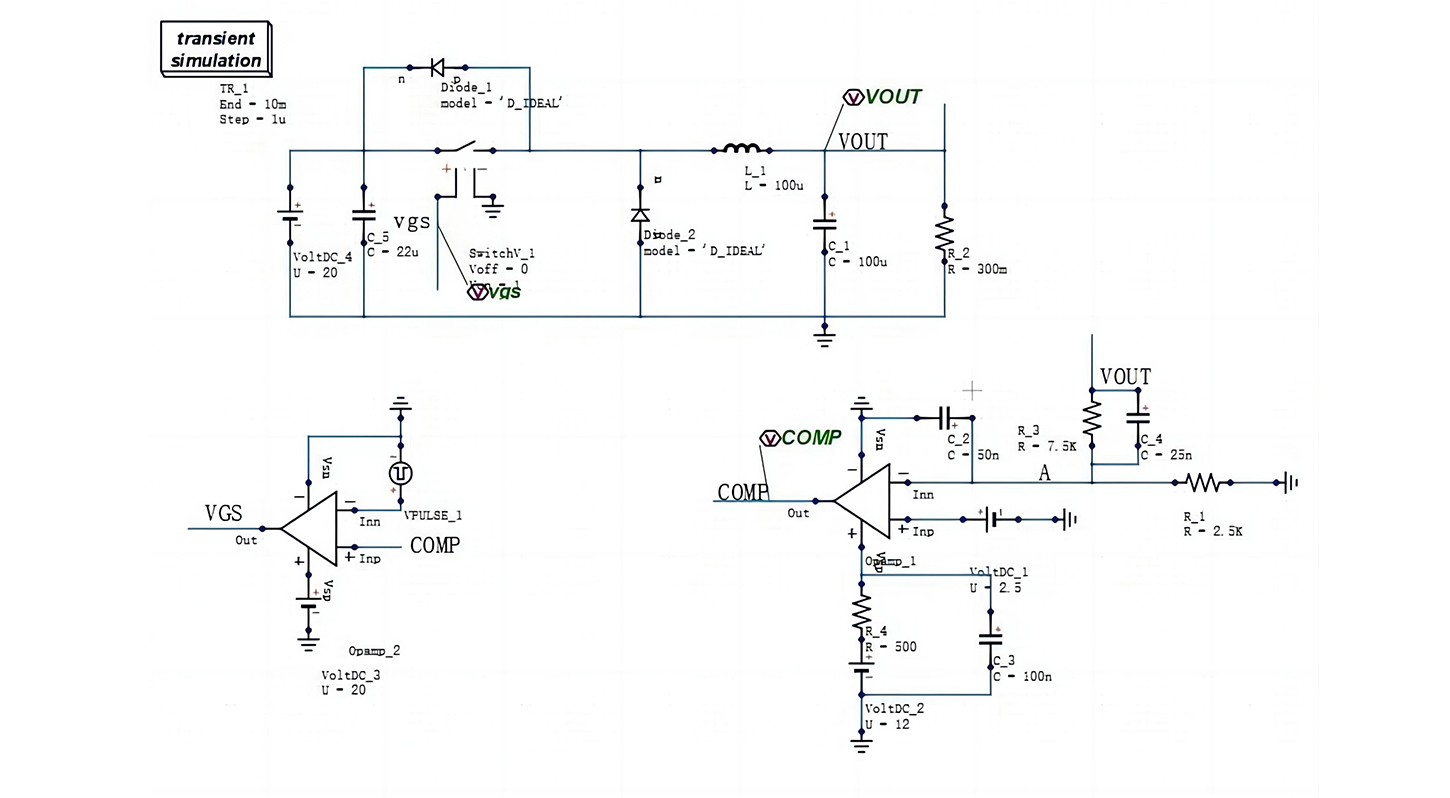

Chiplet和先进封装设计的一个显著特点是其设计复杂性的大幅提升。每个Chiplet内部都有独立的电路设计和功能,设计者需要考虑如何将这些独立的模块组合起来,以实现最佳的性能和功耗。与此同时,封装层面的设计(包括互连、散热、信号完整性等)也增加了额外的挑战。EDA工具需要支持这种多层次的、跨模块的设计过程,而不仅仅是单一的芯片设计。这就需要EDA工具支持多物理场协同仿真,需同时分析电、热、力(应力)耦合效应。

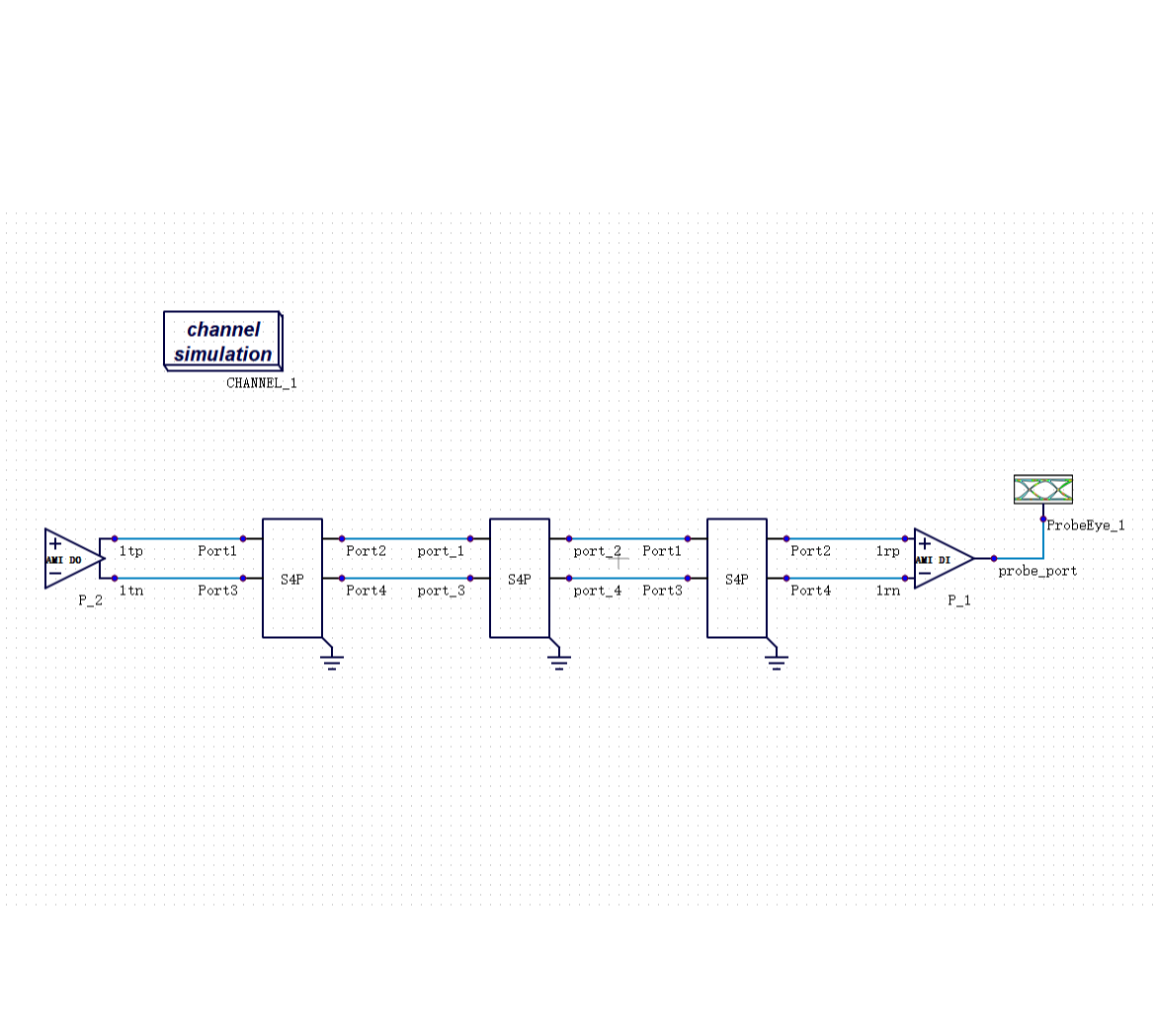

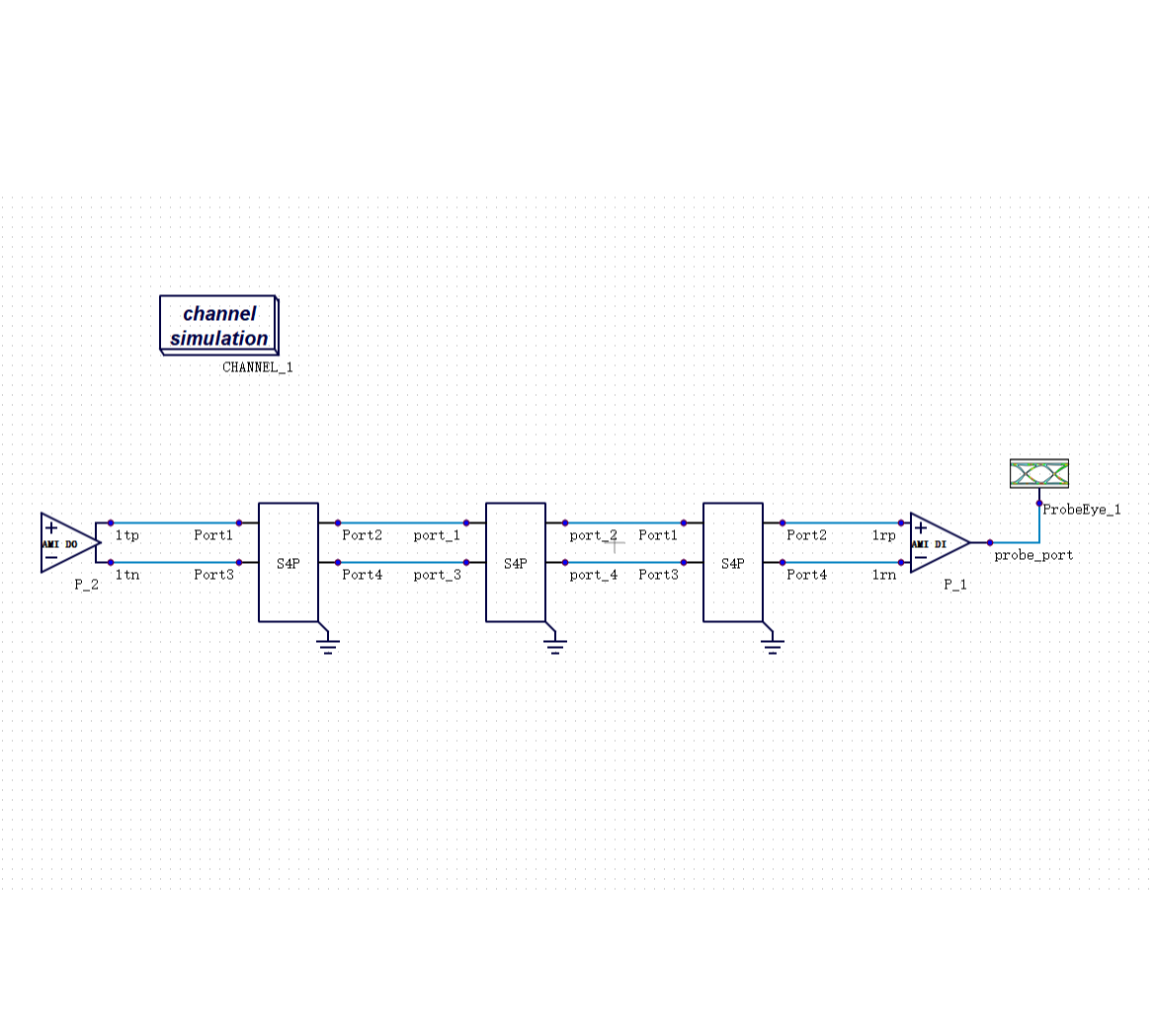

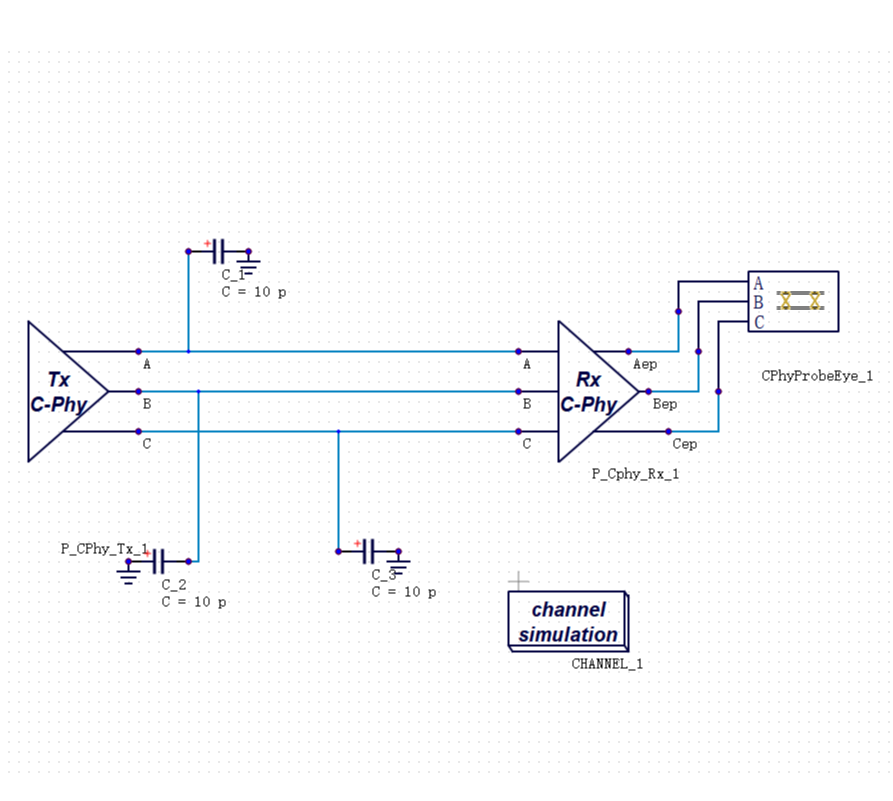

2、互联和带宽的优化

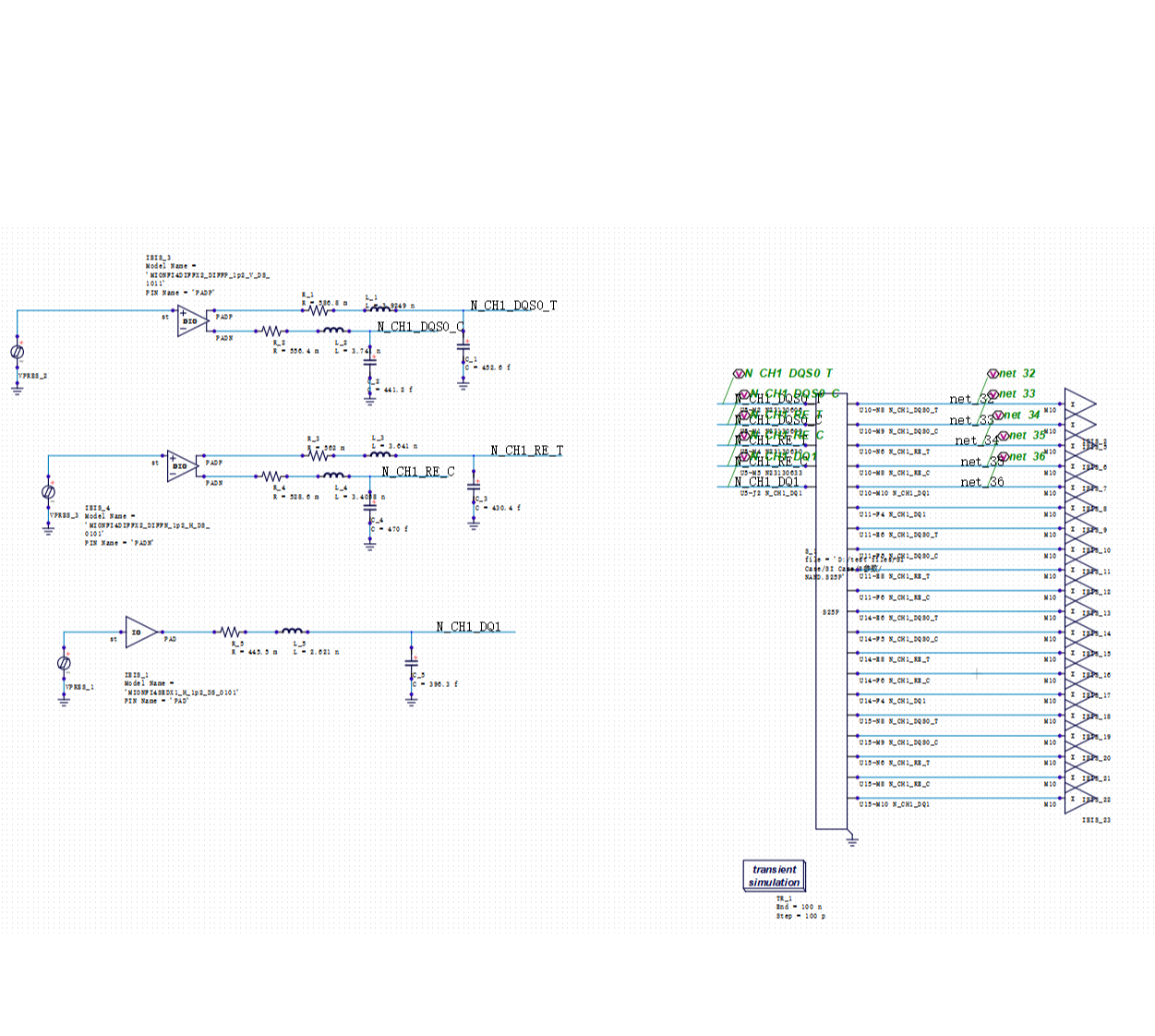

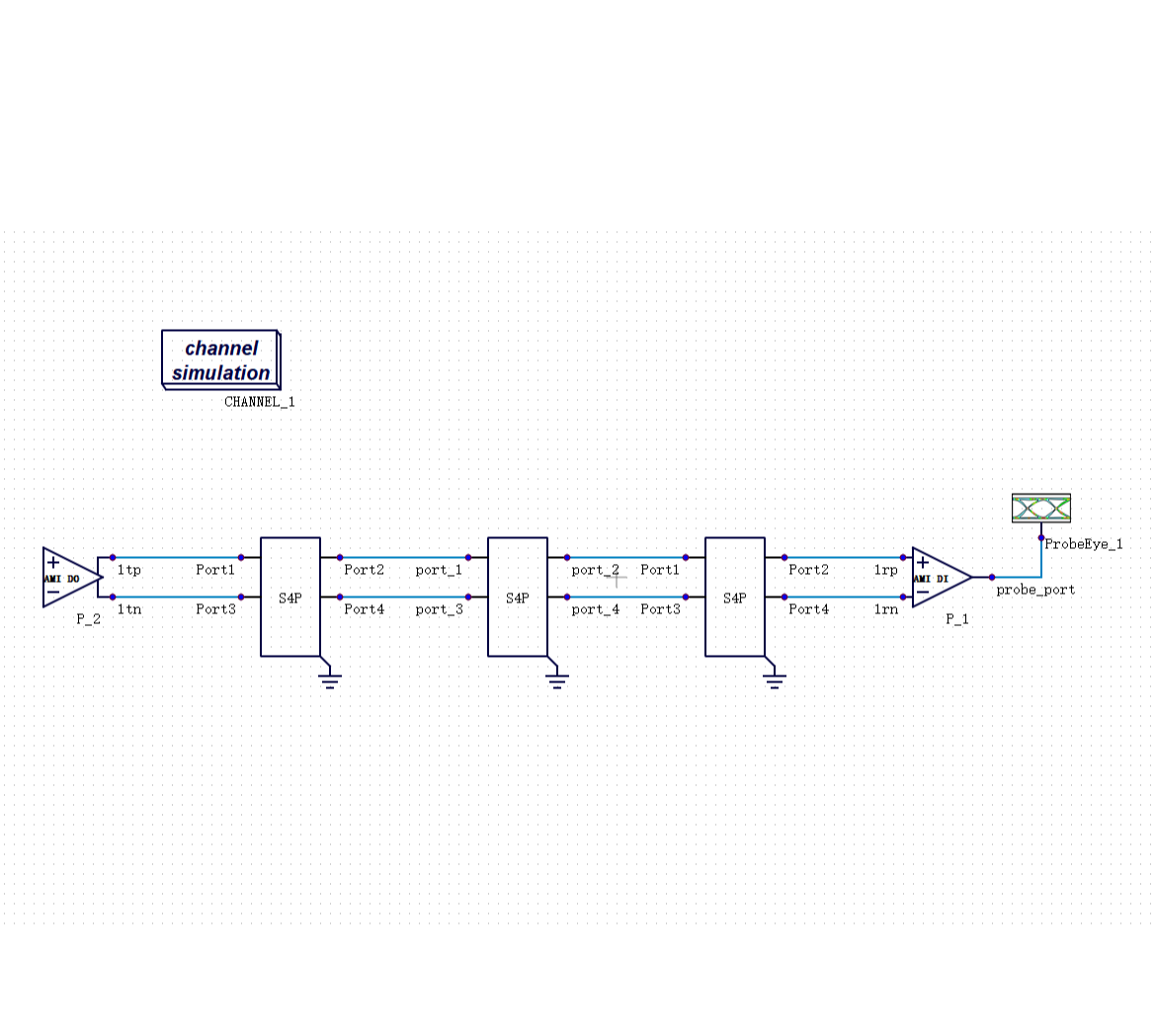

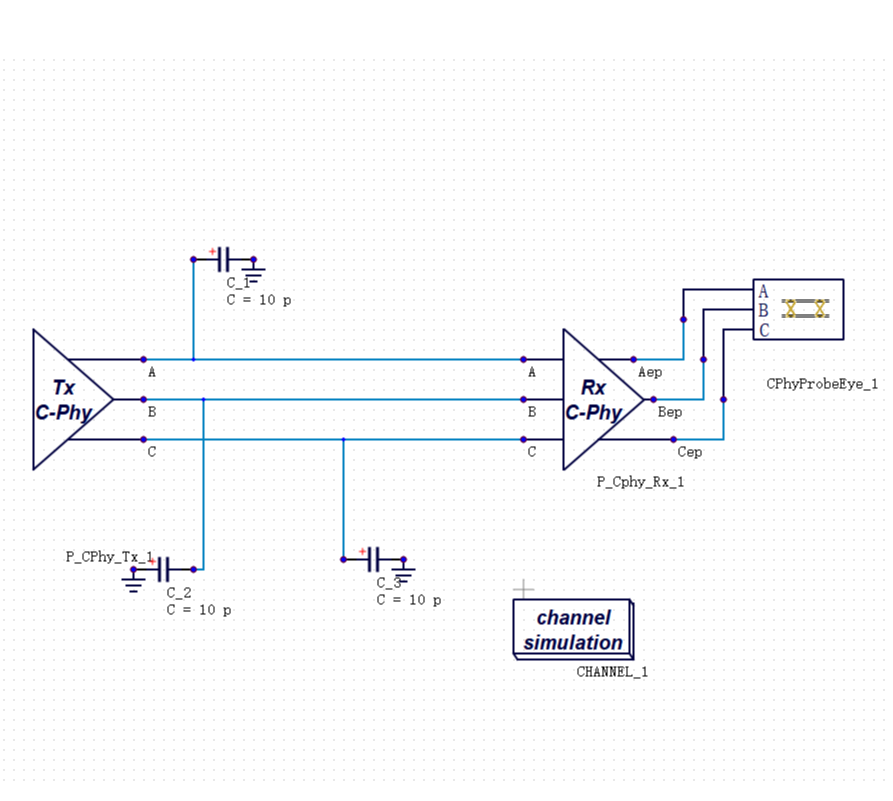

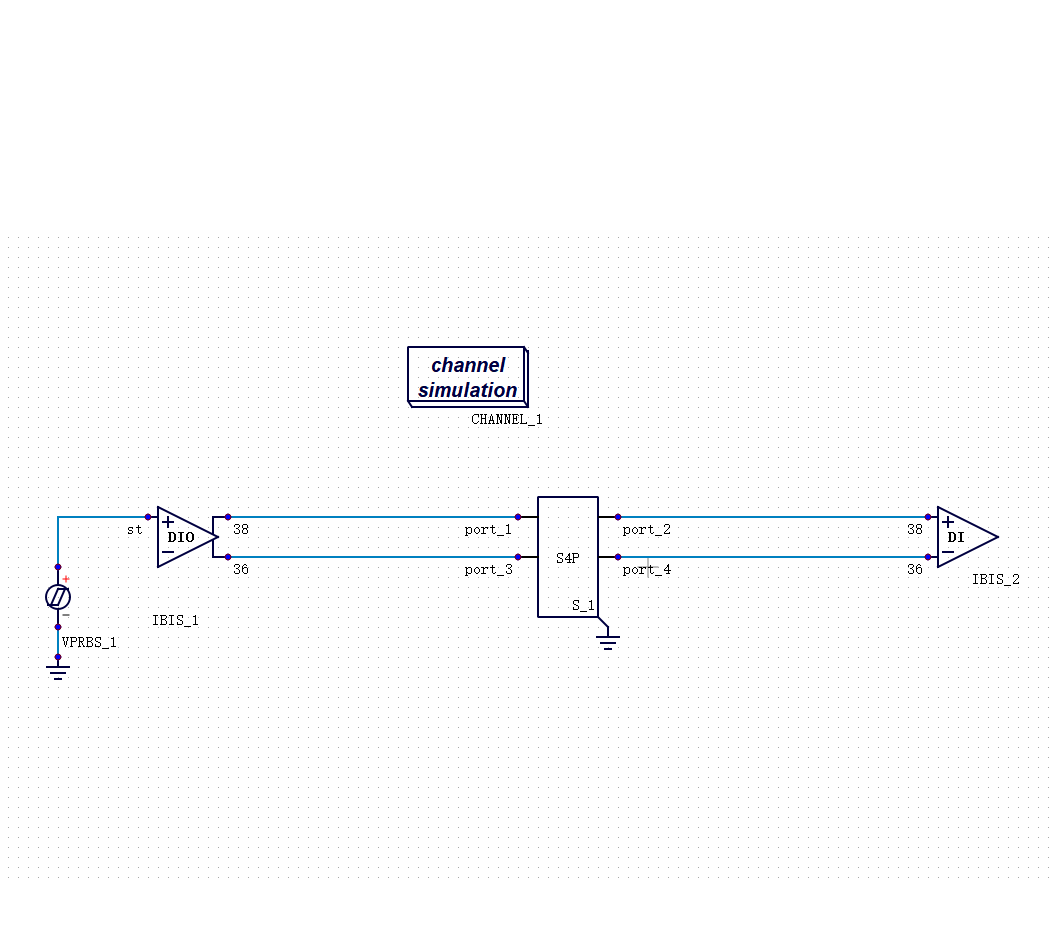

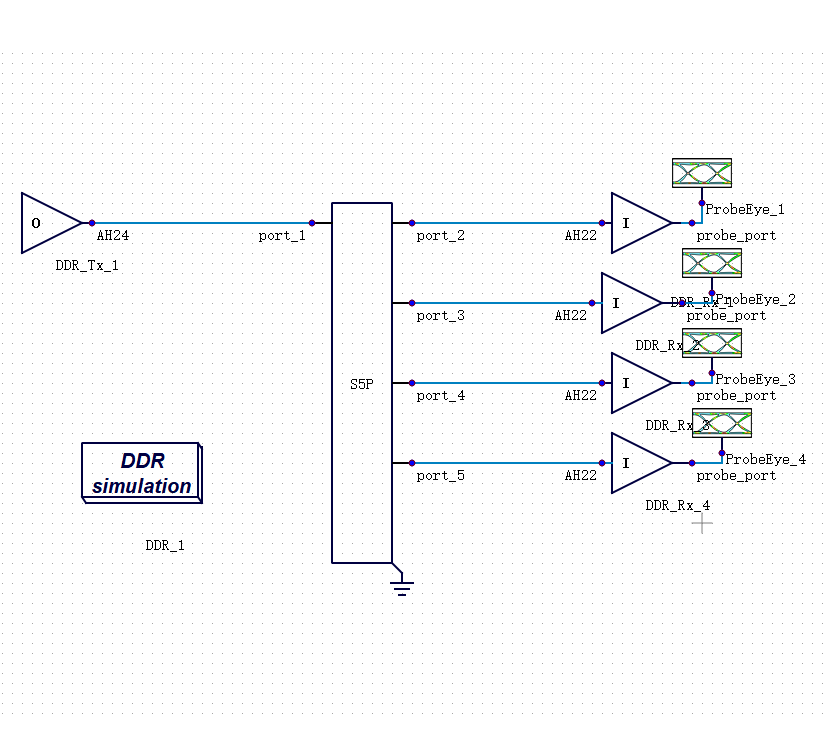

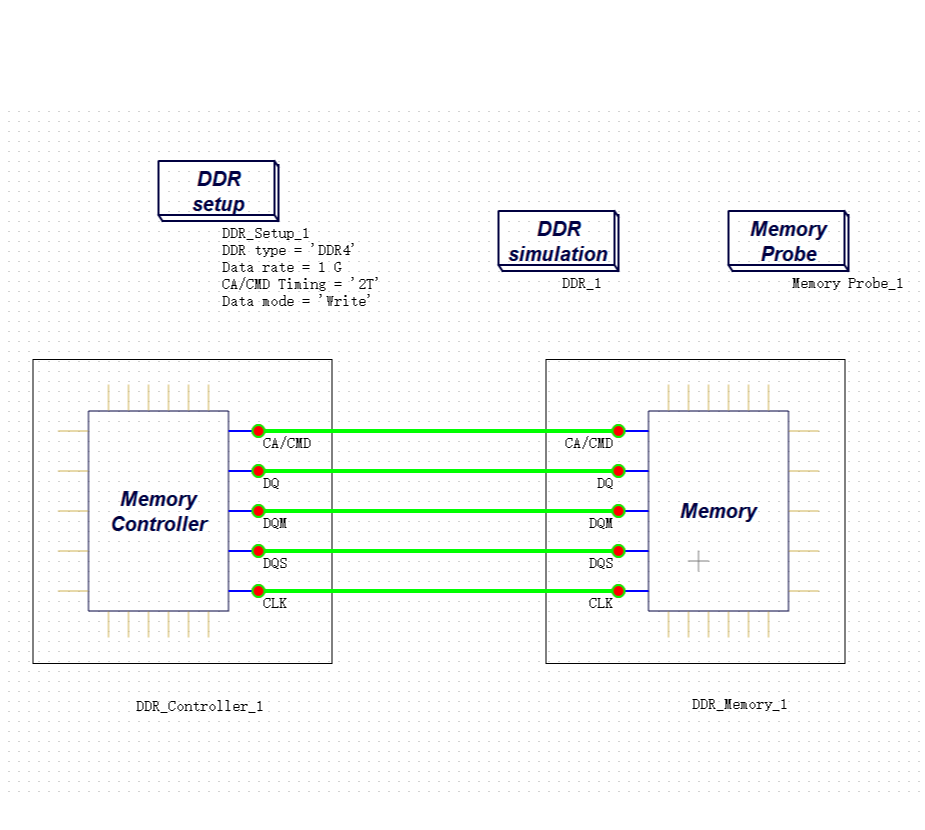

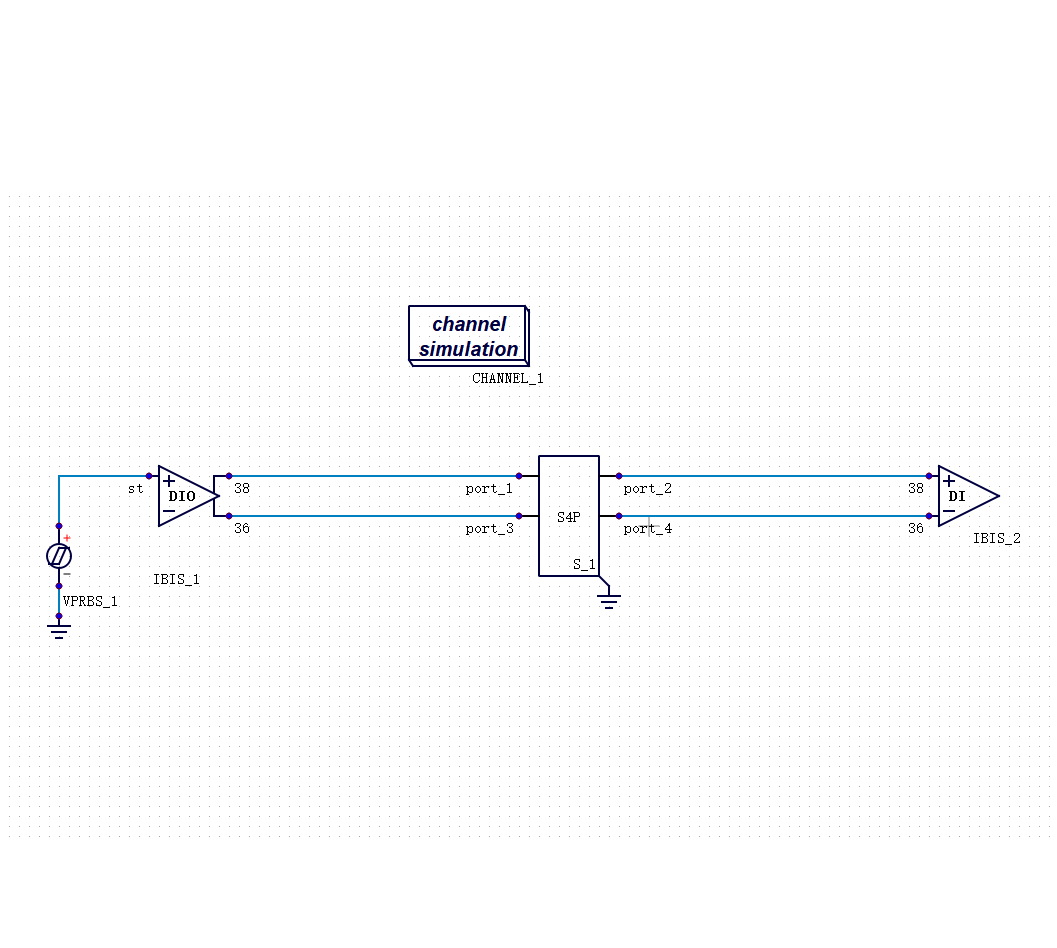

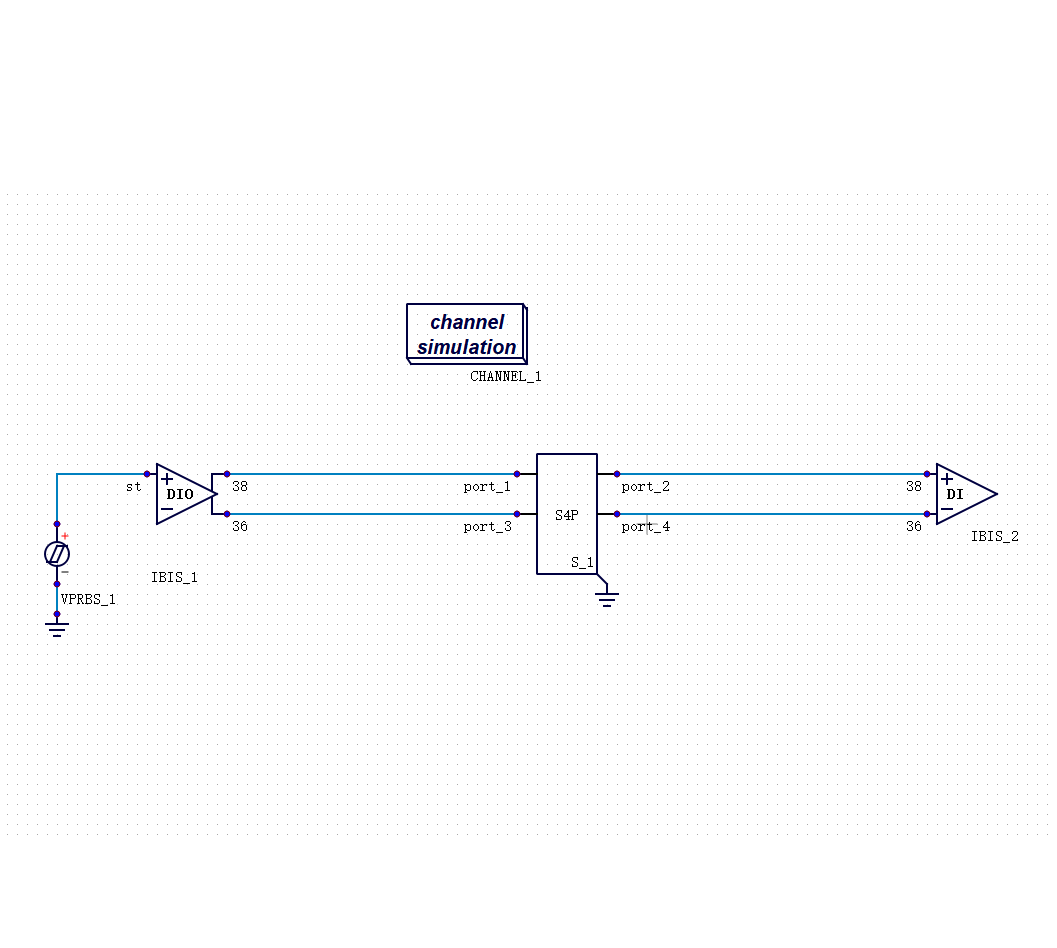

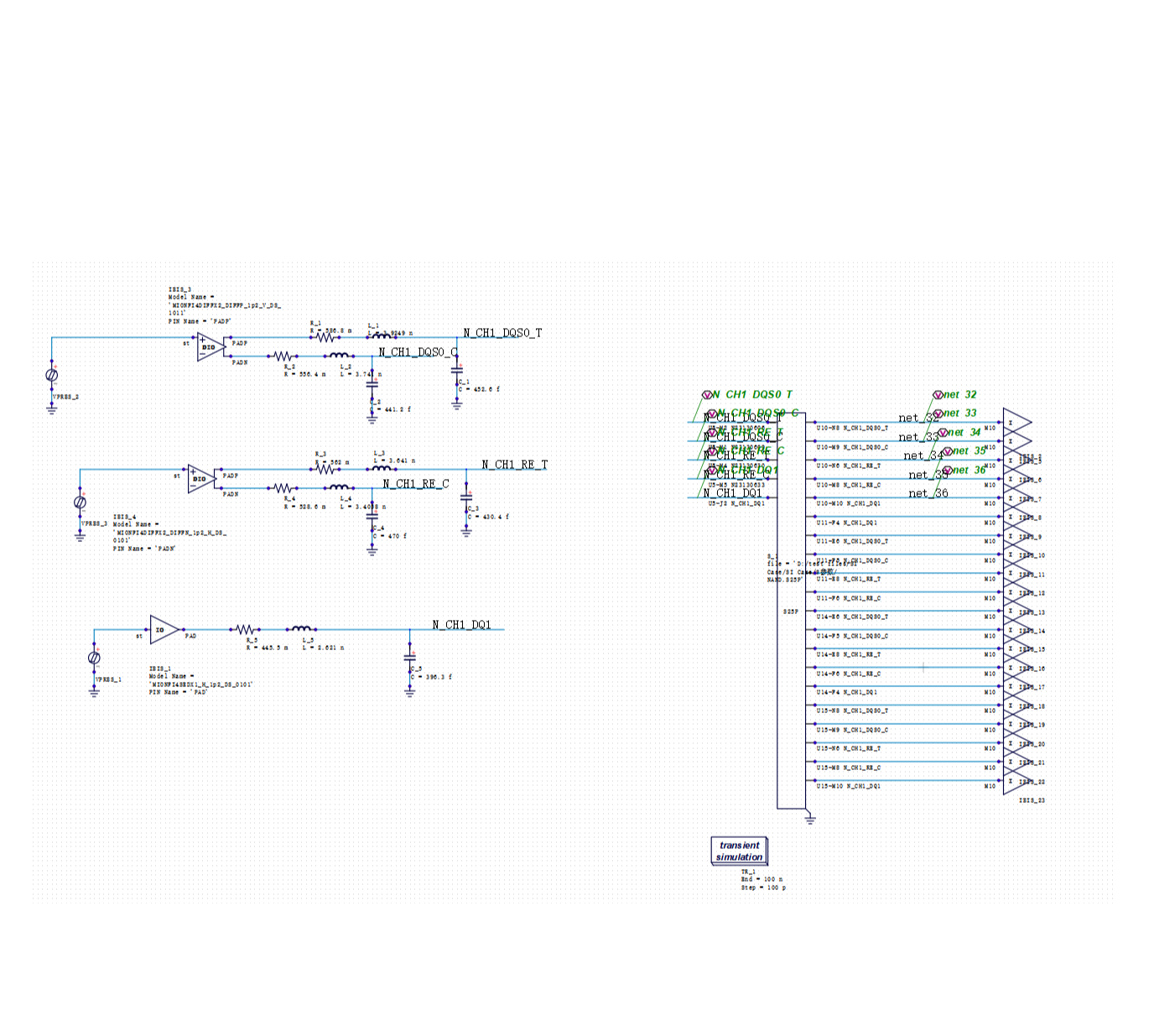

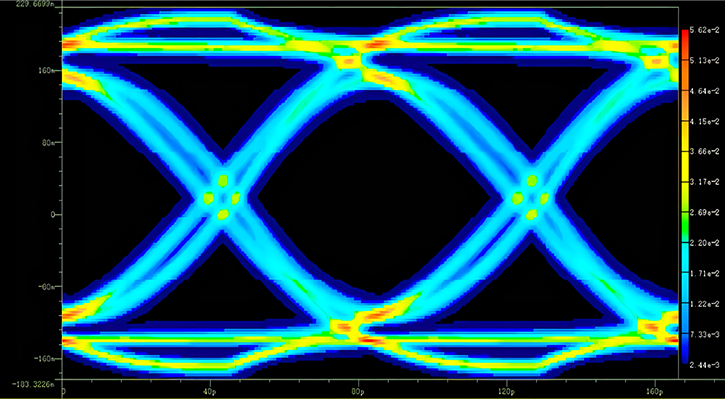

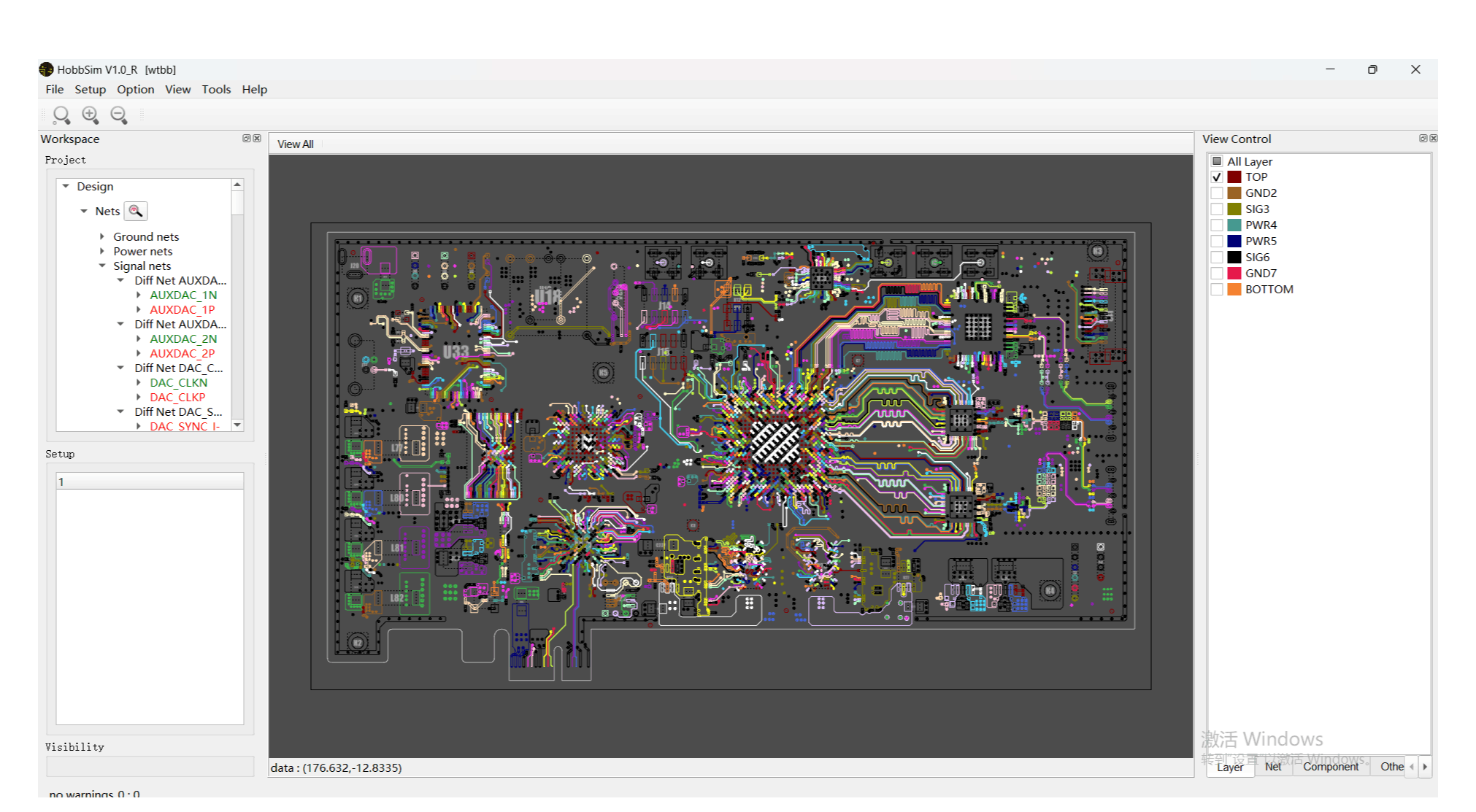

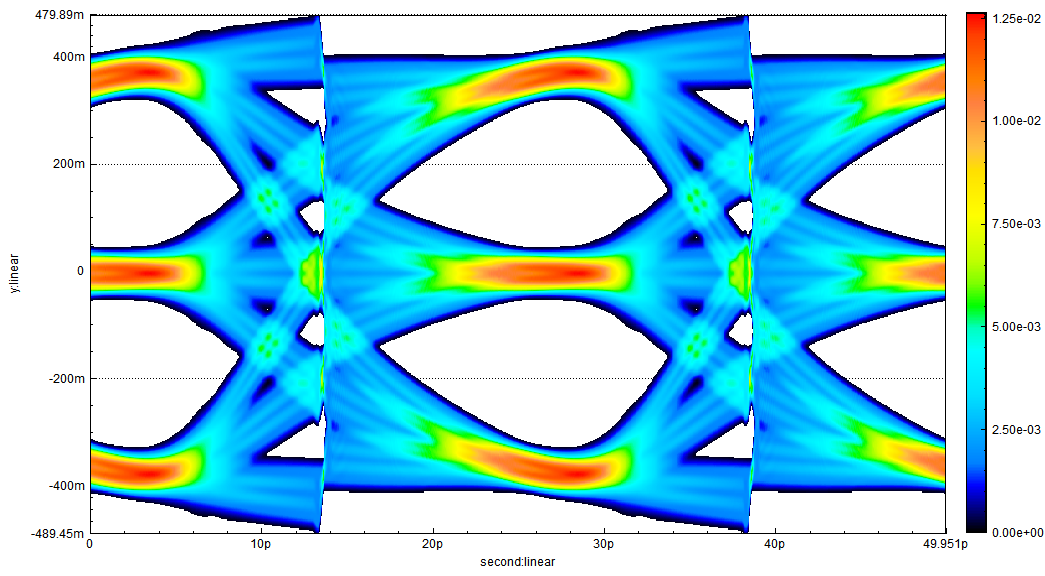

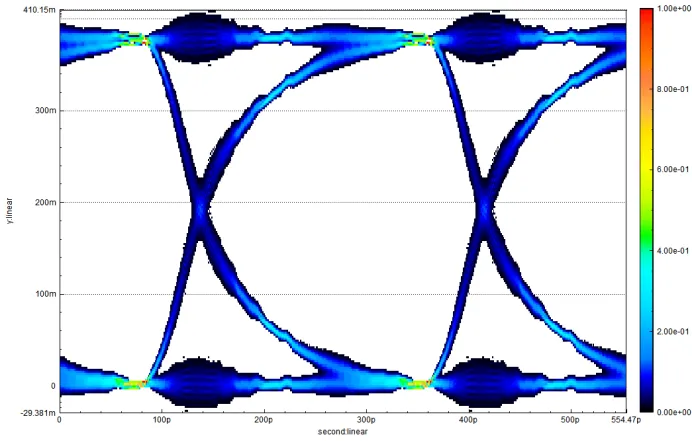

Chiplet之间的互连是其设计中至关重要的一环。不同的Chiplet需要高效、低延迟的互联,以保证整体系统的性能。传统的EDA工具通常集中在单一芯片内部的布线和互连上,但在Chiplet架构中,EDA工具不仅需要考虑单一芯片的信号完整性,还需要处理模块之间的互联设计、带宽规划以及信号传输的时序问题。为了支持这种需求,EDA工具需要具备跨模块的信号仿真和带宽分析能力。从纳米级晶体管到厘米级封装的全链路仿真,要求EDA工具支持电磁场求解器与电路仿真的联合优化。

3、封装层级设计与优化

传统EDA工具通常仅关注芯片级设计,而在Chiplet与先进封装架构下,设计和优化的范围扩展到了封装层级。封装不仅需要支持Chiplet间的电气连接,还要考虑到散热、机械结构、功耗、尺寸限制等多方面的因素。这要求EDA工具在设计初期就能进行封装级的电气、热、机械等多物理场仿真,并提供针对性的优化方案。同时由于当前UCIe(通用Chiplet互连标准)尚未完全普及,EDA工具需支持自定义互连协议验证。

4、多种制造工艺和异构集成

在Chiplet设计中,每个模块可能使用不同的制造工艺(例如,处理器模块使用先进的FinFET工艺,而存储模块可能使用不同的工艺),并且不同的模块需要通过异构集成来连接。不同工艺节点的Chiplet需统一DRC,EDA工具需要支持这种工艺多样性,并能够在不同工艺之间进行有效的互操作性分析和优化。此外,异构集成还要求EDA工具能够处理不同模块之间的电气、热管理和机械对接问题。

5、验证与测试的挑战

Chiplet架构的引入使得验证工作变得更加复杂。传统的SoC设计验证方法可能不适用于Chiplet系统,因为验证过程需要涉及到不同模块之间的交互,以及跨模块的接口验证。此外,由于多个厂商可能提供不同的Chiplet,确保这些模块之间的兼容性和协同工作变得更加困难。EDA工具需要支持跨厂商、多模块的验证,并能够处理复杂的接口标准和协议。

6、功耗和散热的管理

在Chiplet和先进封装的设计中,功耗管理和散热设计是至关重要的。Chiplet间互连功耗可能占系统总功耗15%以上,需动态电压频率调整算法支持,并且每个Chiplet可能具有不同的功耗特性,而它们在集成到封装中的时候,散热成为一个不容忽视的问题。EDA工具需要提供有效的功耗估算和热分析工具,以帮助设计者优化整体系统的能效和热管理,避免出现过热导致的性能下降或失效。

三、总结

Chiplet与先进封装的结合正重塑半导体产业模式,而EDA工具需突破传统边界,向多物理场、高自动化、全链路协同的方向演进。为了应对这些挑战,EDA工具必须不断进化,提供更强的跨模块设计、优化、验证以及仿真能力,同时支持异构集成和多厂商协作。巨霖科技将围绕Chiplet产业,就先进封装(2.5D,3D)技术提供一个覆盖全流程的EDA仿真平台,该平台提供完整的包括3DIC设计、SI/PI/多物理场分析的解决方案。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!