Power-Aware IBIS模型介绍与应用

-

2025.02.27

引言:在现代高速数字电路设计中,电源完整性和信号完整性是确保电路性能的关键因素。为了准确评估这些参数,设计师们引入了Power-Aware IBIS模型。本文将介绍Power-Aware IBIS模型的概念、内容组成及其在实际仿真中的应用案例。

一、Power-Aware IBIS模型概述

Power-Aware IBIS模型是一种扩展的标准IBIS模型,通过考虑电源噪声对信号传输的影响,显著提升了仿真精度。传统的IBIS模型主要用于模拟信号的电压波形和时间特性,但它忽略了电源噪声的影响。而Power-Aware IBIS模型则通过引入电源分配网络的特性和电源噪声,能够更准确地模拟真实世界中的信号传输情况。

二、Power-Aware IBIS模型的组成

Power-Aware IBIS模型包含多个关键部分,每个部分都承担着重要的功能。

1、IV表(电流-电压表)

IV表用于描述缓冲器在不同状态下的电流特性。具体包括以下四种:

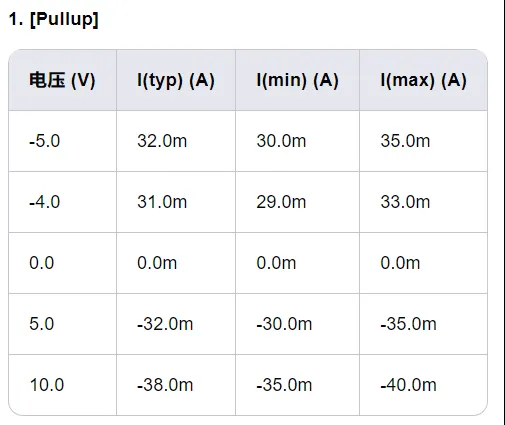

IV for PU:缓冲器输出逻辑高电平(逻辑1)时的电流特性。这个参数对于理解在高电平时缓冲器的电源需求非常重要。

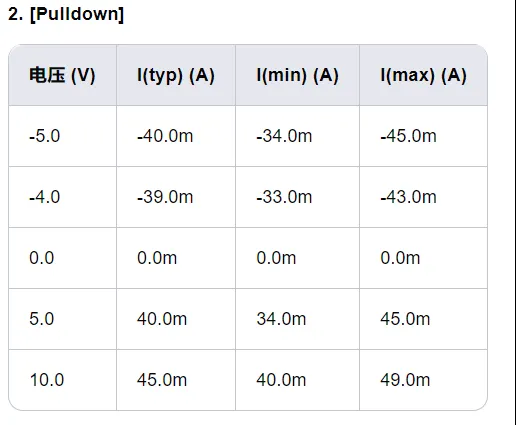

IV for PD:缓冲器输出逻辑低电平(逻辑0)时的电流特性。它帮助设计师了解在低电平时的电流消耗情况。

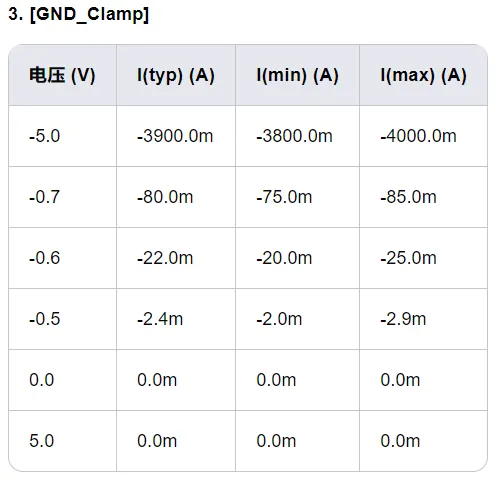

IV for GC:表示以GND为基准的ESD保护二极管的电流-电压特性,描述了地钳位二极管的行为。

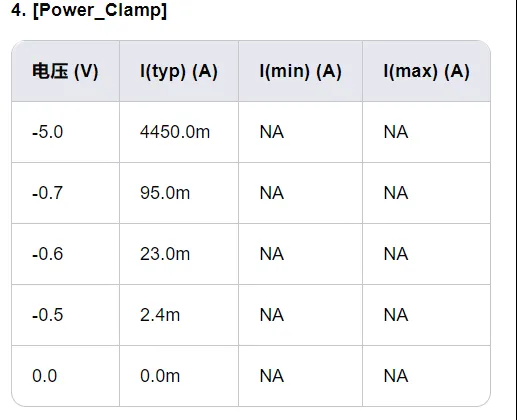

IV for PC:表示以VDD为基准的ESD保护二极管的电流-电压特性,描述了电源钳位二极管的行为。

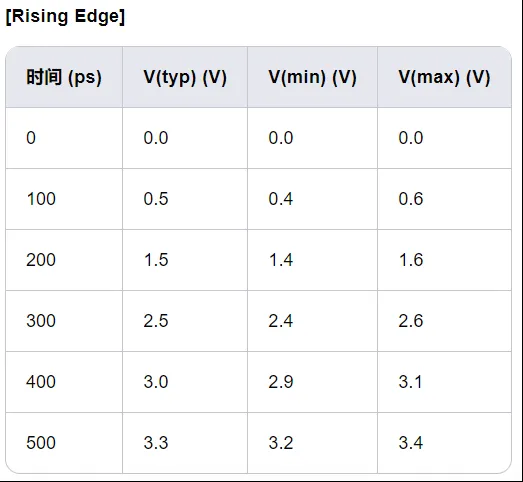

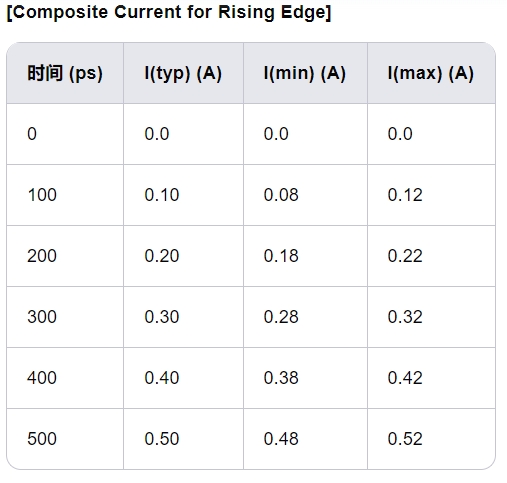

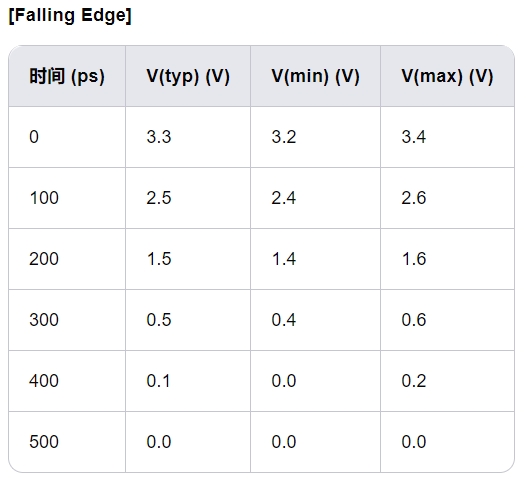

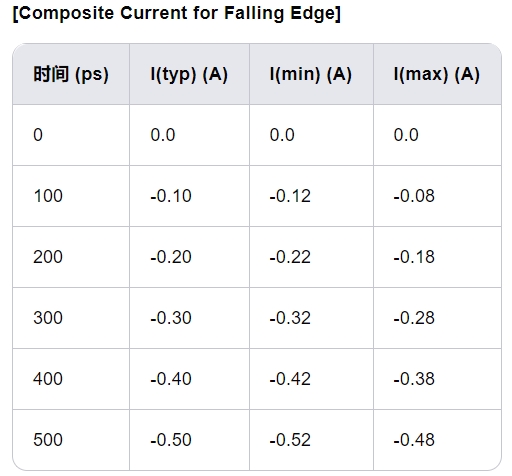

2、 Rising/Falling Waveform以及Composite Current

Composite Current描述了缓冲器在电源端(如VCCO或GND)的电流变化,包括上升沿和下降沿的电流波形。这些电流波形与信号的电压波形(V-T)同步,用于模拟电源噪声。通过对这些电流波形的精确建模,可以有效捕捉电源噪声对信号传输的影响。

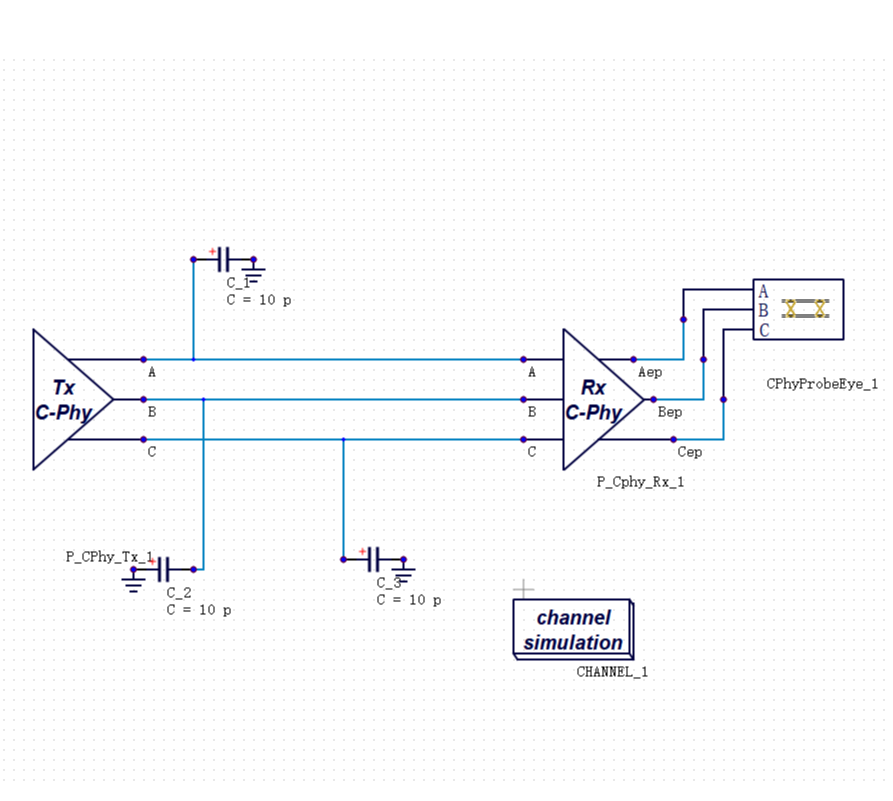

三、SIDesigner具体案例分析(深度解析 高速信号完整性仿真平台:SIDesigner)

运用Power-Aware IBIS模型进行仿真

要进行Power-Aware IBIS仿真,首先需要从芯片供应商处获取支持Power-Aware功能的IBIS文件。这些文件通常包含上述关键字和表格。

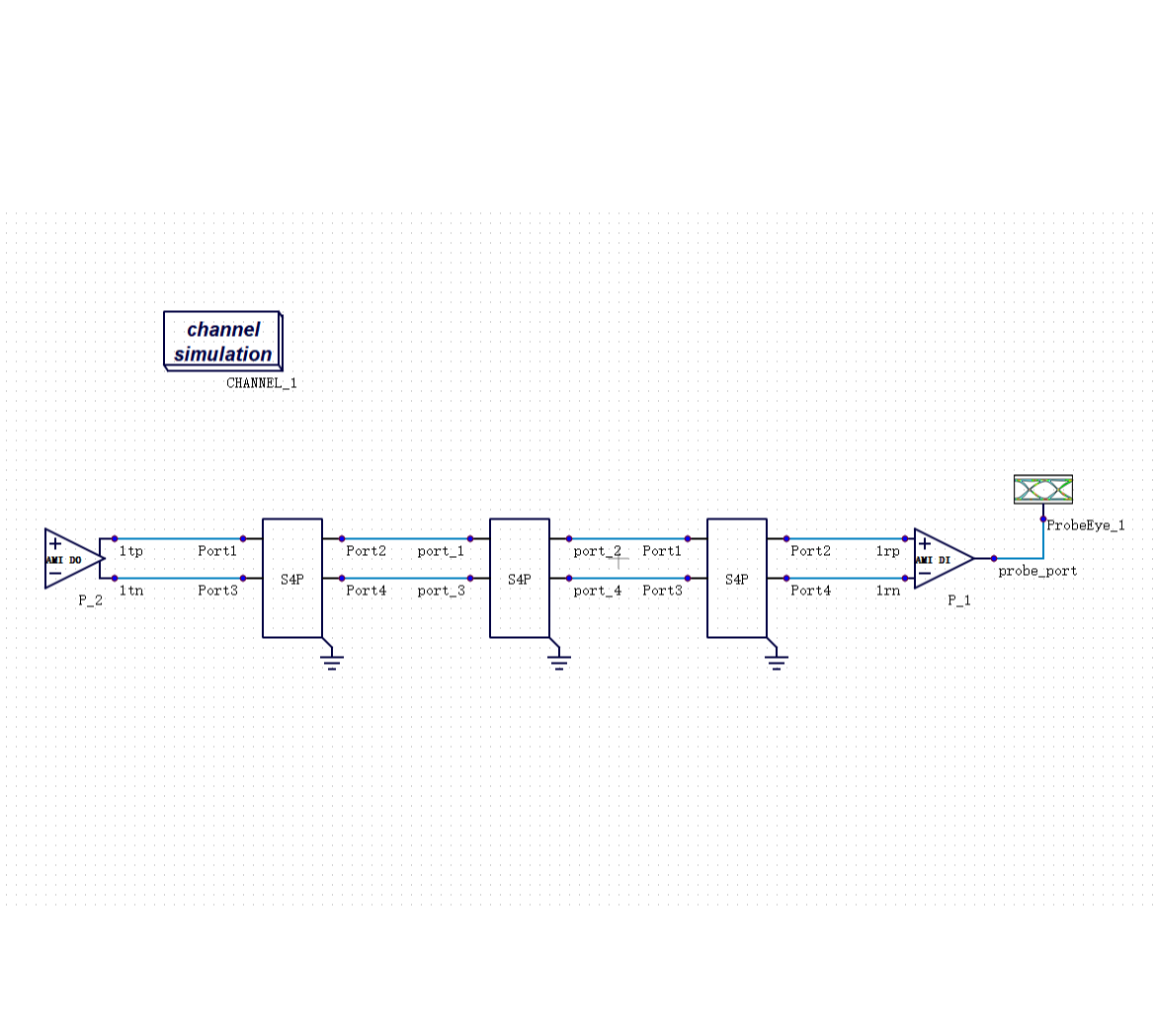

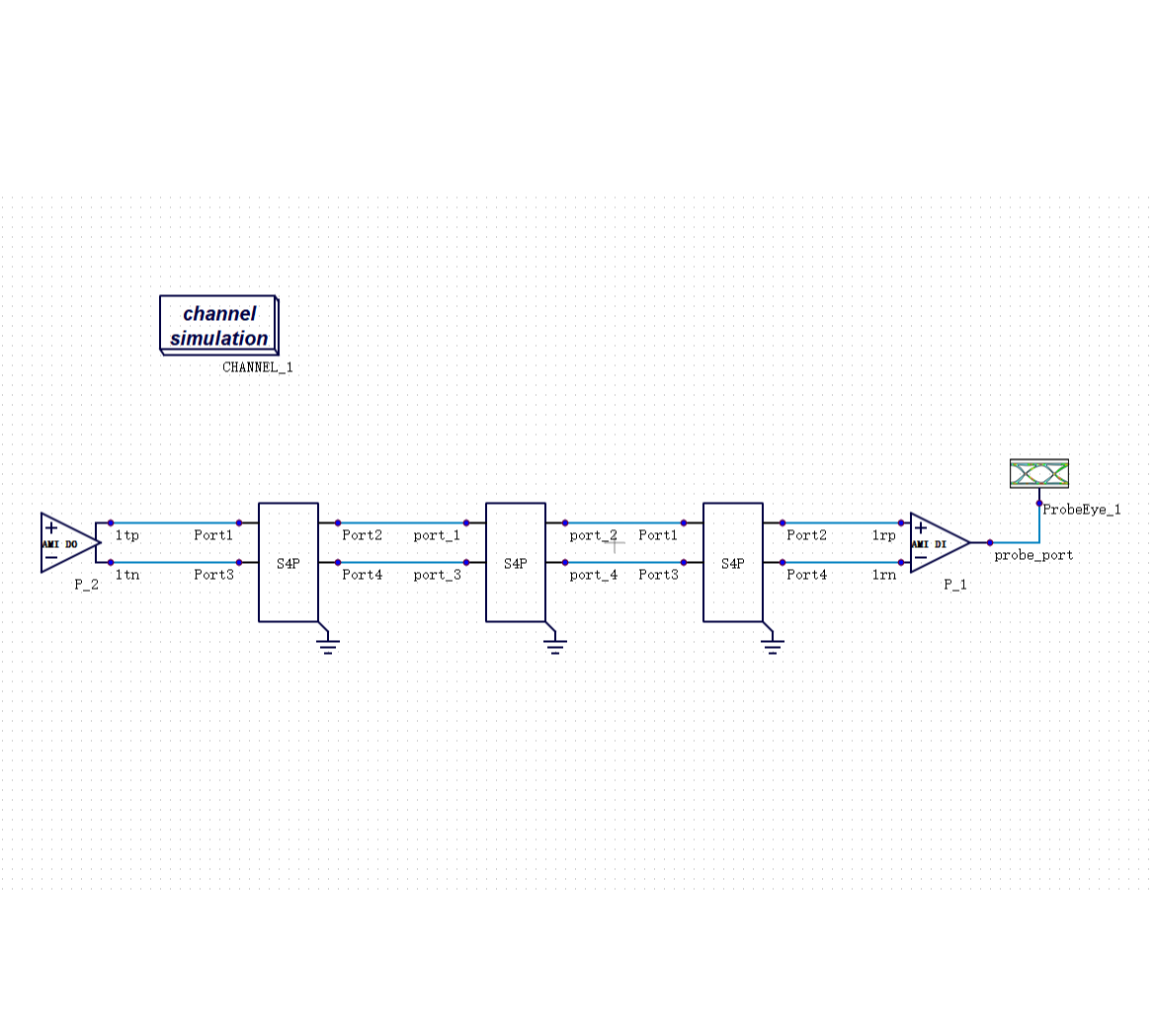

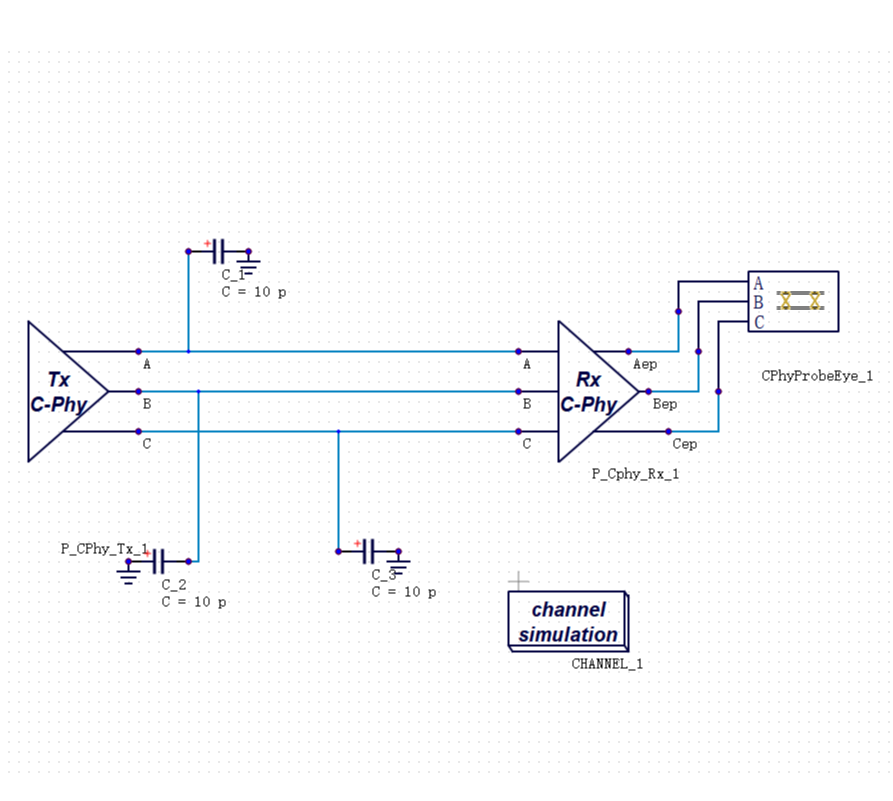

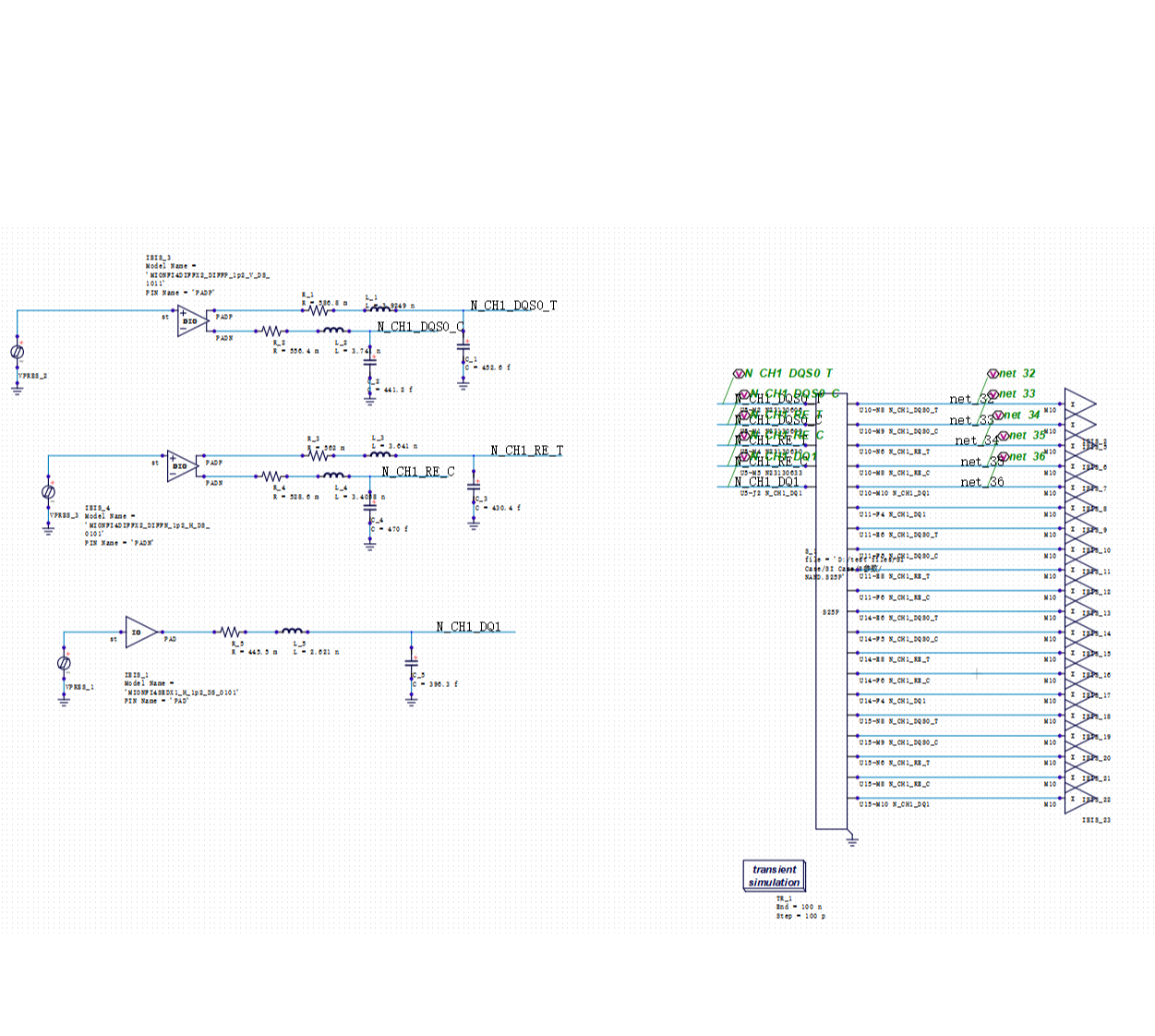

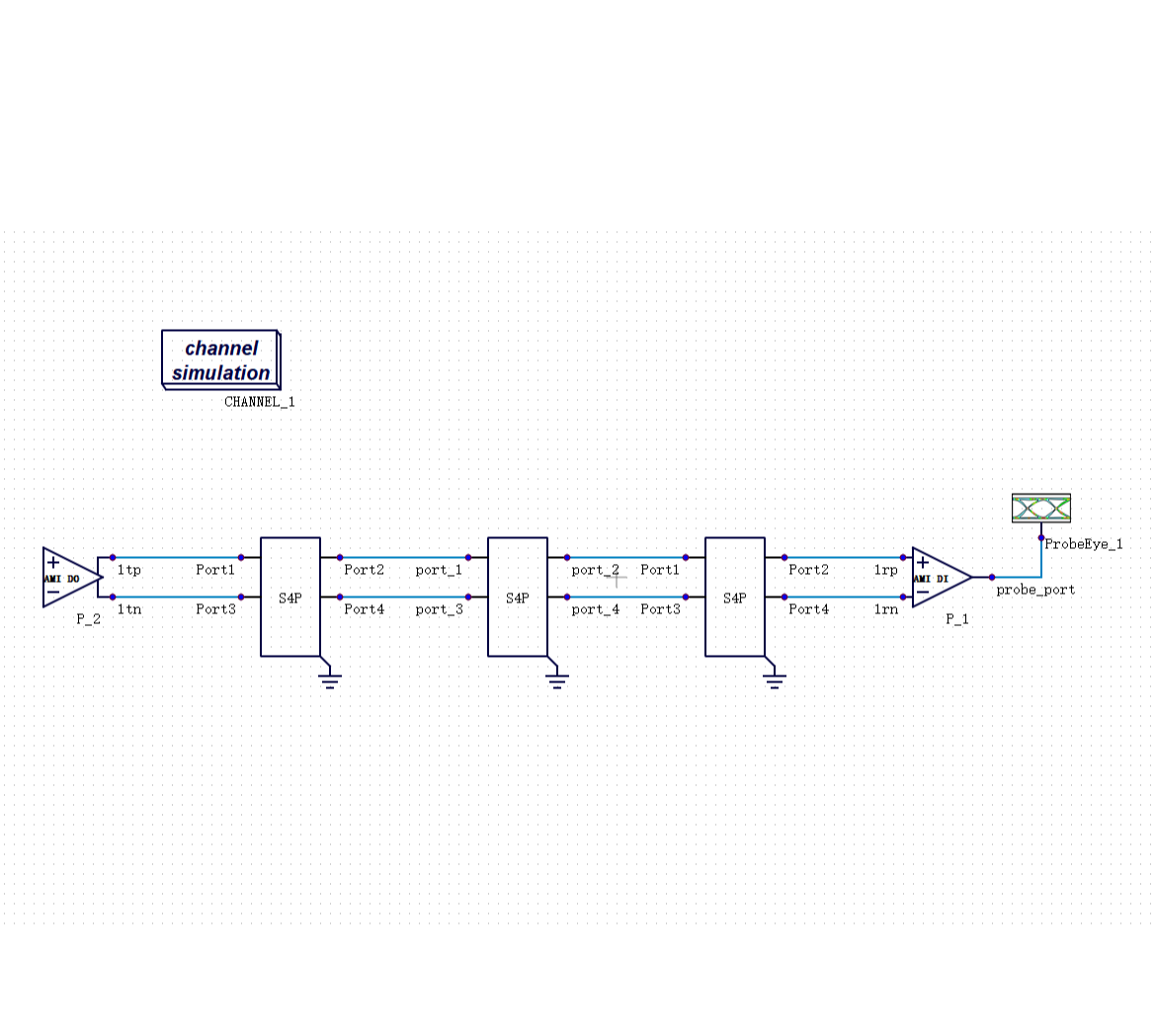

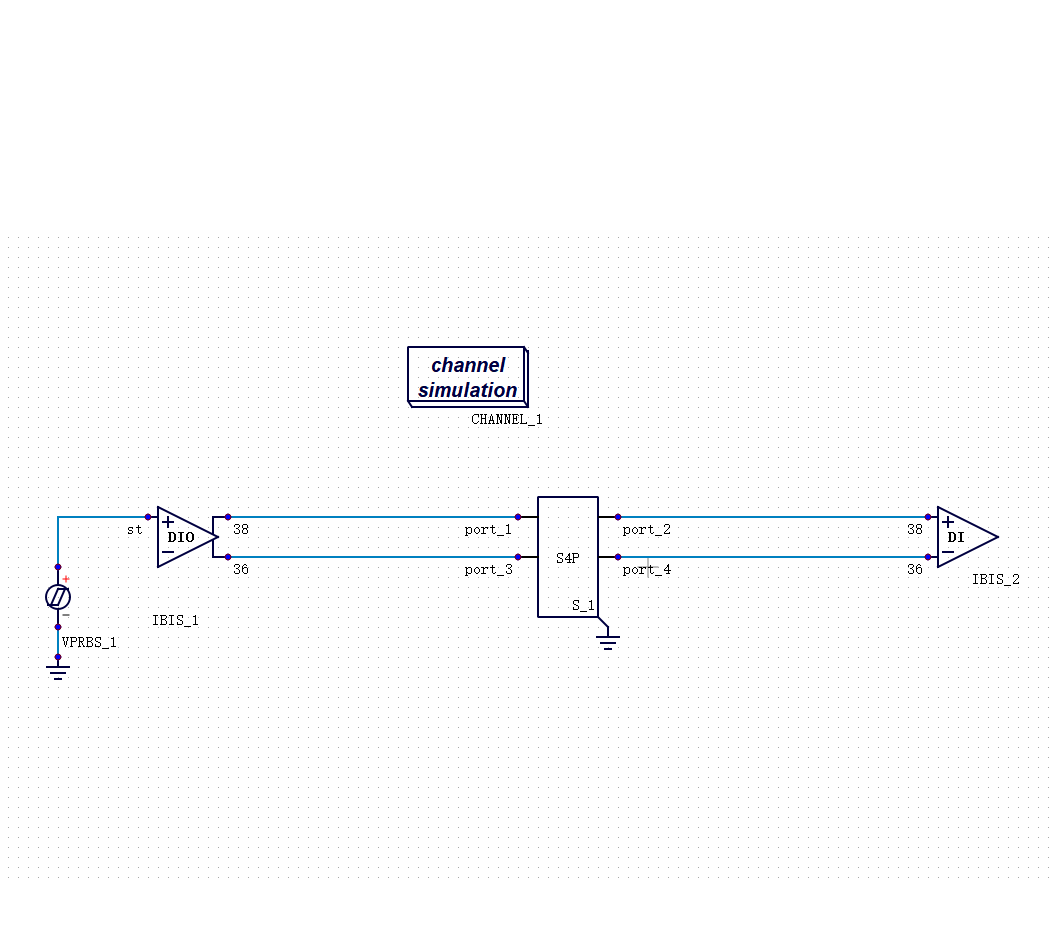

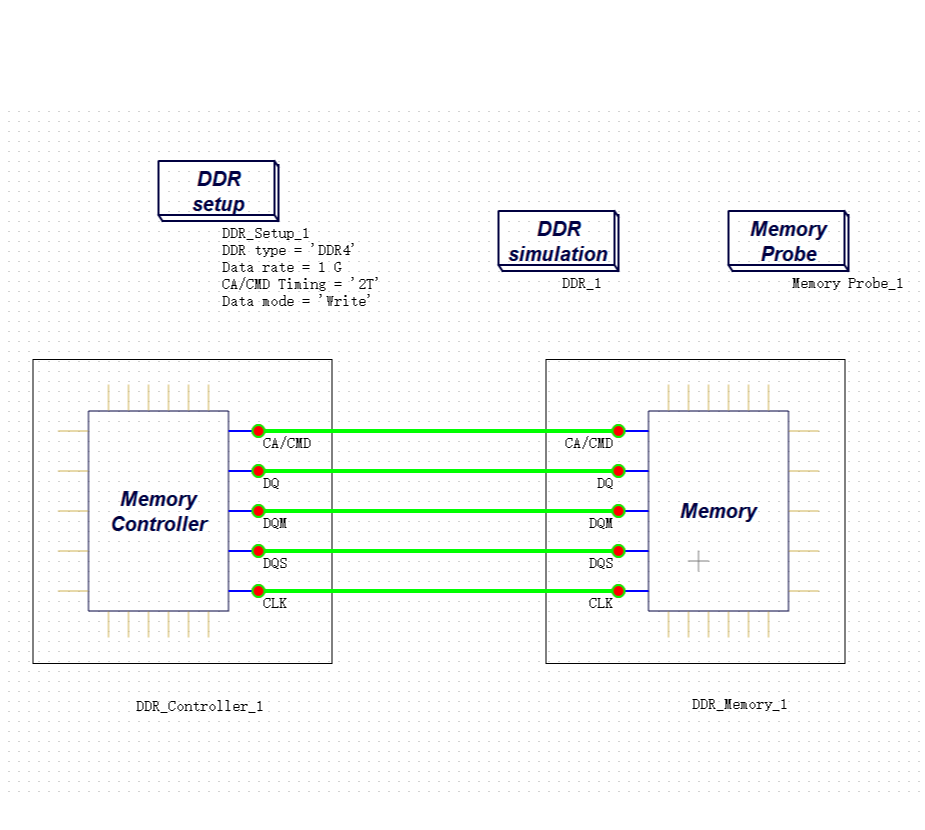

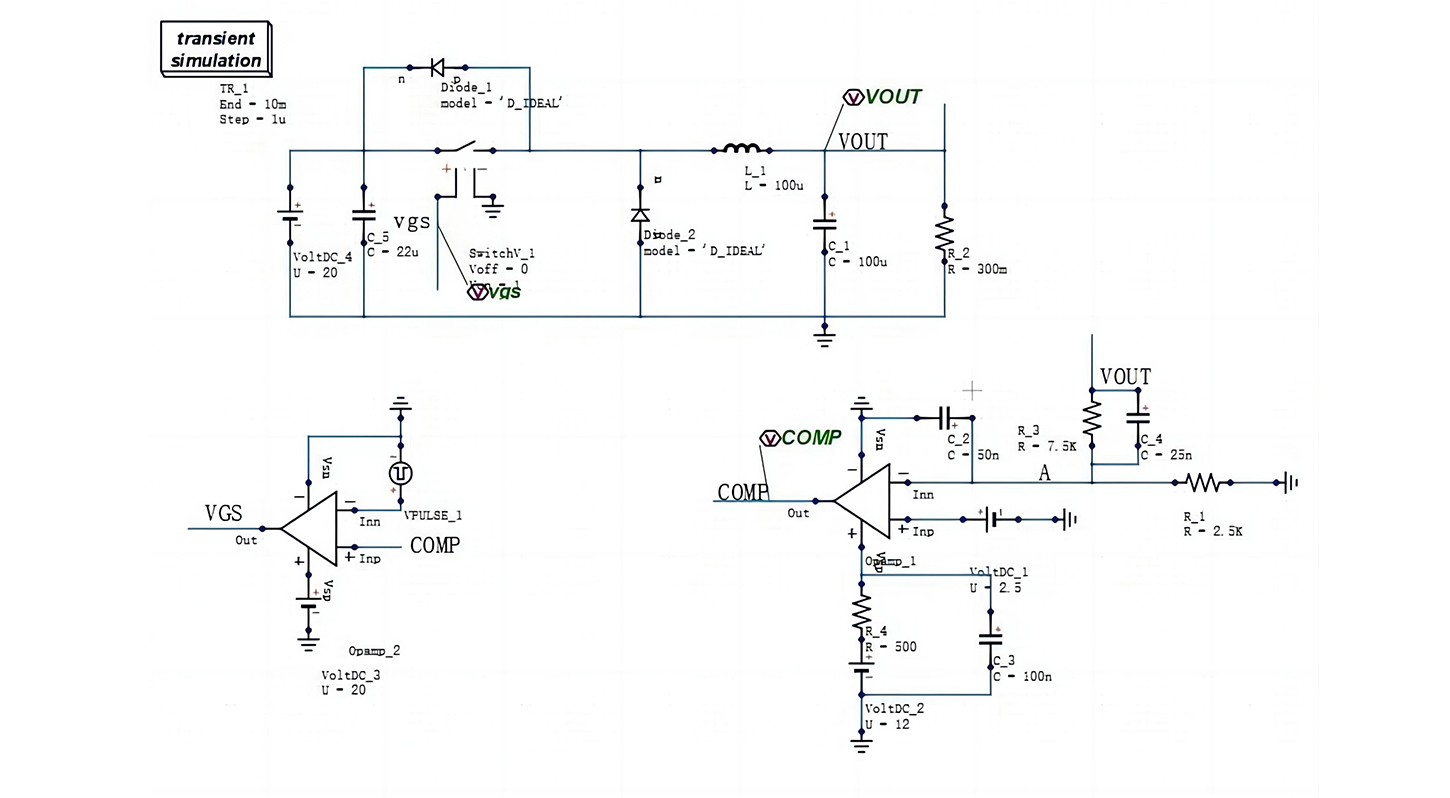

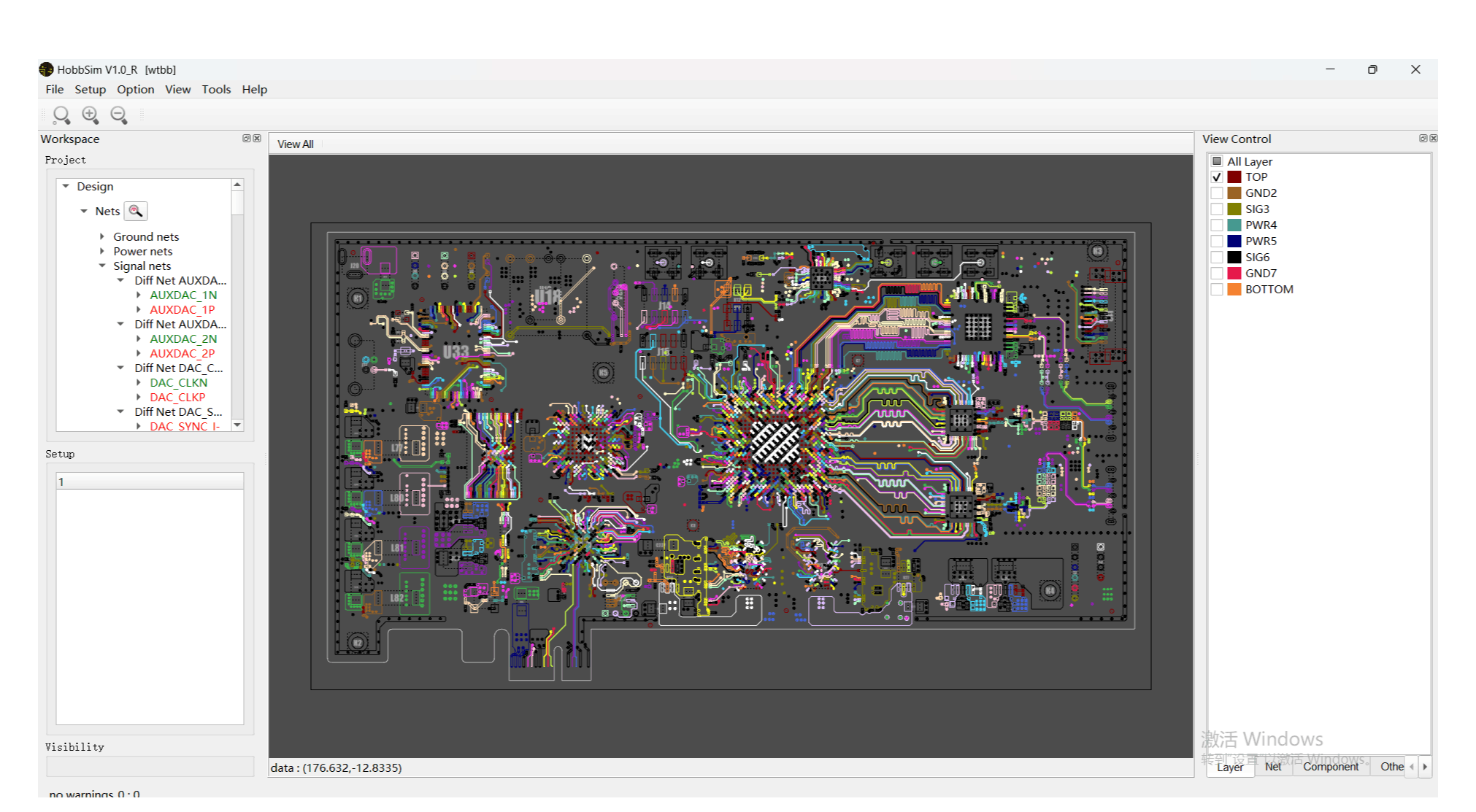

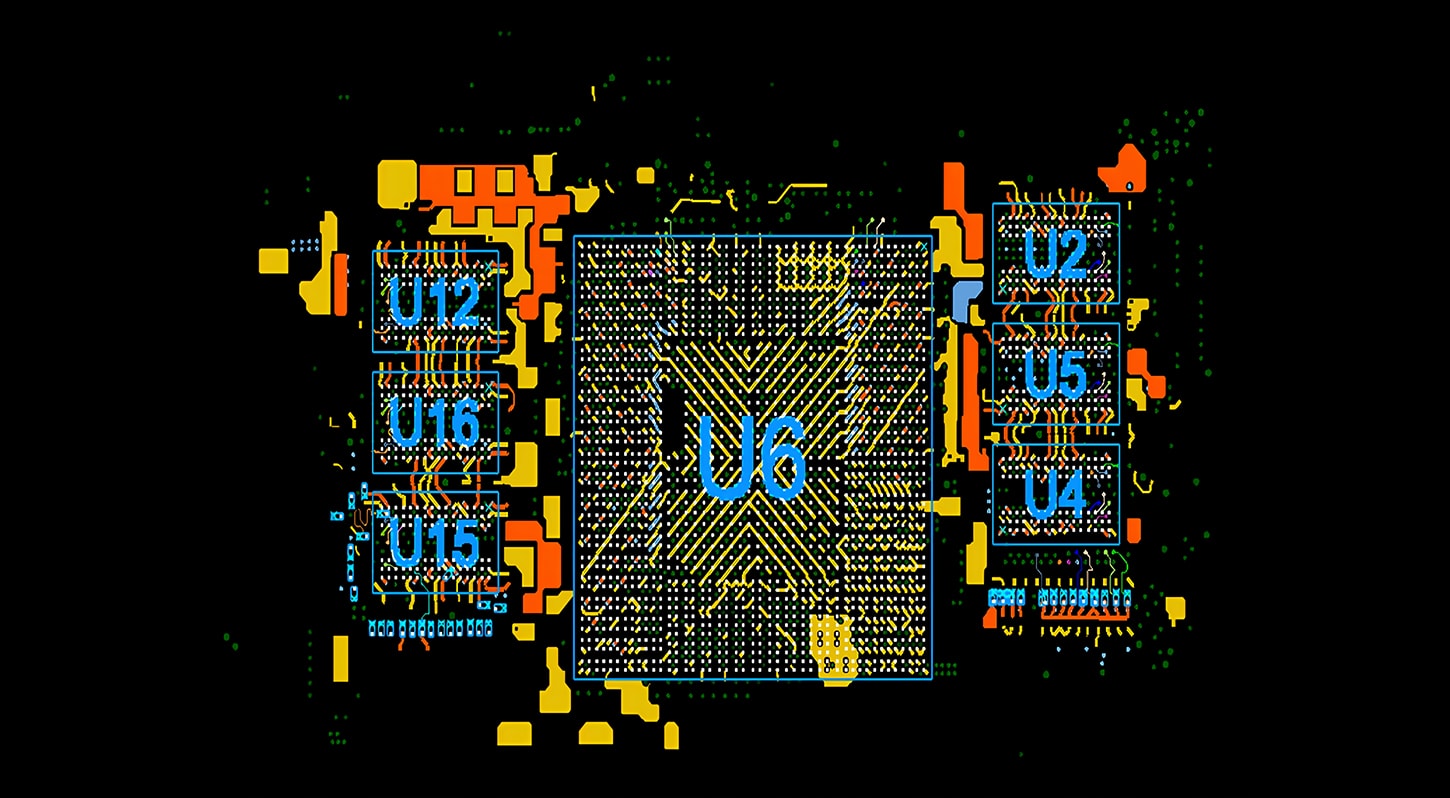

接下来,需要配置仿真工具以支持Power-Aware IBIS模型的导入与仿真。我们使用巨霖科技的SIDesigner来演示使用过程,以下是一个具体的DDR4仿真案例。

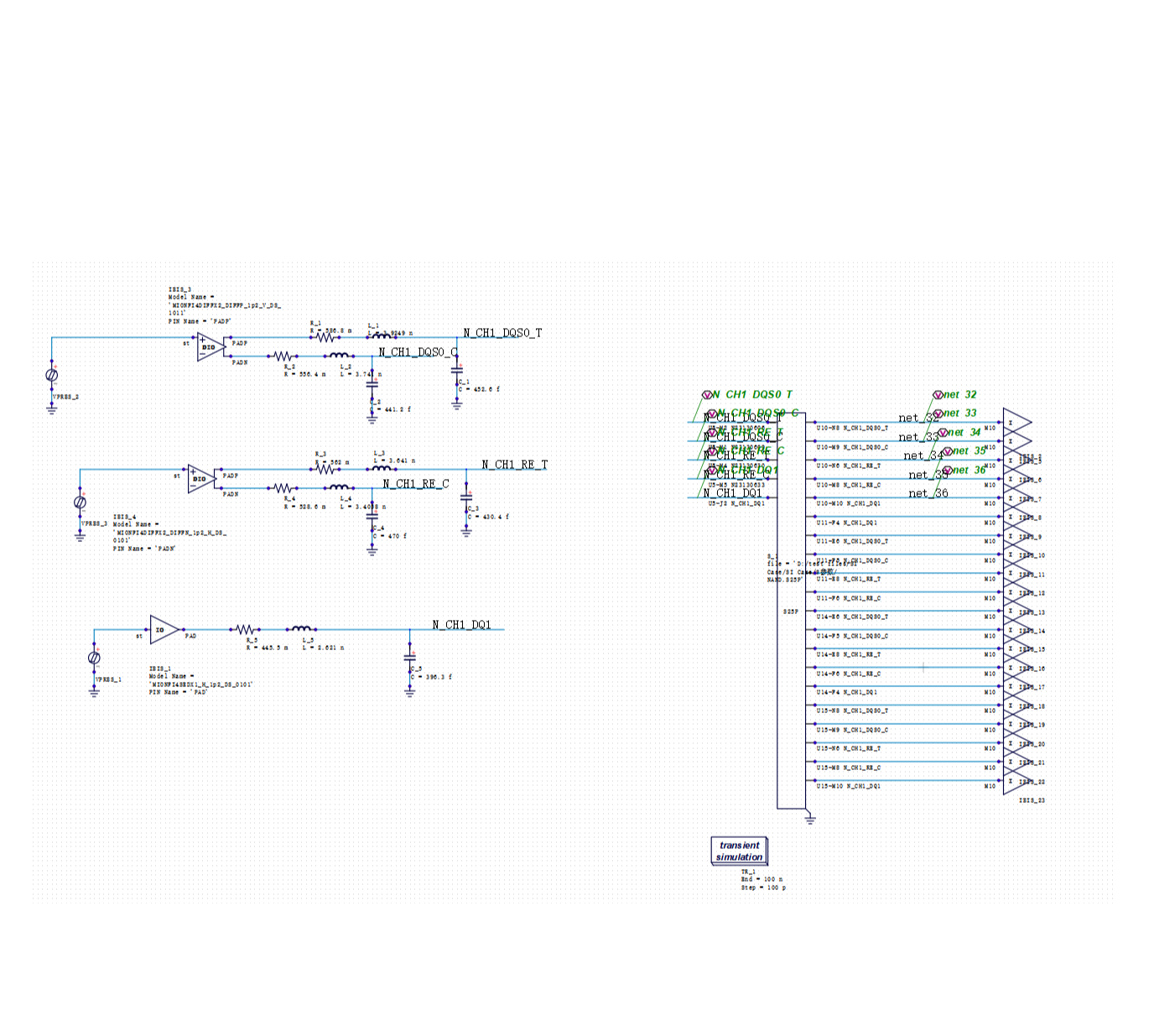

在巨霖SIDesigner中进行Power-Aware IBIS模型的导入与仿真包括以下几个步骤:

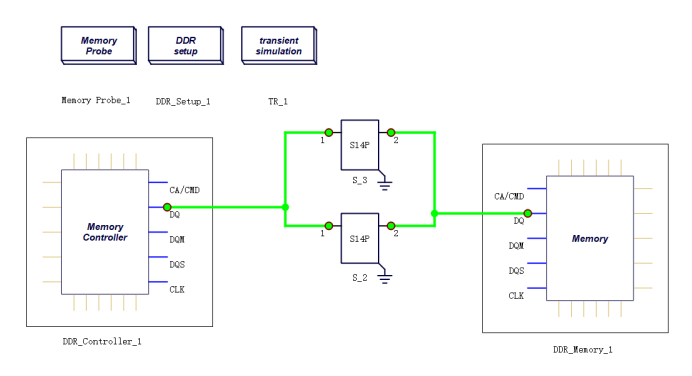

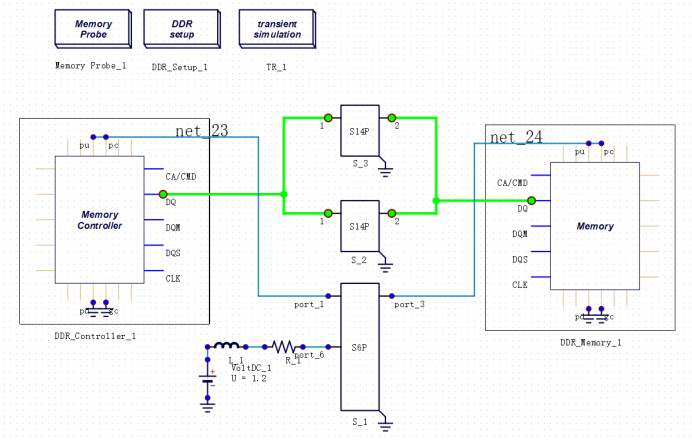

1、导入IBIS文件:将获取到的IBIS文件导入仿真工具中,本例中直接导入到DDR controller和 DDR memory组件中,完成批量信号仿真设置。

2、配置网络连接:根据实际连接关系,定义电源网络和信号网络的各个节点及其连接关系,确保网络连接的准确性。

3、设置仿真参数:根据设计需求设置仿真时间和步长等参数,以确保仿真结果的准确性和可靠性。

以下是分别使用理想电压源和非理想电压源的仿真工程及其仿真结果:

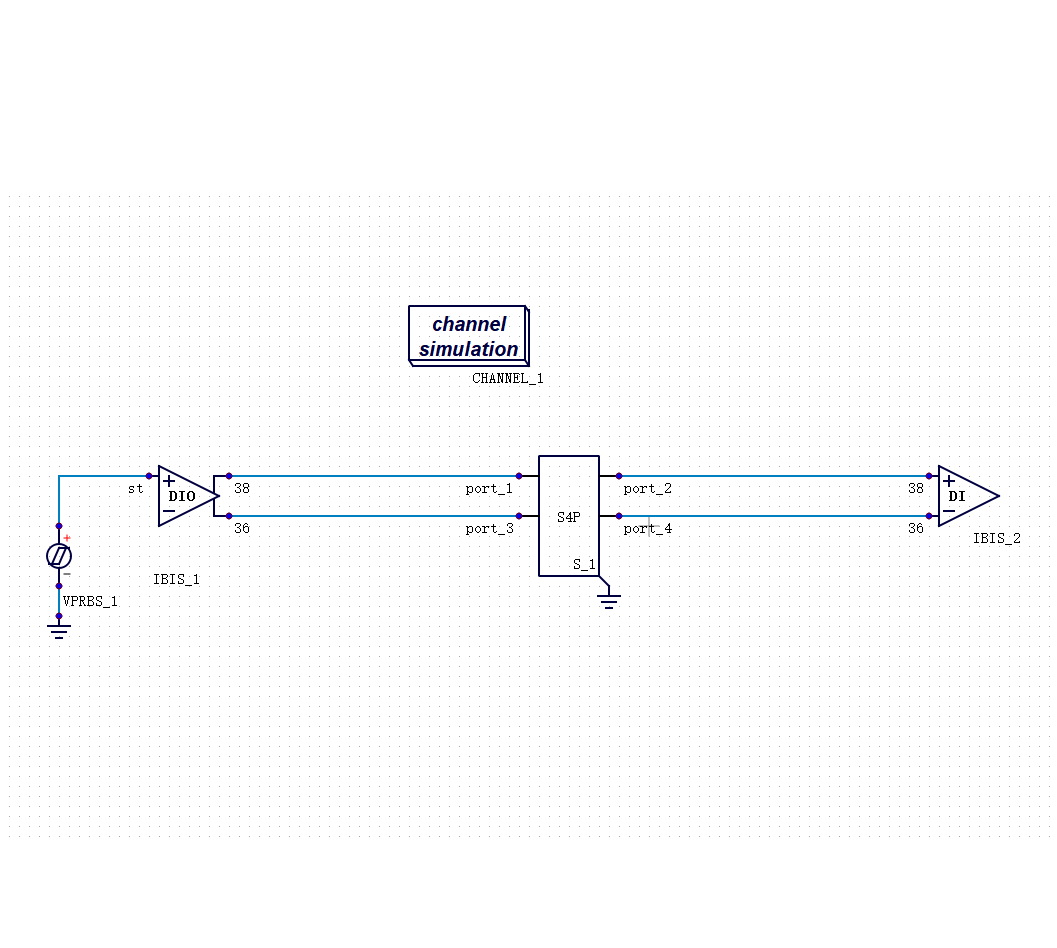

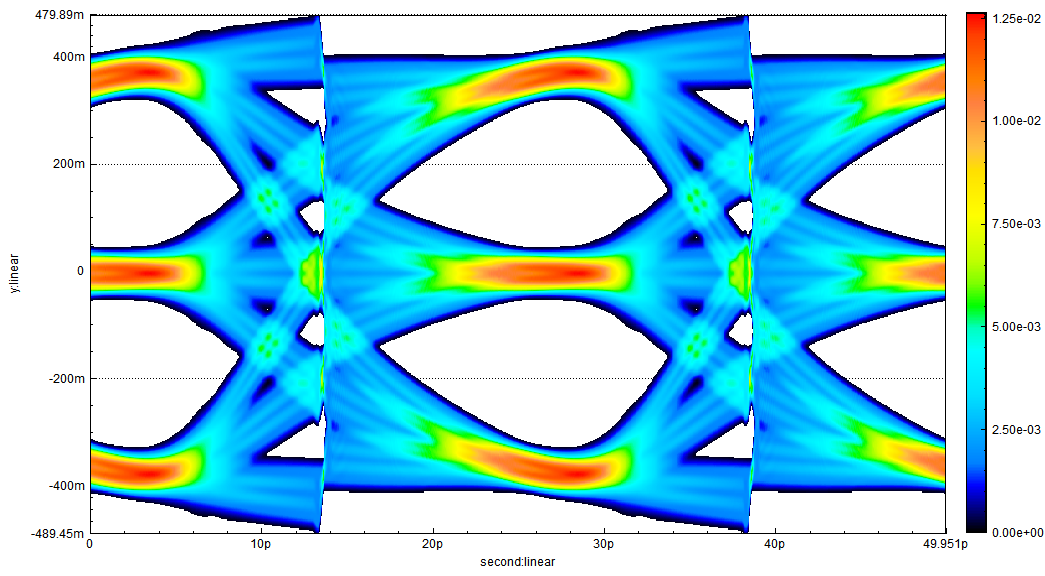

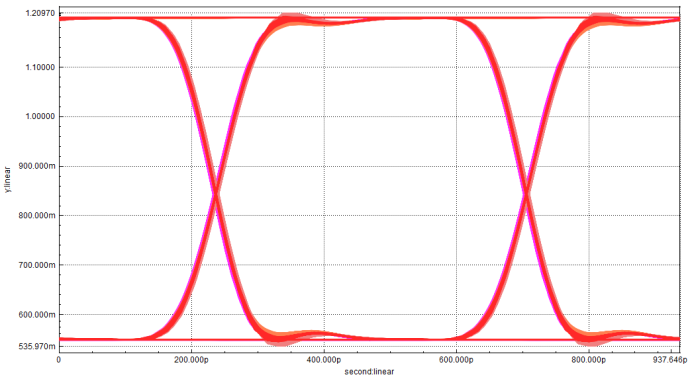

(1) 理想电压源

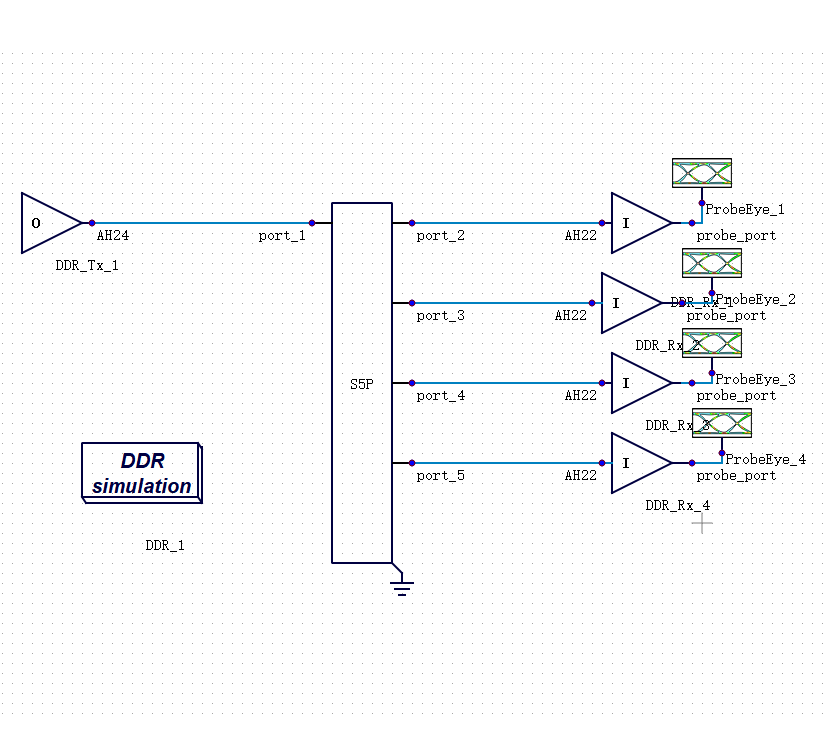

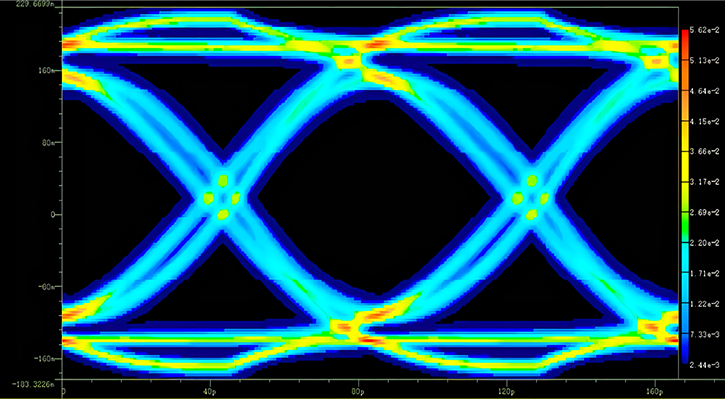

在初始仿真中,我们按照传统方法设置了信号网络和电源网络,但未考虑电源噪声的影响。此时,仿真结果(图中仅展示DQ0-DQ3)表现比较理想。

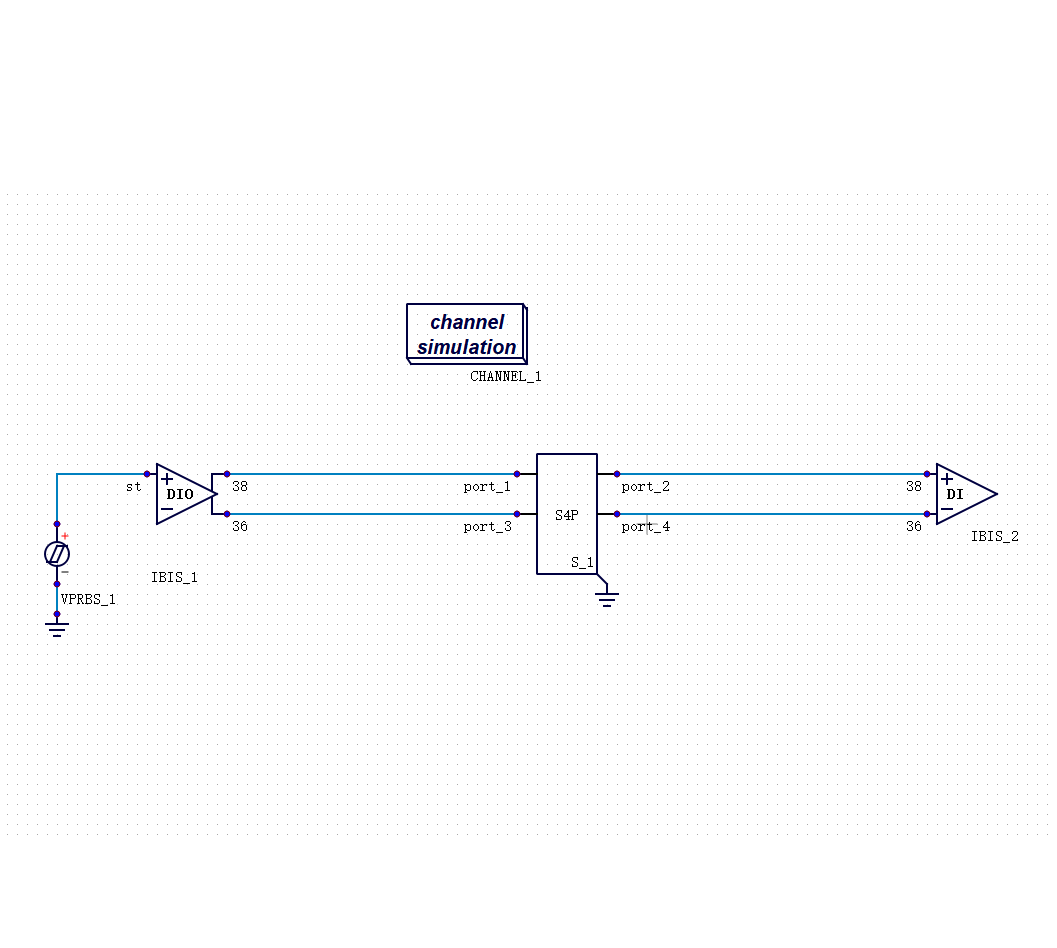

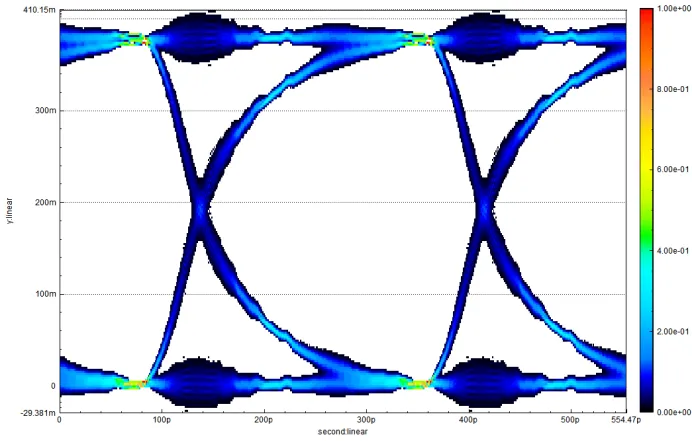

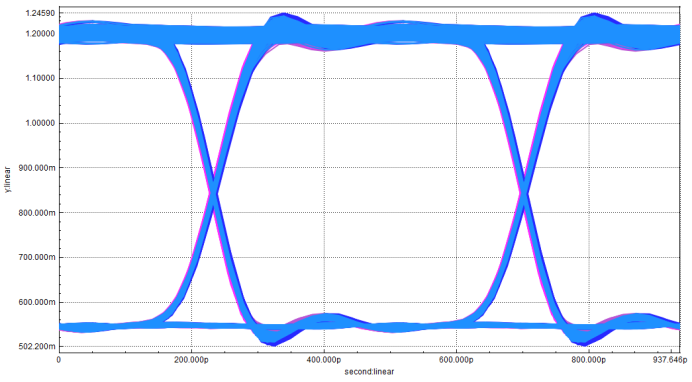

(2) 非理想电压源

在初始仿真中,我们按照传统方法设置了信号网络和电源网络,但未考虑电源噪声的影响。此时,仿真结果(图中仅展示DQ0-DQ3)显示电源噪声增大,信号完整性变差,具体表现为过冲、下冲和抖动增加。

以上可以看出,通过引入了Power-Aware IBIS模型,可以更加真实评估DDR实际运行过程中电源完整性对信号完整性的影响,并且可以通过分析仿真结果,对电源网络和信号网络进行相应的优化调整。例如,增加去耦电容的数量、调整电源分配网络的结构、优化信号路径等,然后再次运行仿真验证优化效果直至满足设计要求。

四、总结

Power-Aware IBIS模型作为一种新型的行为级仿真模型,在电源完整性和信号完整性分析方面具有显著优势。它不仅能够更准确地模拟电源噪声对信号的影响,还能有效减少仿真时间和资源消耗。在实际的数字电路设计过程中,合理运用Power-Aware IBIS模型能够大大提高设计效率和产品质量。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!