SIDesigner实现并行接口信号完整性分析案例

-

2021.08.31

前言

并行接口如DDR、EMMC等在消费类电子以及高端服务器产品中应用越来越广泛,数据速率越来越高。由于并行接口同步切换时各信号之间相互干扰较强,且电流较大,抖动以及电源噪声会造成较大的系统时序损失,而一旦设计完成再发现问题重新设计会造成较大的成本损失。因此在设计前以及设计中对并行接口进行信号完整性、电源完整性分析以确保设计速率满足规格要求是信号完整性工程师的一个主要任务。

进行信号完整性分析一般分为EM仿真器物理建模和用SPICE工具进行系统时序电路分析两个步骤,而在pre-layout阶段,由于缺少具体的layout物理设计,通常选用相近似的PCB或者package设计模型并根据实际情况用传输线模型以及过孔模型来进行评估,从而在设计初期对系统结果有一定预期。SIDesigner作为信号完整性与电源完整性电路级仿真平台,可以在PCB、Package物理模型已有的情况下进行系统级信号完整性、电源完整性分析,或者pre-layout阶段的系统时序性能评估。本案例介绍基于SIDesigner仿真平台的pre-layout阶段并行接口信号完整性分析,案例涉及IBIS模型、S参数模型以及传输线模型等。

一、仿真准备工作

在仿真评估开始前,必须对要仿真对象全貌以及要评估的内容进行充分的准备,所谓garbage-in garbage-out。本案例以LPDDR3为例,对其中的一个byte进行信号完整性评估,准备工作如下:

1、DDR接口速率:简单起见以1Gbps为例。

2、DDR TX/RX IO模型:以下为例,TX为controller,需控制芯片IP提供商提供IO模型,RX为DRAM,需要DRAM厂商提供对应的IO模型。

3、Channel模型:封装模型由DRAM、controller厂商提供,PCB由于还未设计,以接近设计的传输线模型代替。

4、电源模型:在pre-layout阶段评估,以理想电源代替,暂不考虑电源噪声的影响。

以上准备工作就绪后,即可开始在SIDesigner中进行系统级信号完整性仿真工作。

二、SIDesigner进行并行接口信号完整性仿真具体步骤。

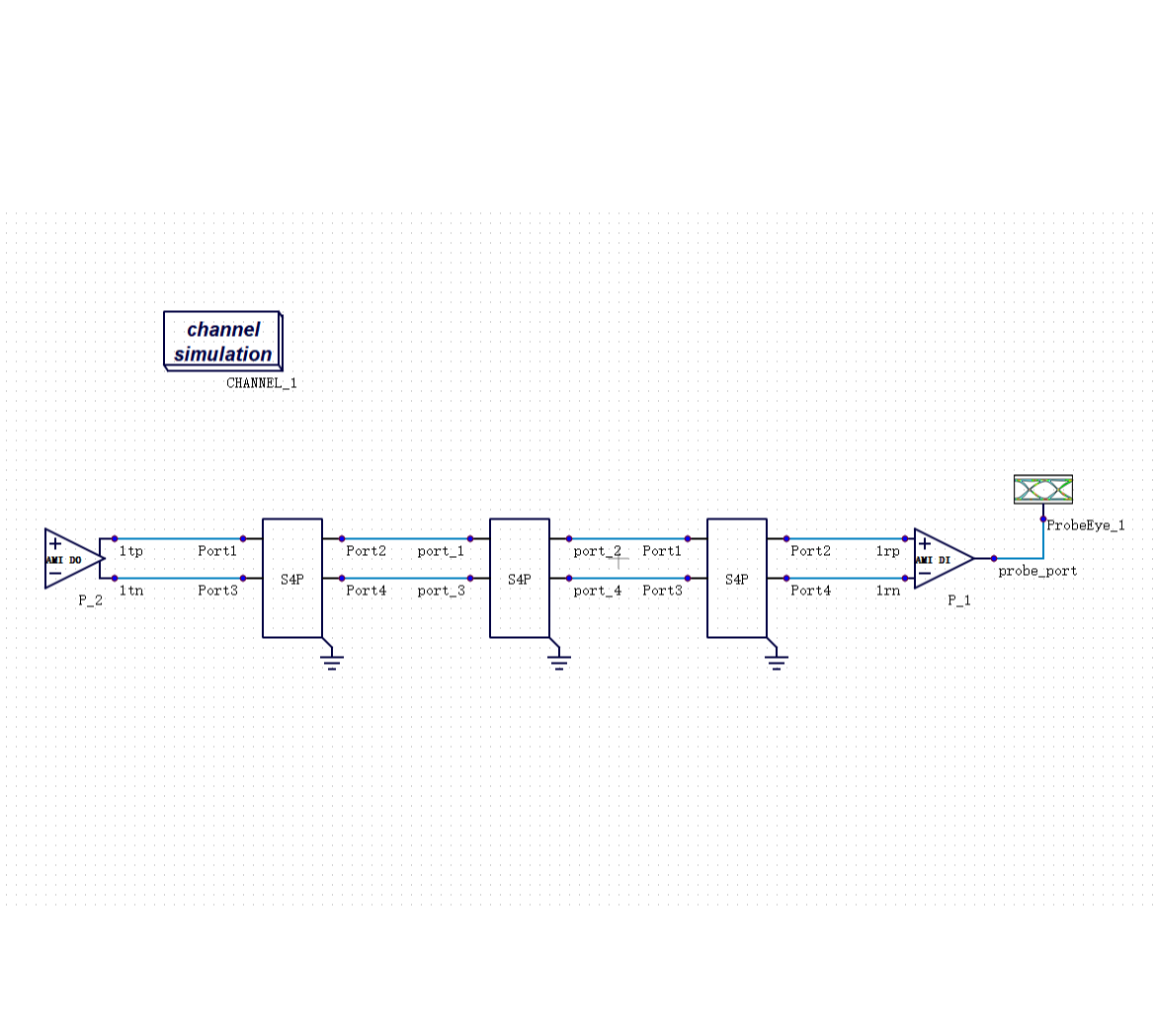

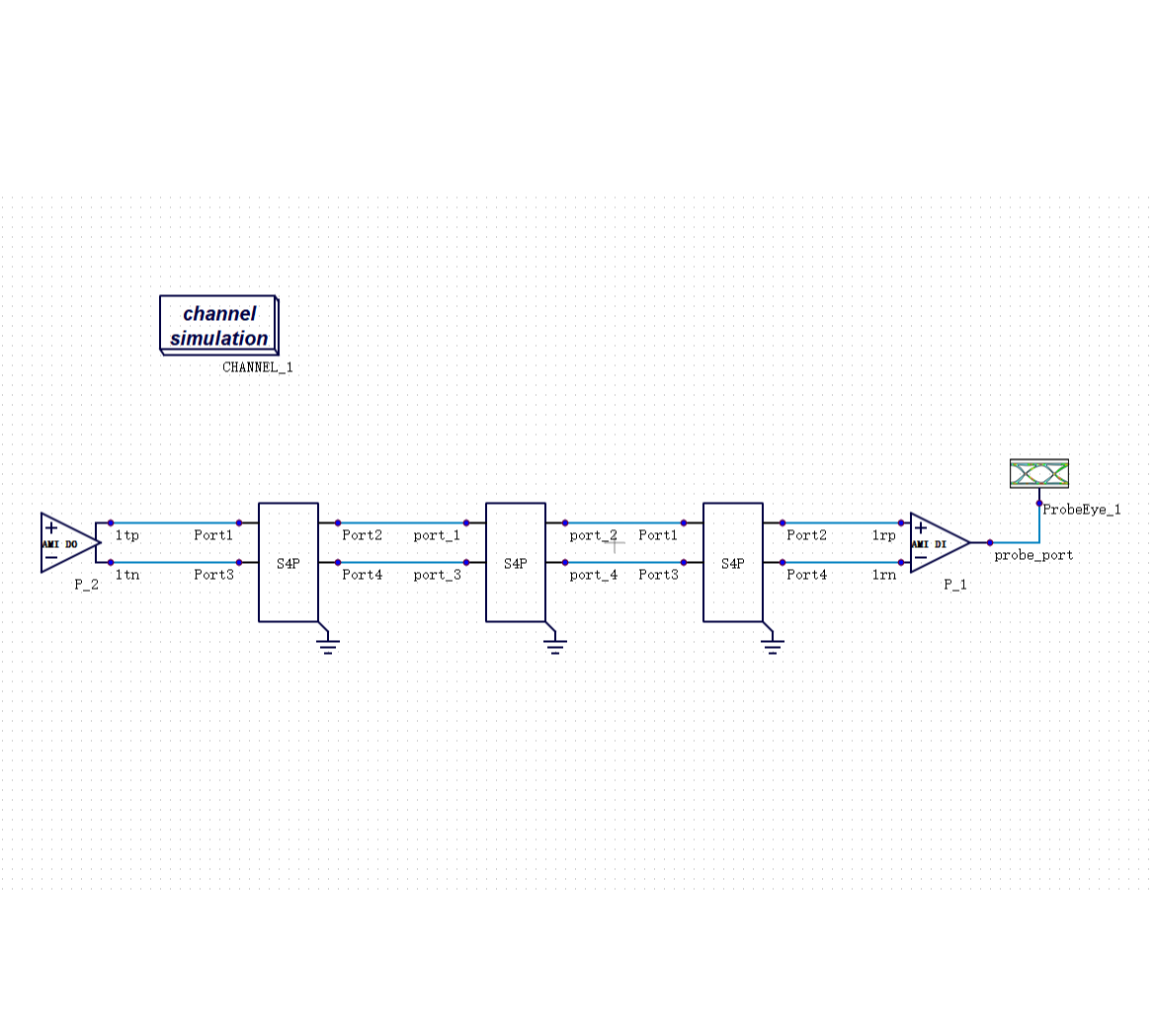

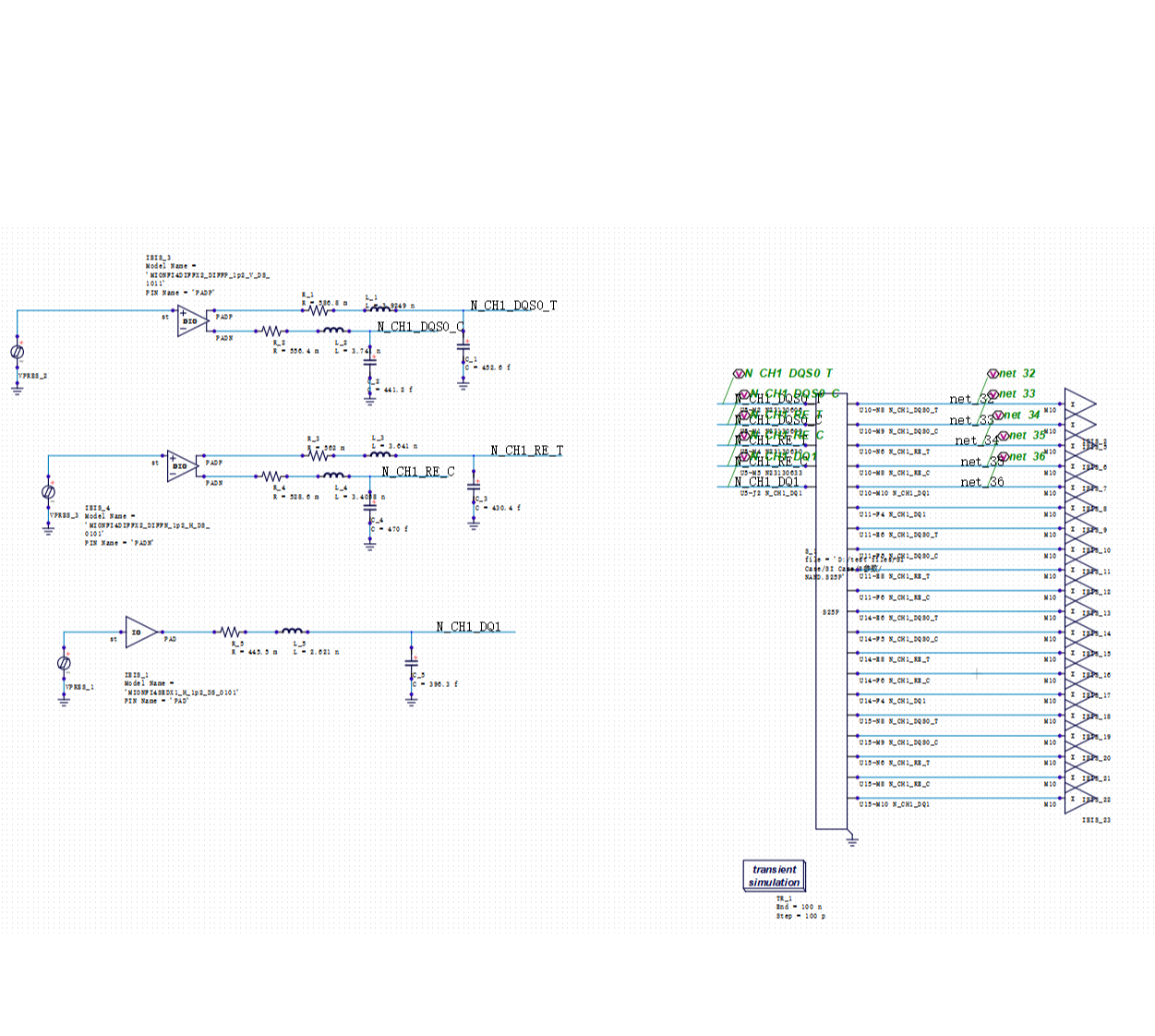

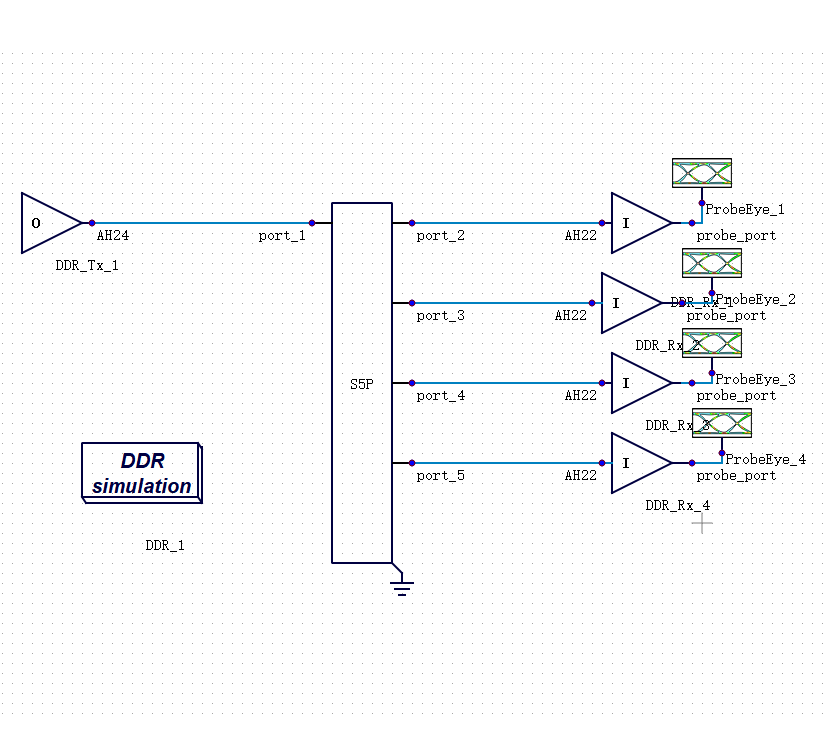

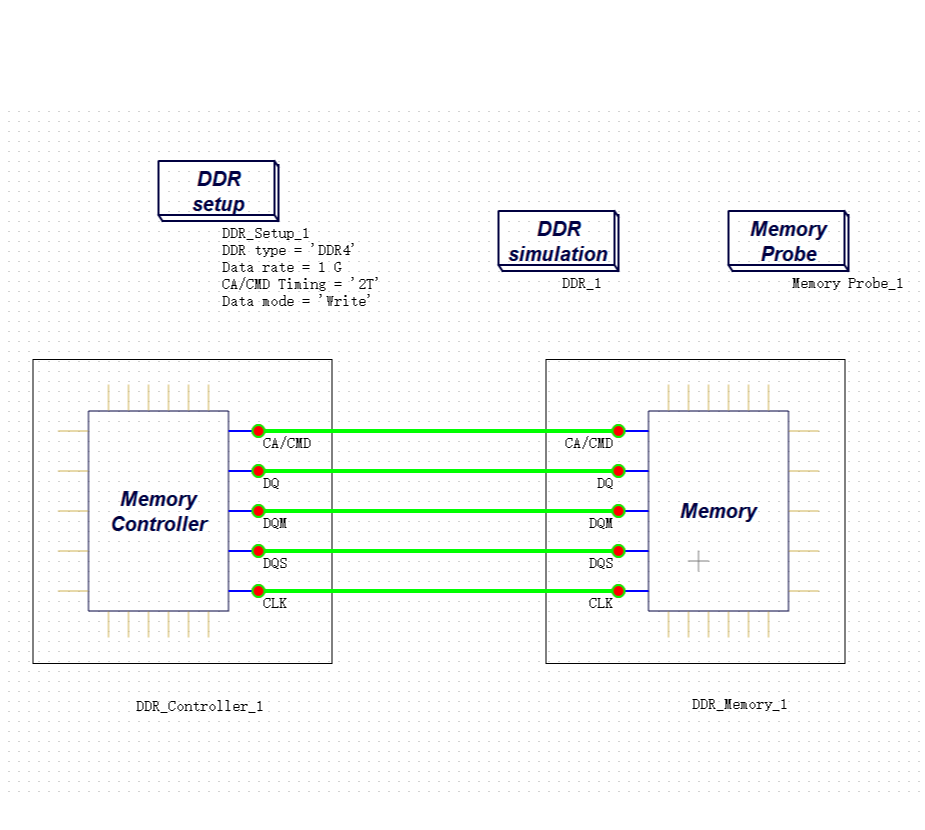

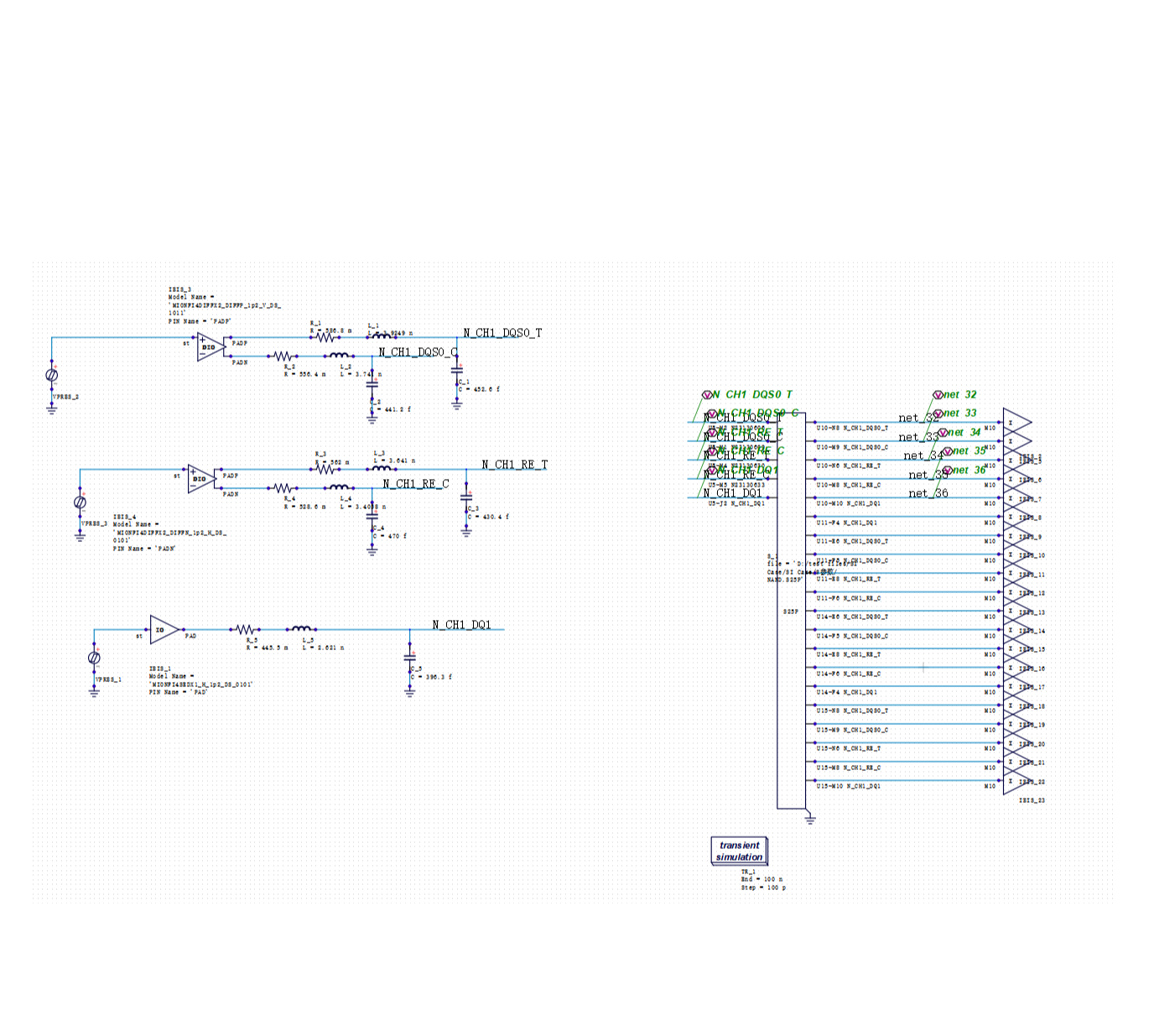

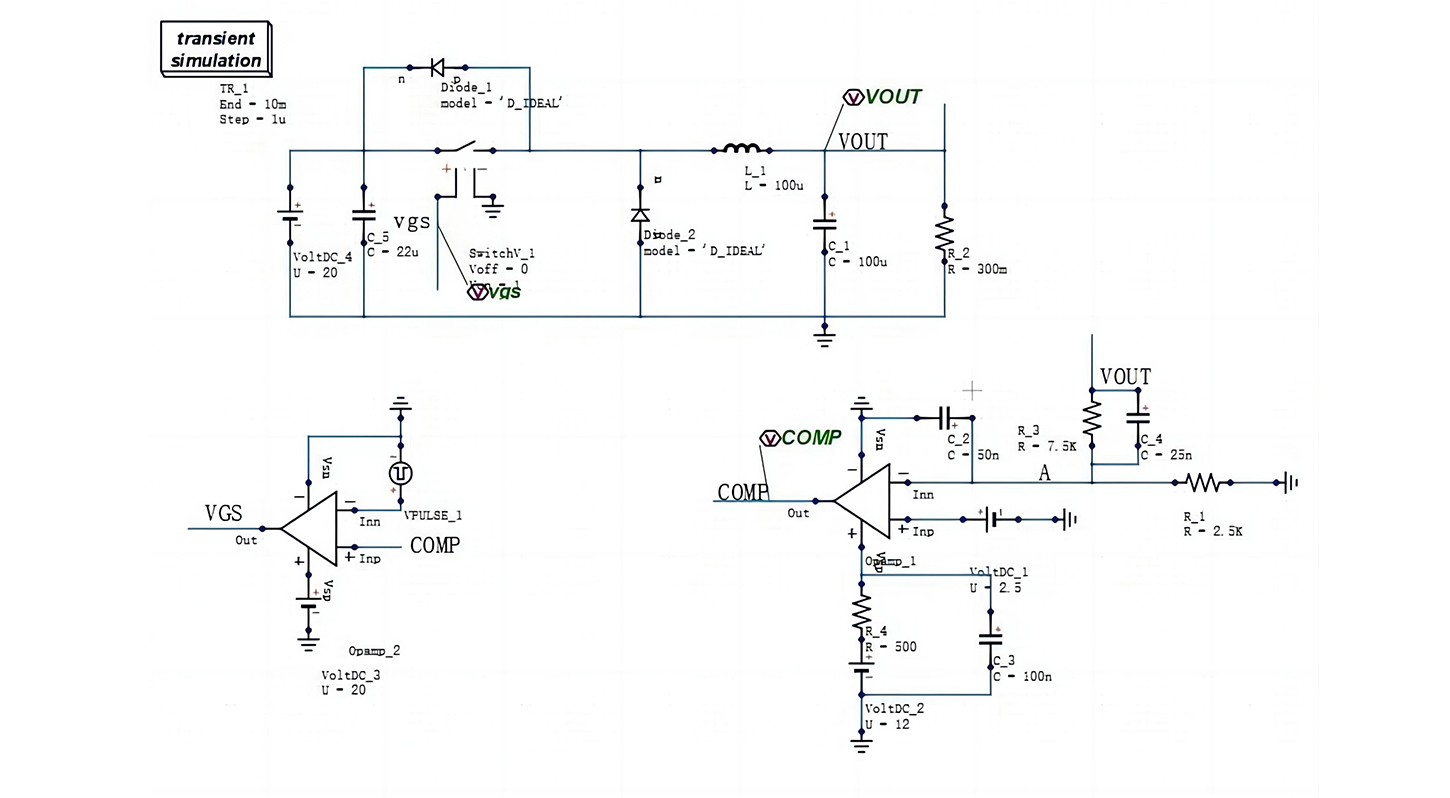

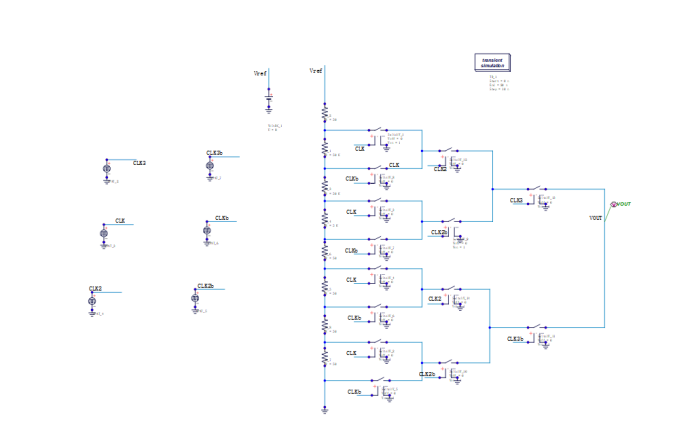

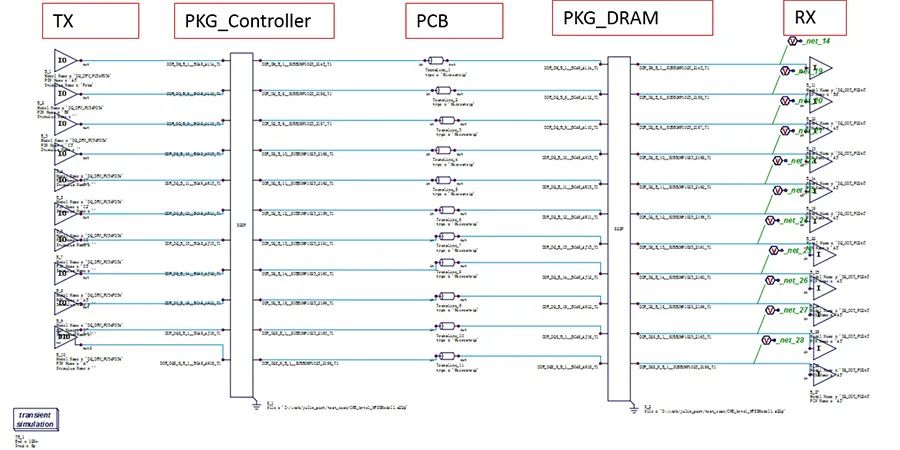

本案例的最终电路结构图示如下,下面将分步介绍案例在SIDesigner中的创建过程。

图1 案例整体电路图

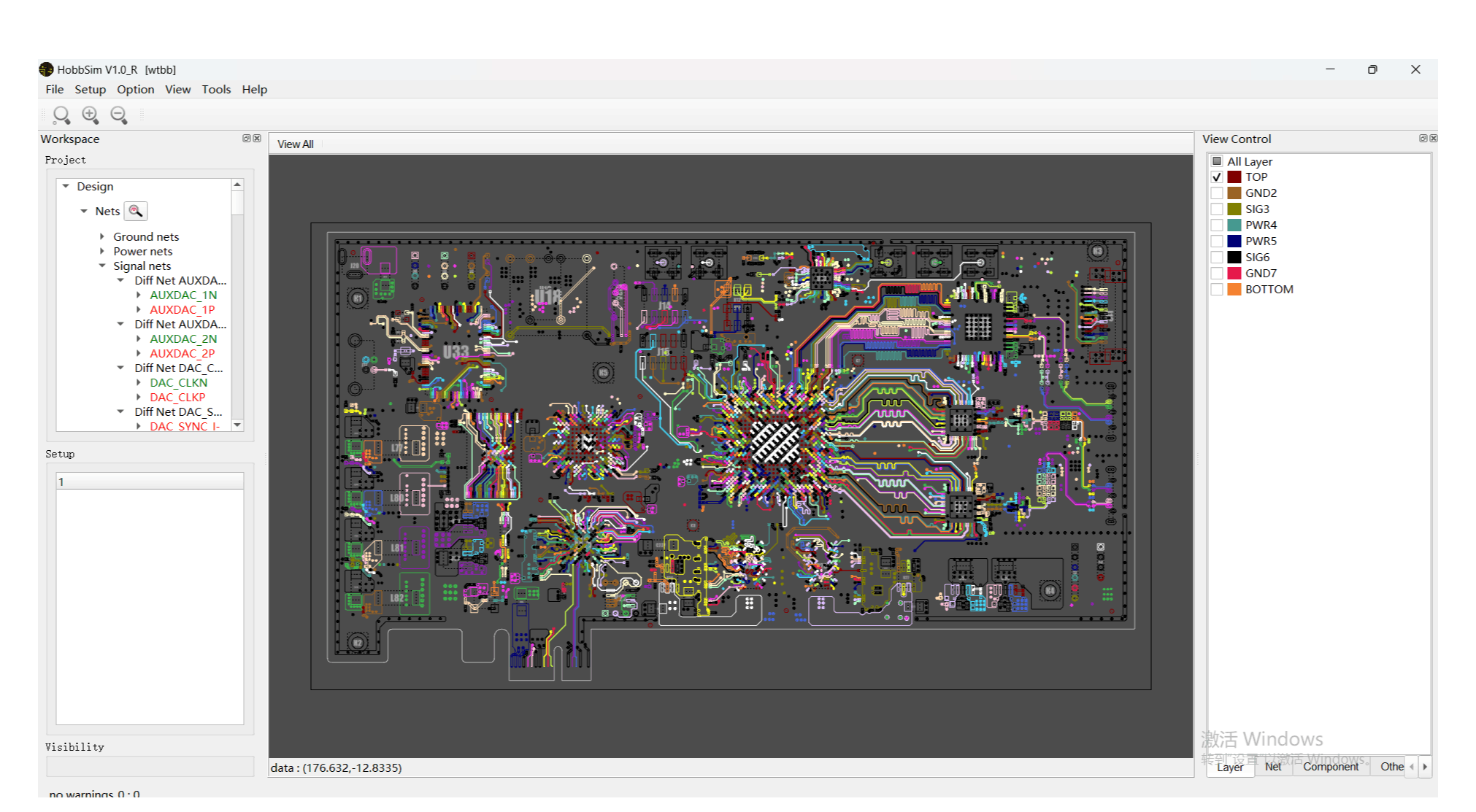

步骤一:工程创建

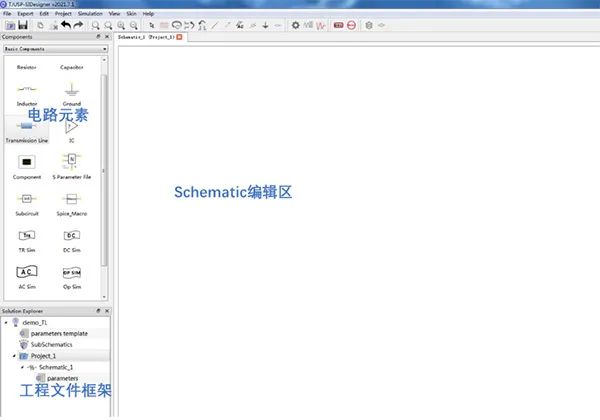

Step 1:SIDesinger中需要先创建Solution,然后创建Project,并进行命名。在Project下面,可以创建具体的电路schematic。

通常在创建完成后,首先设置仿真所用的S参数模型及IO IBIS模型所在的路径,以便后续设置时快速获取。

图2 新建工程

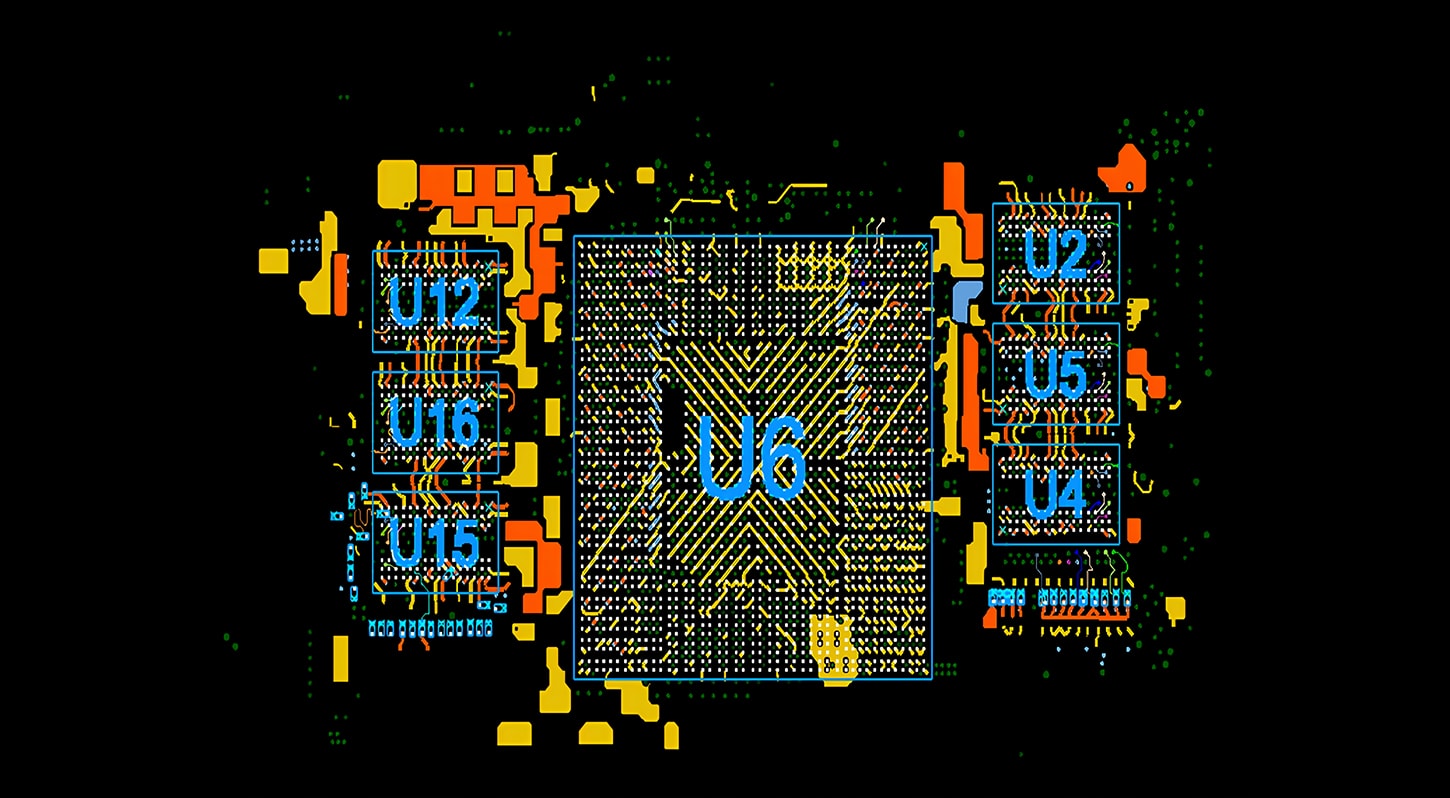

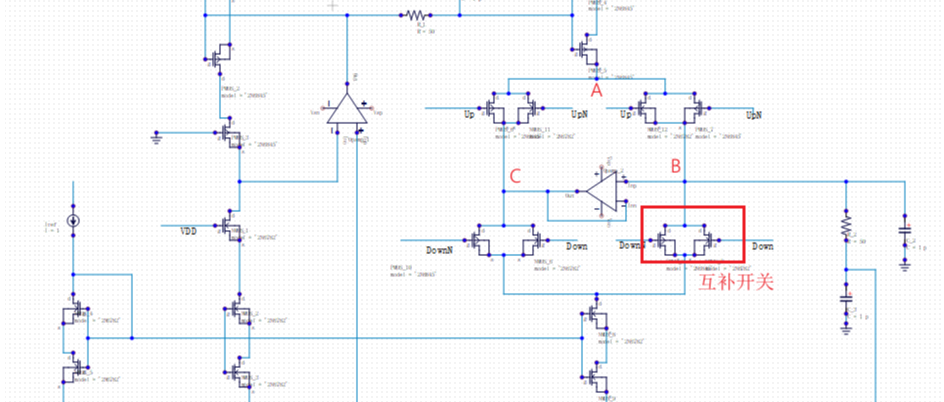

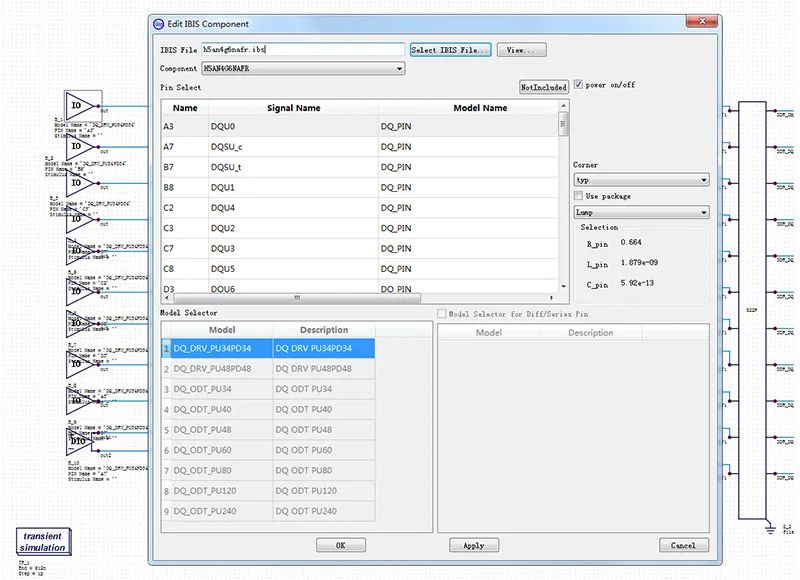

Step 2:IO模型实例化

放置IO buffer模型并进行模型实例化:导入IBIS文件,选择相应的component,然后选择pin及对应的IO model,逐一完成IO实例化。注意需要对发送端和接收端设置响应的Output和Input模型。图示为Output模型,驱动选择34ohm。

图3 IO模型实例化设置

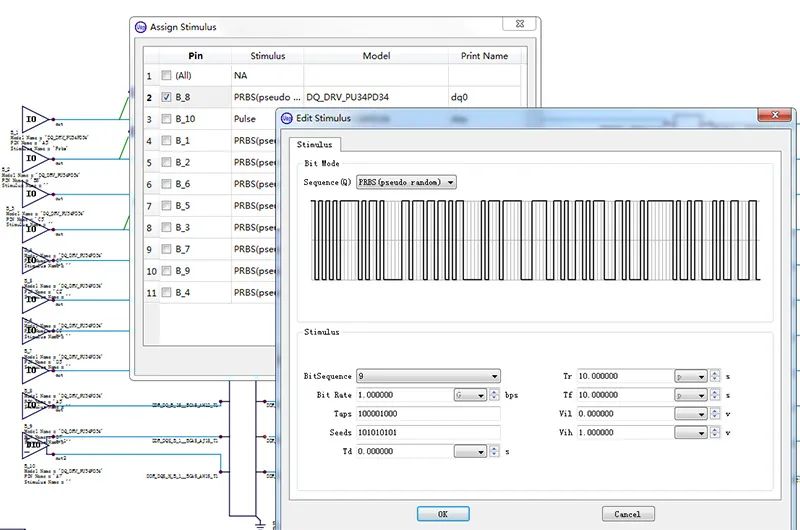

Step 3:信号激励设置

IO模型实例化结束后,即可对发送端的IO设置激励波形。SIDesigner支持各种类型的激励设置,包括PRBS、PWL、Pulse、PAT以及各种基于文件输入的形式。在DDR接口仿真中,通常DQ信号用PRBS激励,而DQS信号用PULSE激励。

需要注意的是对于DDR接口来说,DQ、DQS之间根据SPEC的需求有响应的延时,在设置仿真激励时必须予以考虑。

图4 IO激励源设置

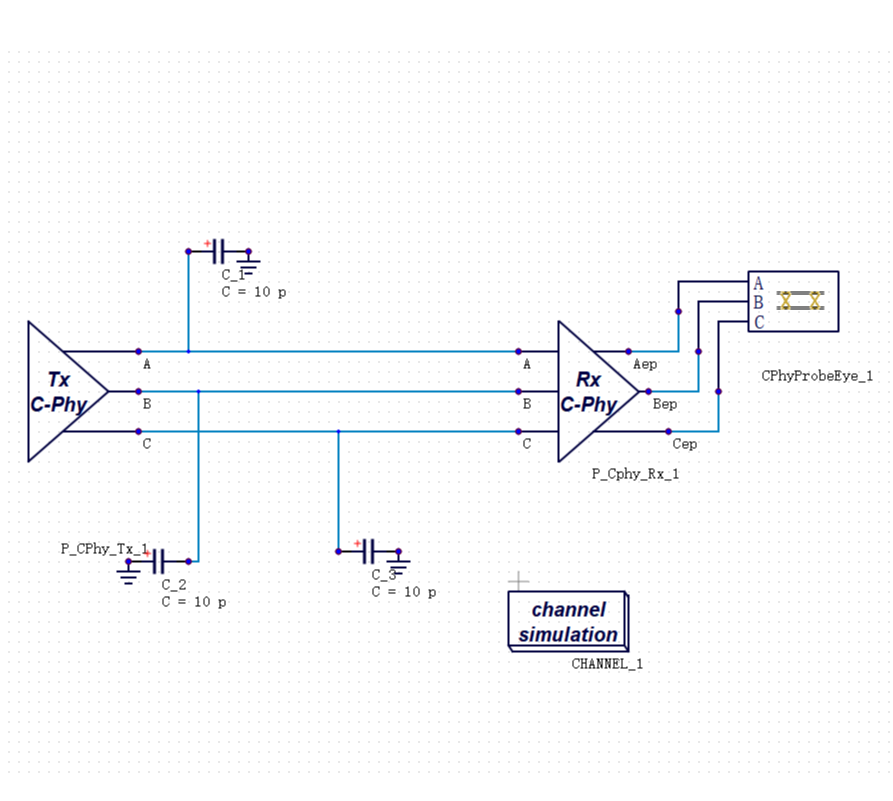

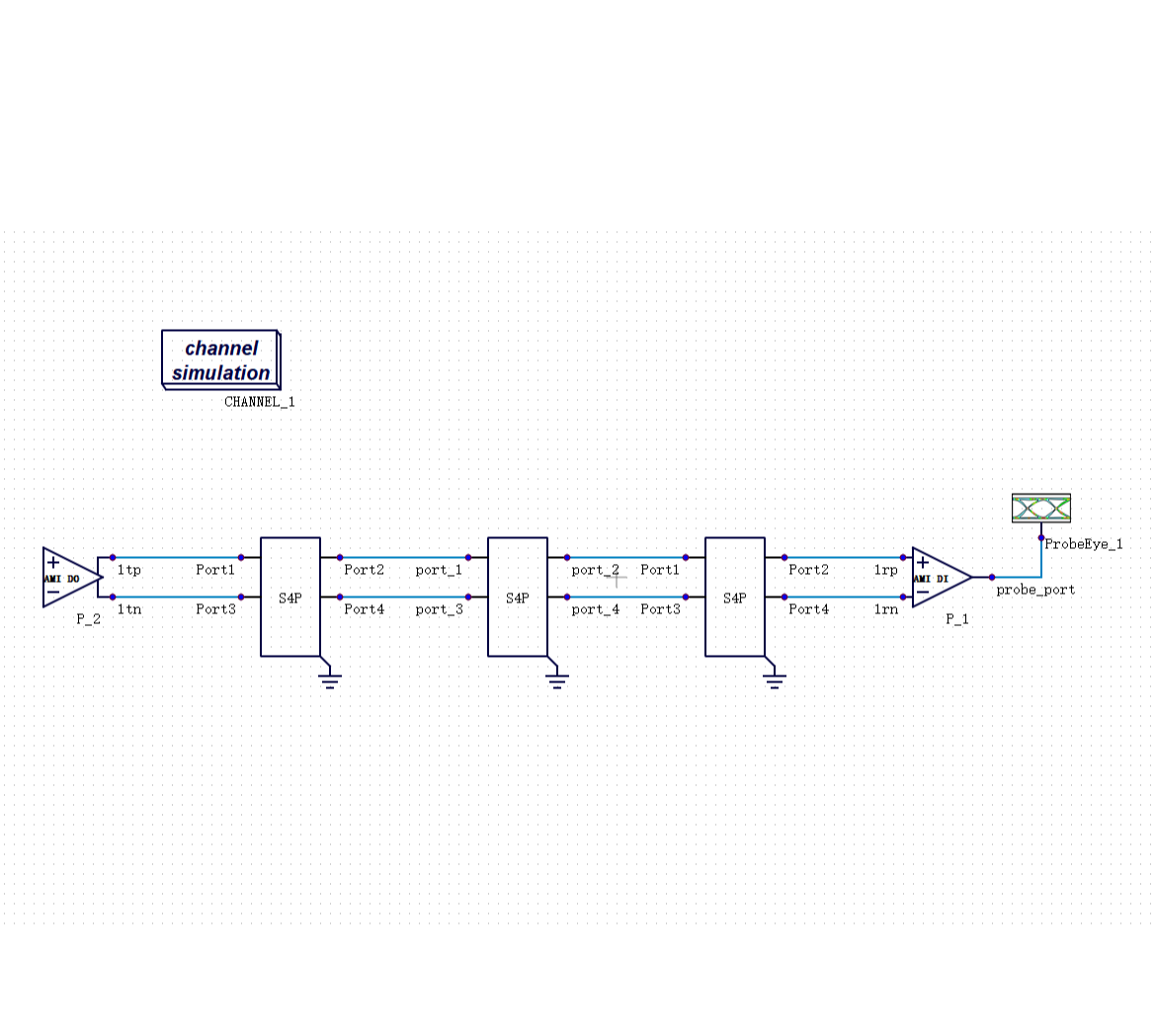

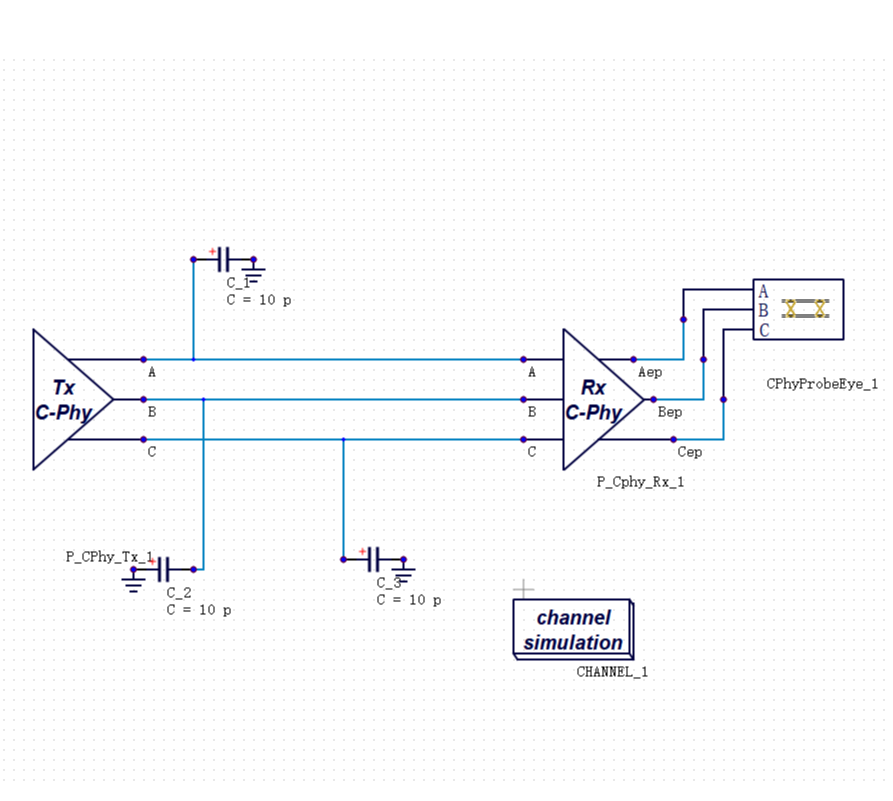

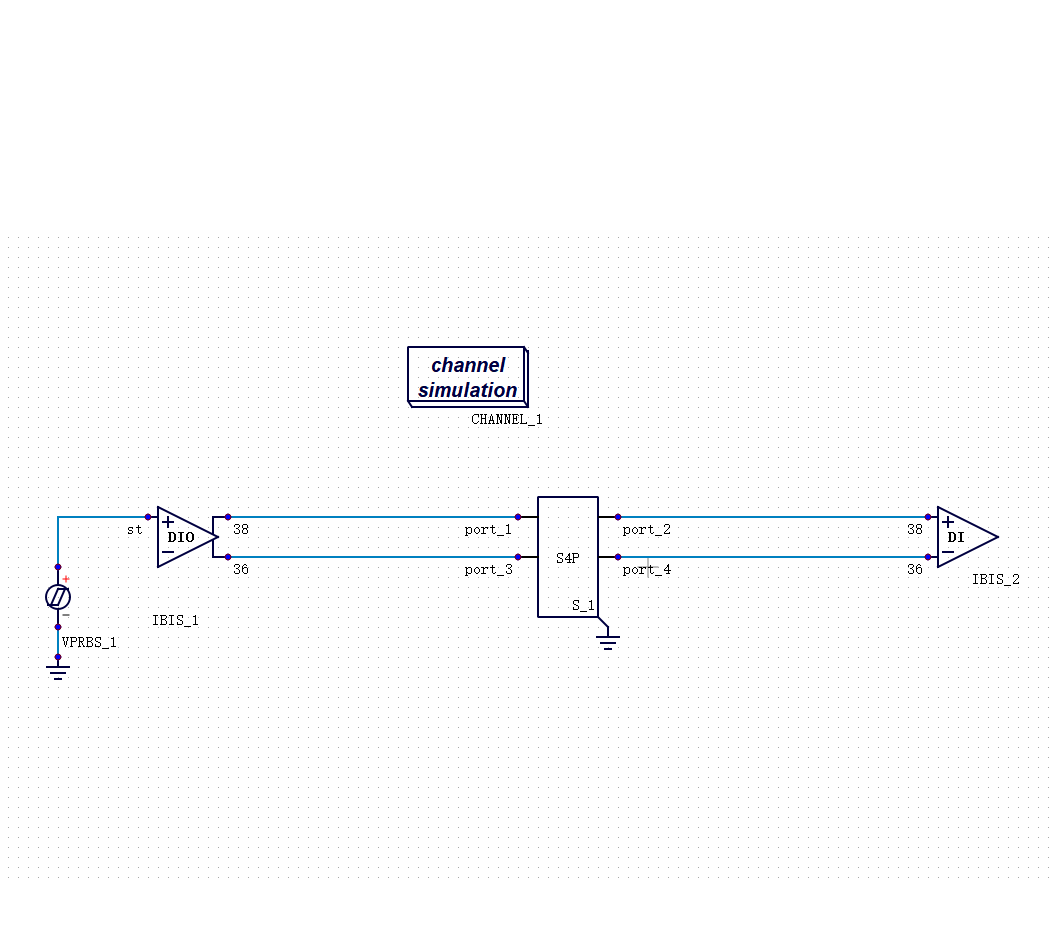

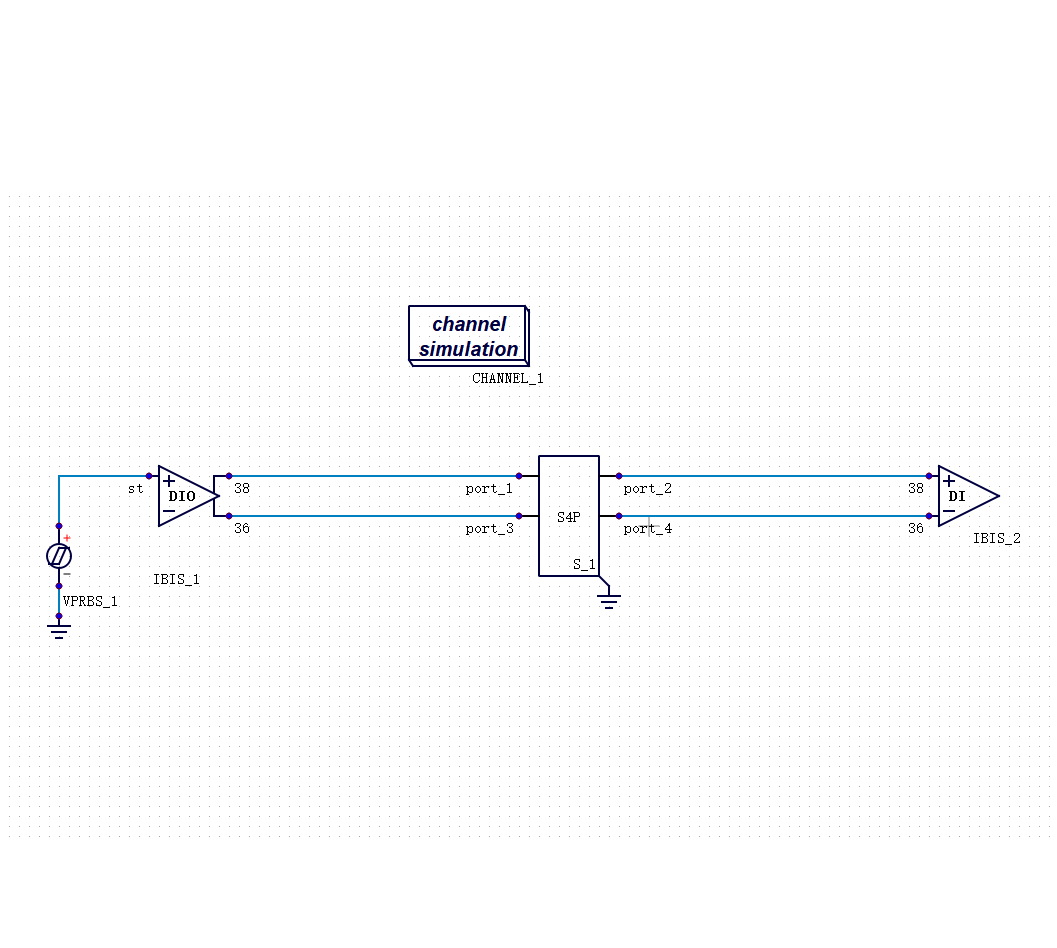

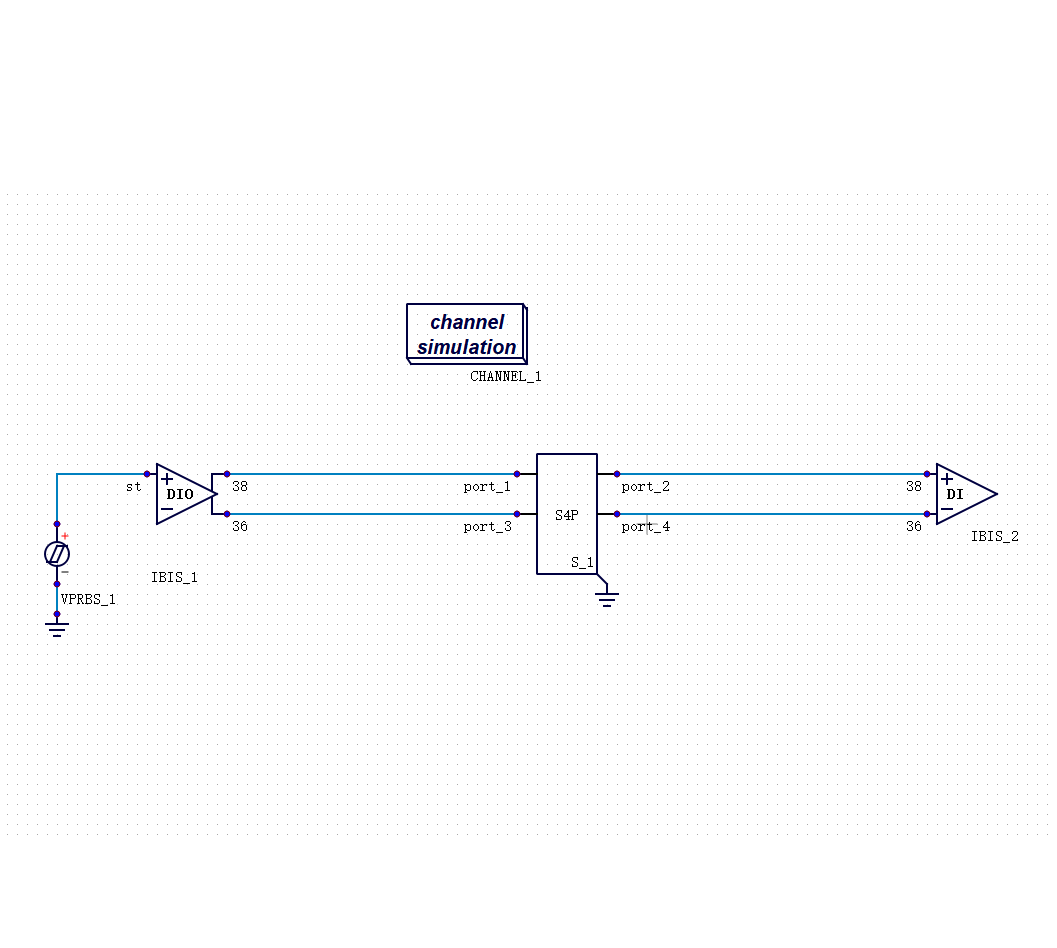

Step 4:Channel模型创建

信号完整性仿真中Channel一般由S参数或者响应的宽带电路模型组成。在pre-layout阶段也可有传输线以及过孔模型作为补充。

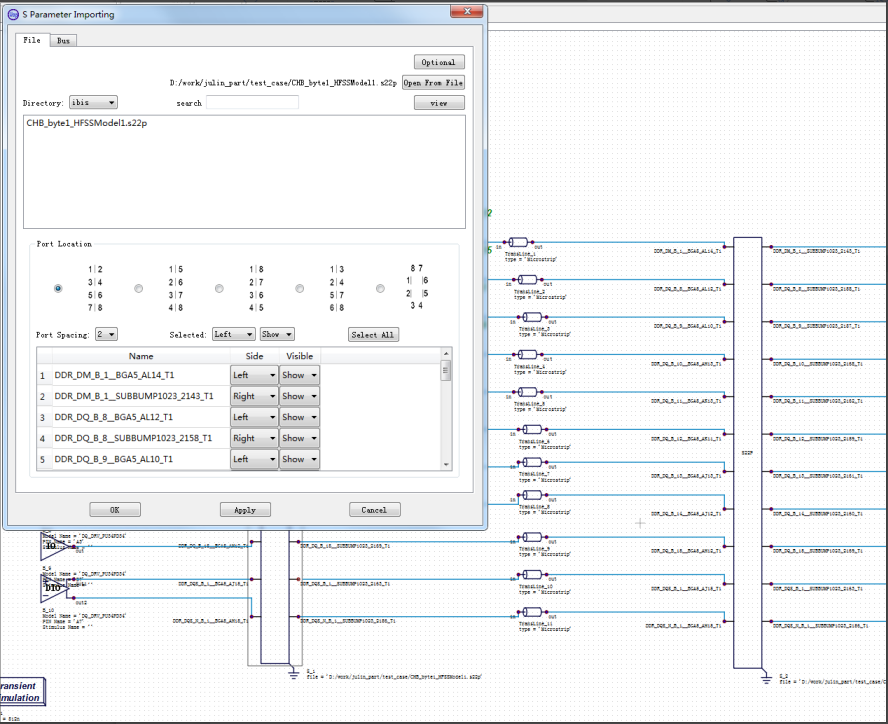

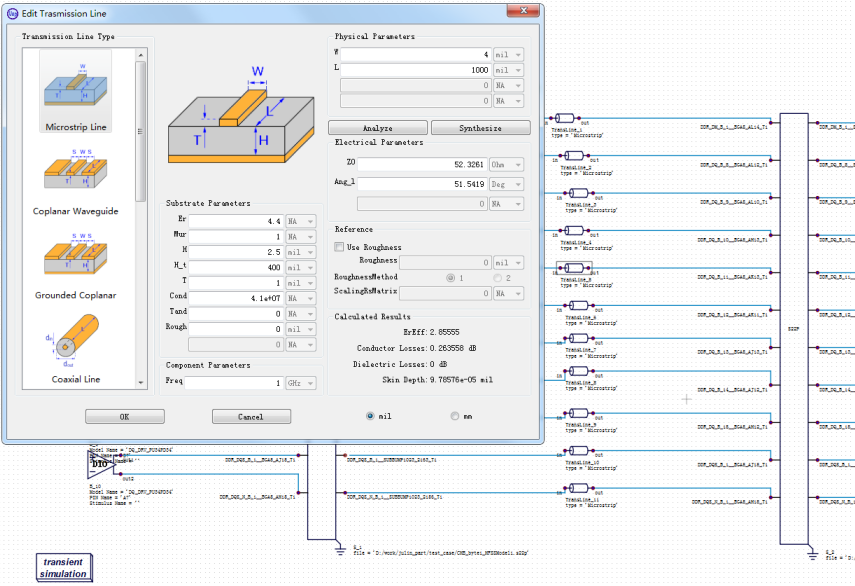

本例即为S参数和传输线组合而成。

图5 S参数模型导入设置

图6 传输线模型设置

Step 5:仿真设置

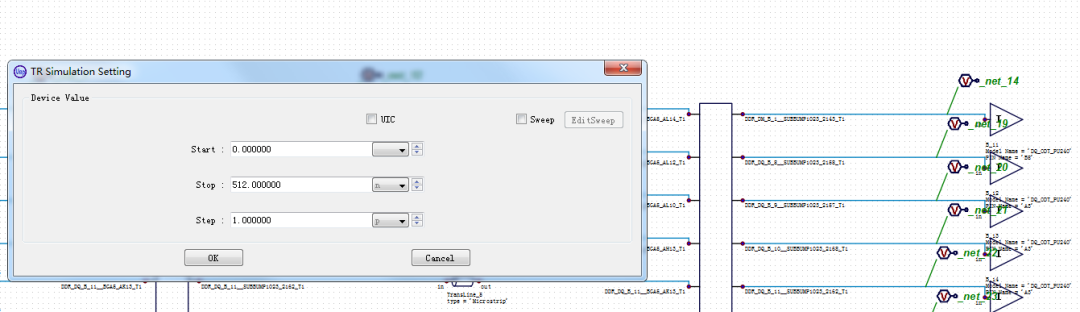

系统电路搭建完成后,需要添加波形/眼图观测点以及瞬态仿真控制,如下图:

图7 时域仿真设置

仿真时间以码型长度*UI来衡量,观测点一般以激励点和接收端输入点作为必选点。

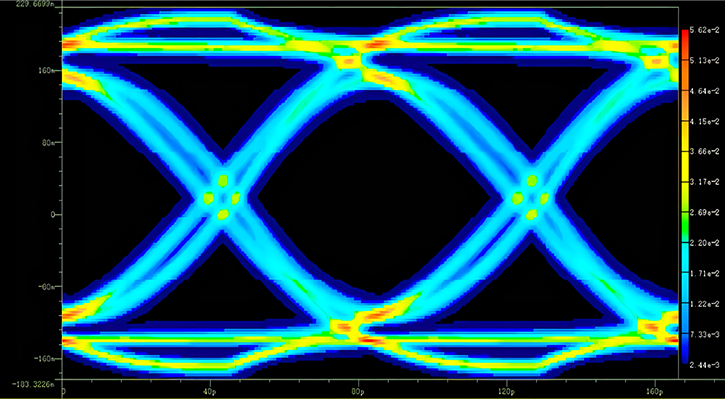

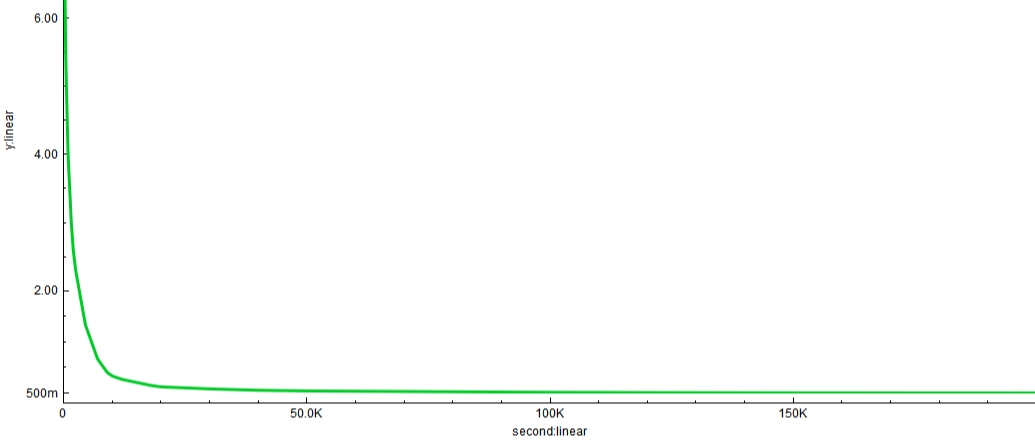

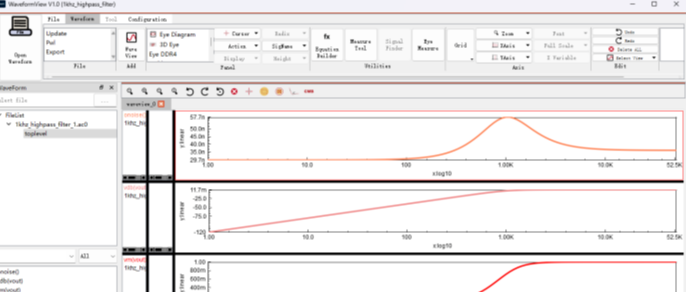

Step 6:波形查看及后处理

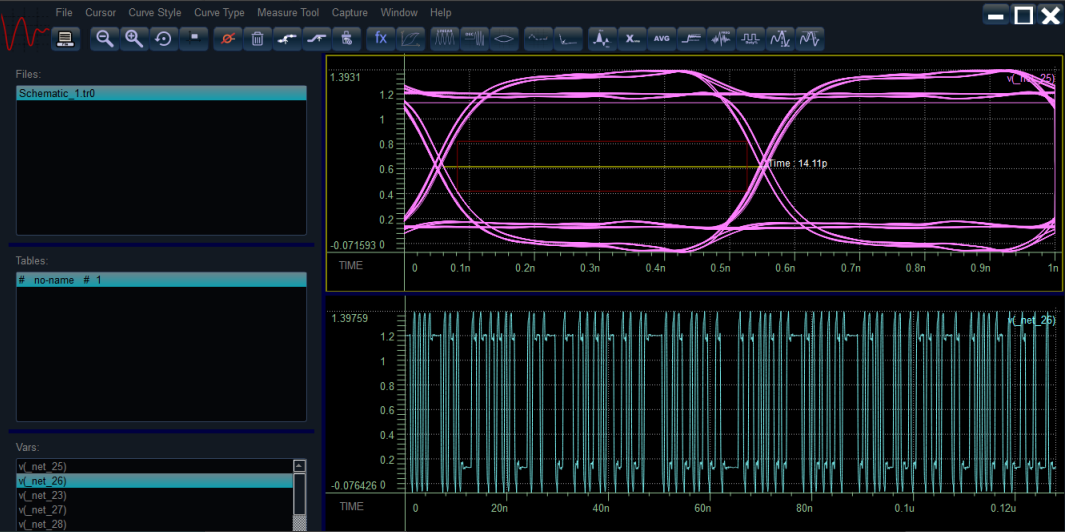

仿真结束后,SIDesigner内嵌的波形处理器自动允许导入生成的波形,用户可以对仿真结果进行后处理以及测量。

图8 仿真结果查看及后处理

三、总结

本文以一个简单的DDR仿真案例来介绍如何在SIDesigner中完成并行接口的信号完整性分析。作为一款以信号完整性为重心的通用电路仿真软件,SIDesigner能完成除3D EM建模之外的所有SI/PI相关工作。用户可以在SIDesigner中方便的进行各种假设性分析以挖掘设计优化方向。

欢迎点击 软件试用 (yongsy.net) 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

文中部分图片来自网络,如有侵权,请联系删除,谢谢!