Julin Released SIDesigner - a Signal Integrity Simulation Platform

-

2021.11.29

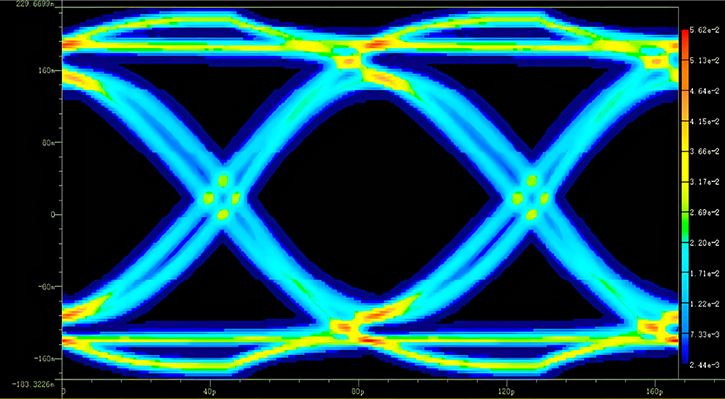

With the vigorous development of the chip industry, the market's demand for a higher data transmission rate is increasing. Signal Integrity (SI) is a field to analyze the quality of signal transmission, that is, to ensure the complete transmission of signals in the interconnected circuit, so that the performance of the chip is not corrupted. Nowadays, the signal rate goes up to double-digit Gbps, and the signal wavelength is smaller than the geometrical size. When the signal is transmitted by electromagnetic waves, the reflection, propagation and interference of the waves must be taken into consideration. The high-frequency phenomenon generated during signal transmission has become a nonnegligible factor in the signal integrity design. Therefore, the result of chip design needs to be tested, verifying whether the power, performance, and reliability configured are fully met in the specific implementation process. This is also the foundation for the design to meet expectations.

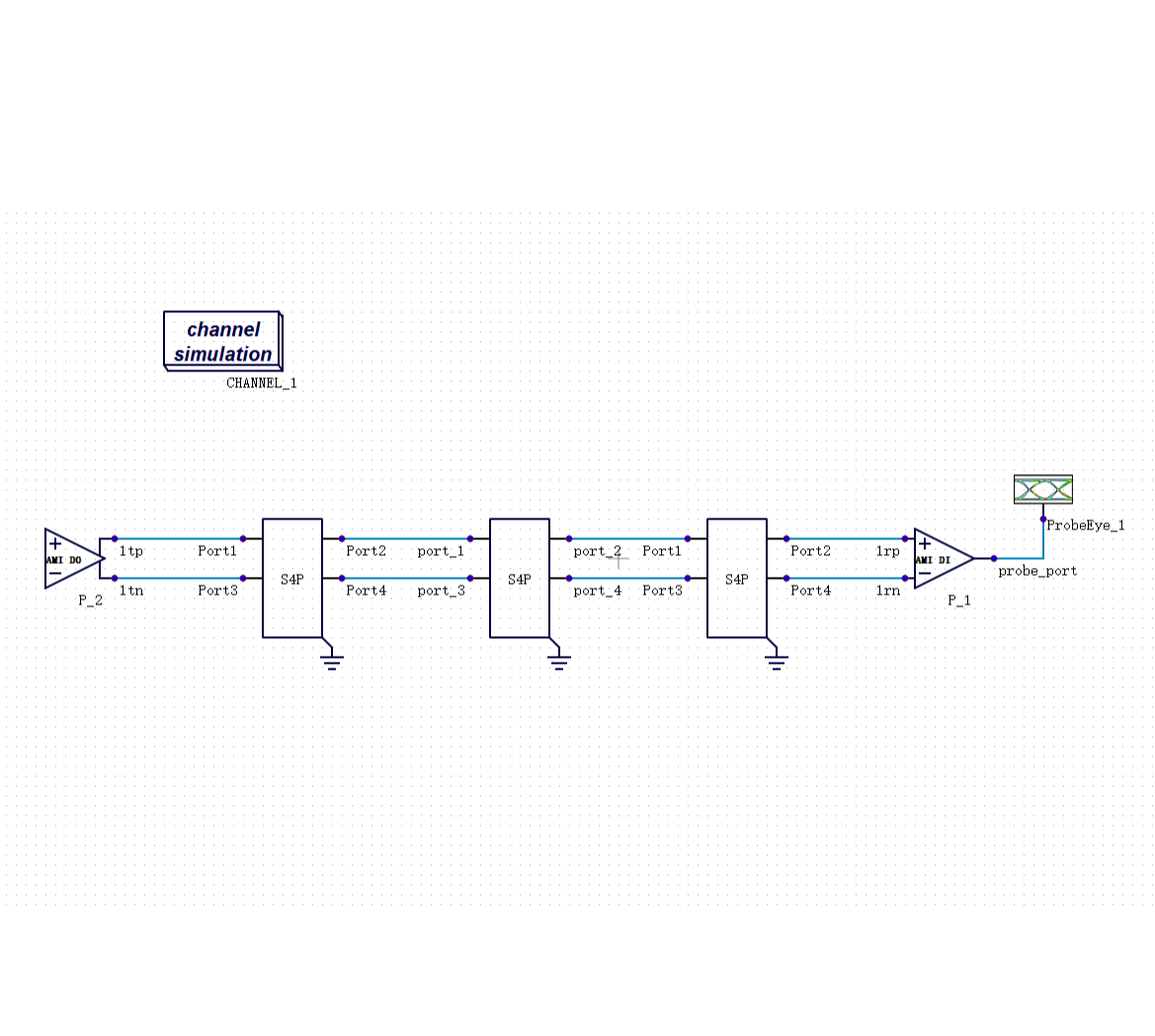

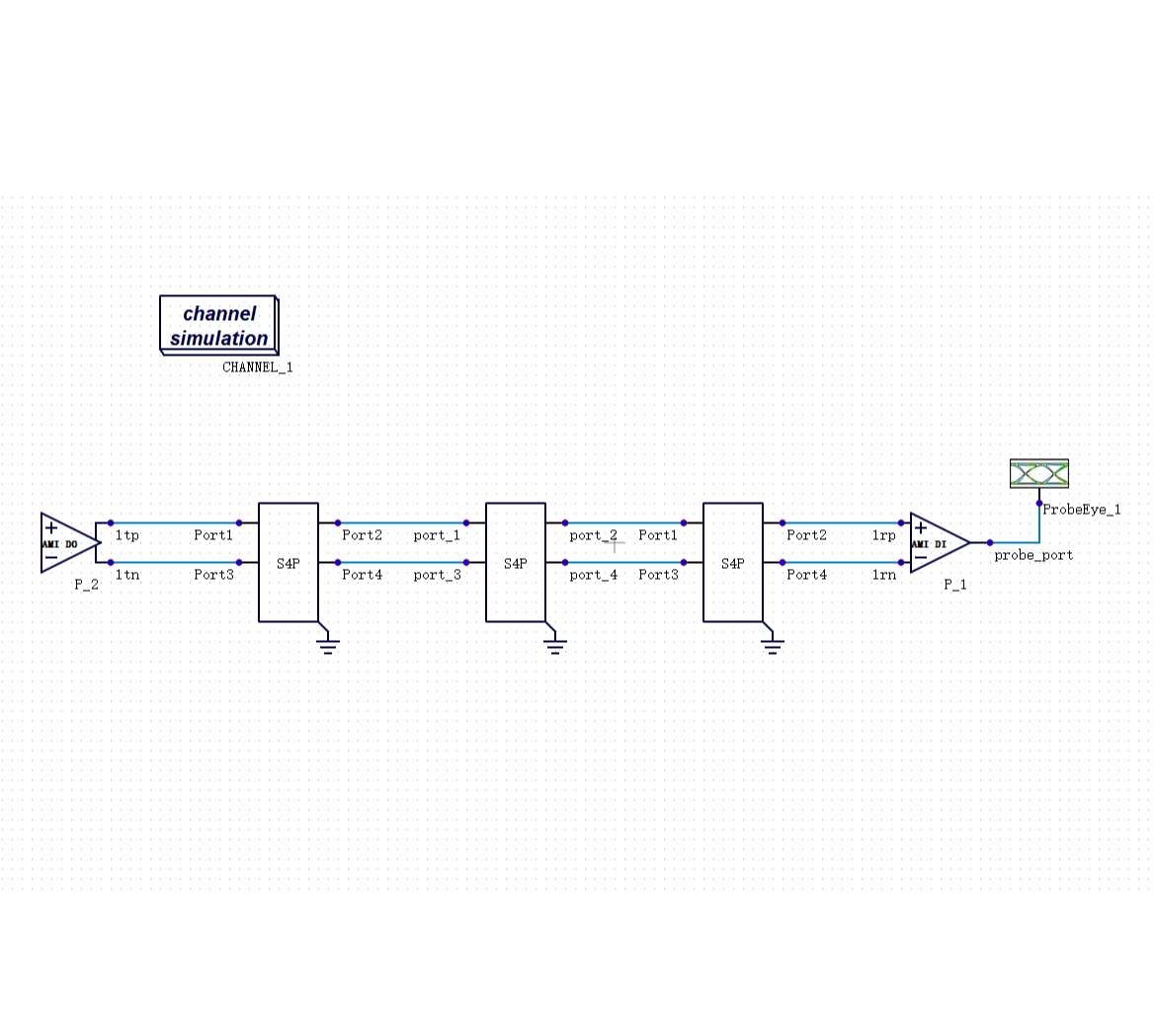

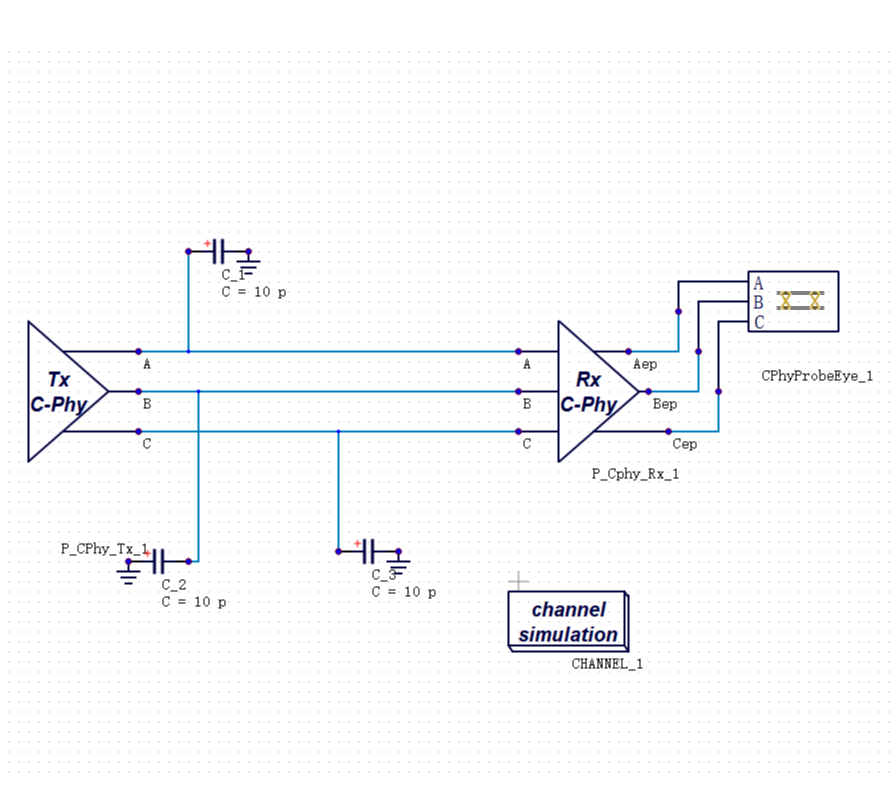

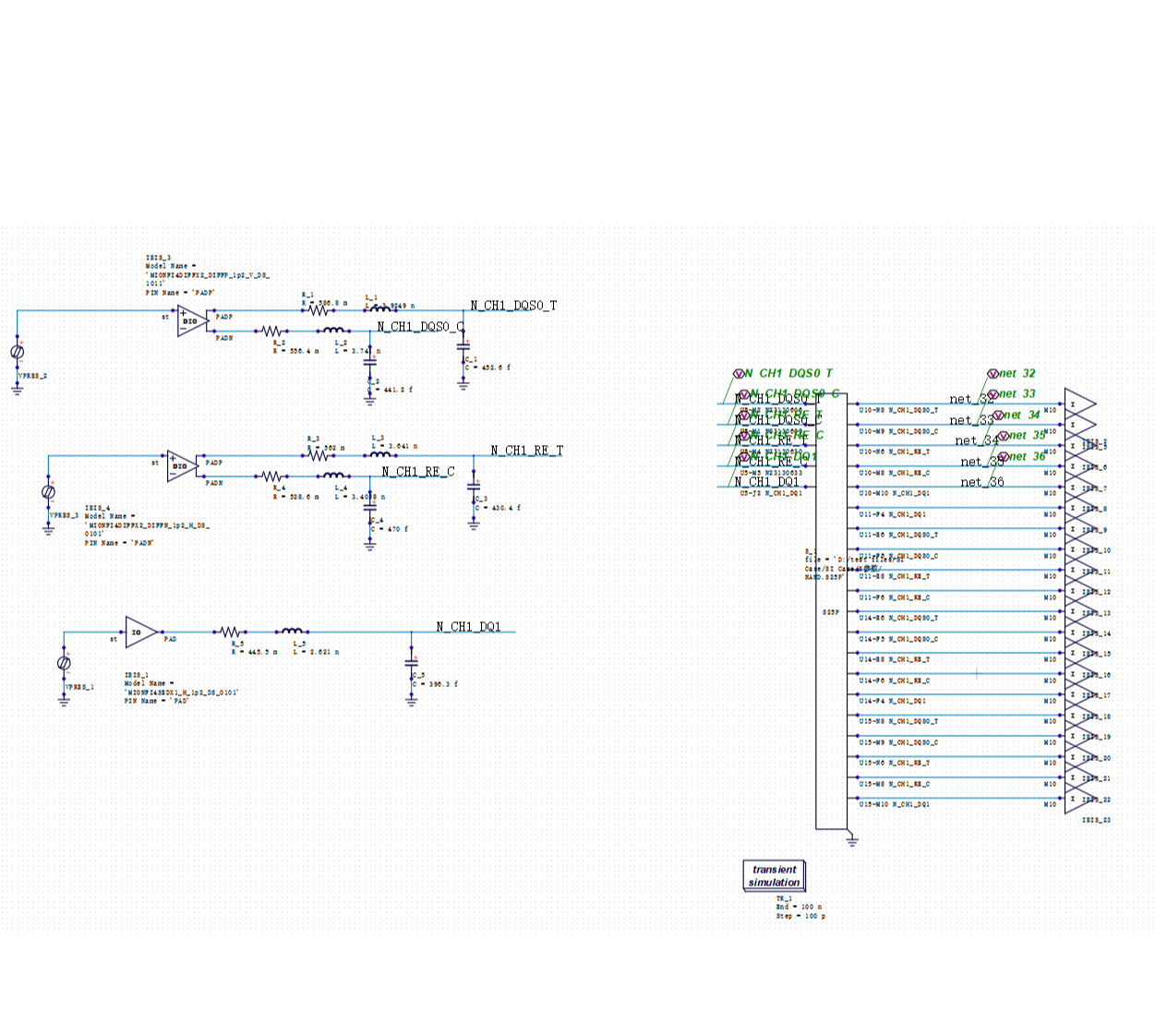

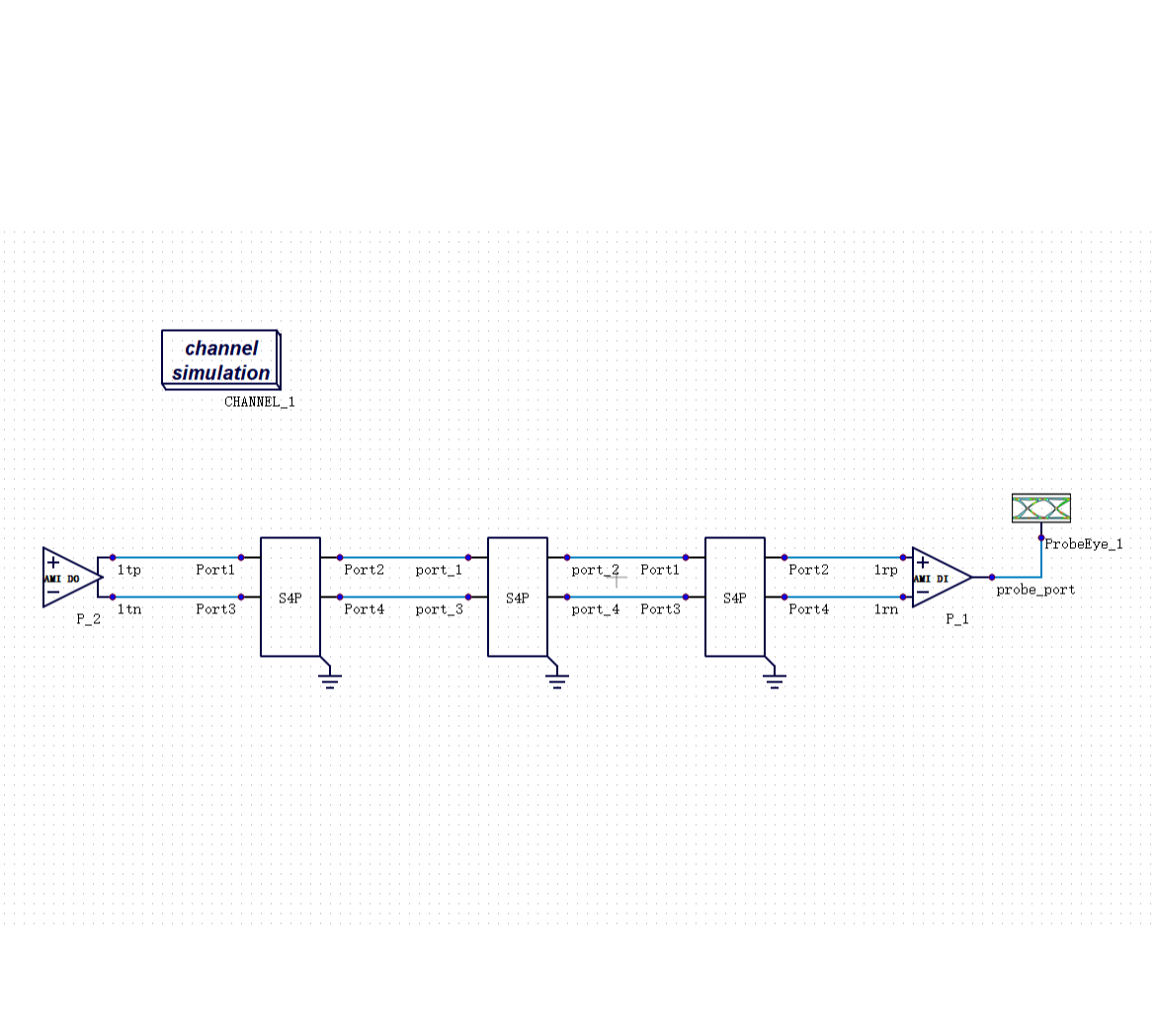

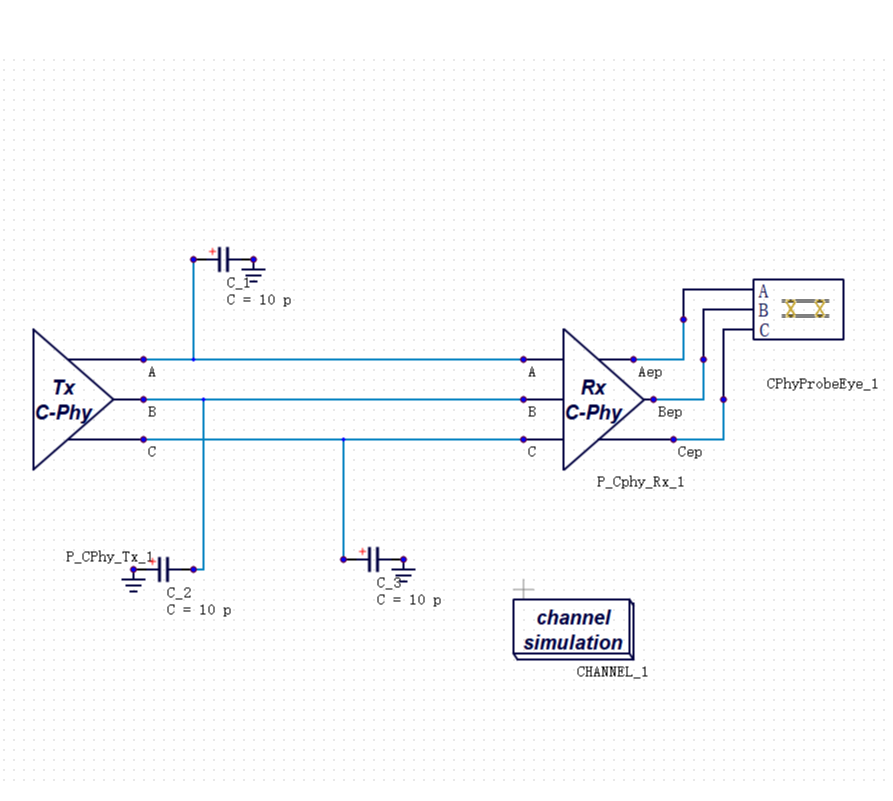

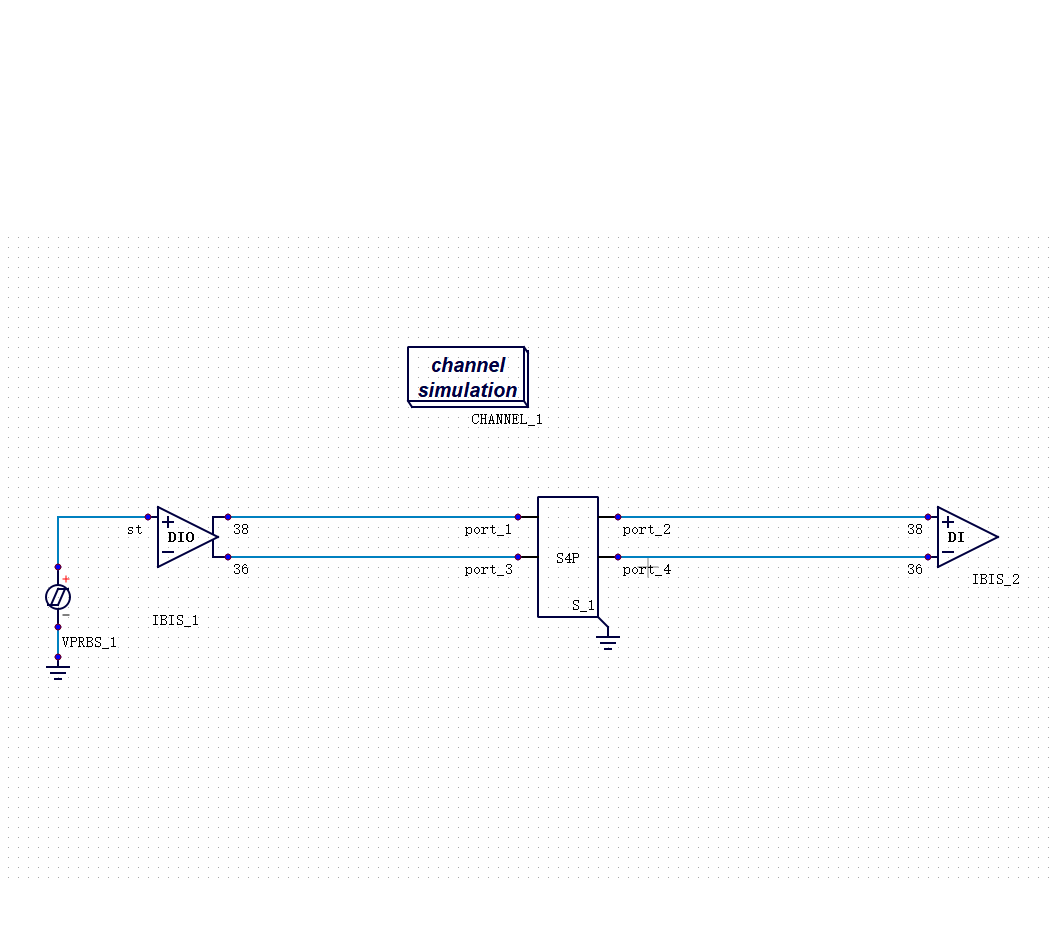

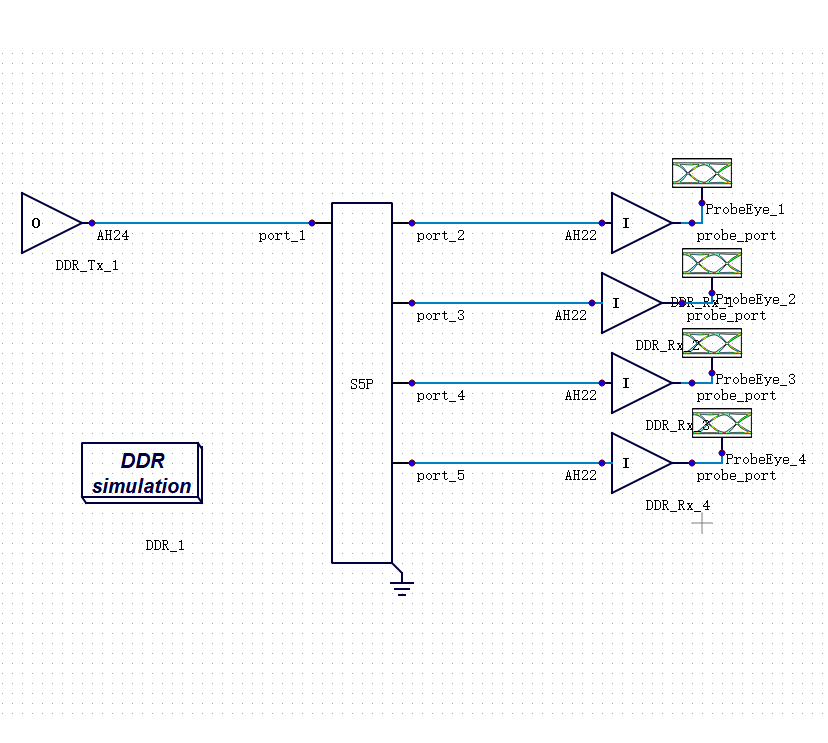

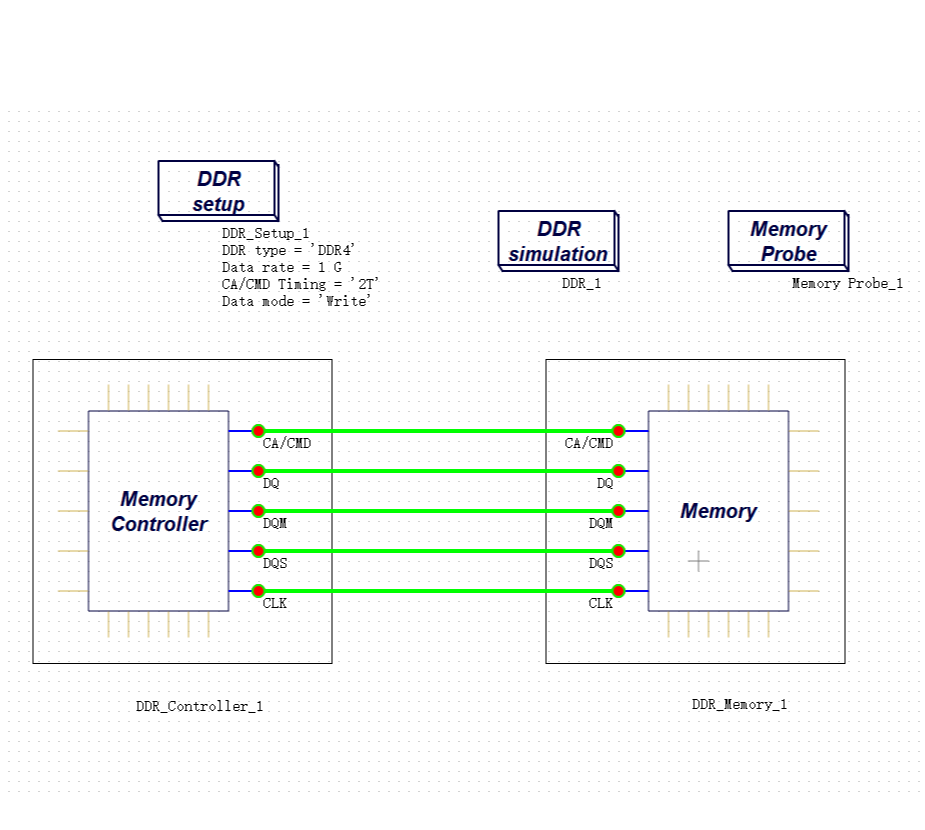

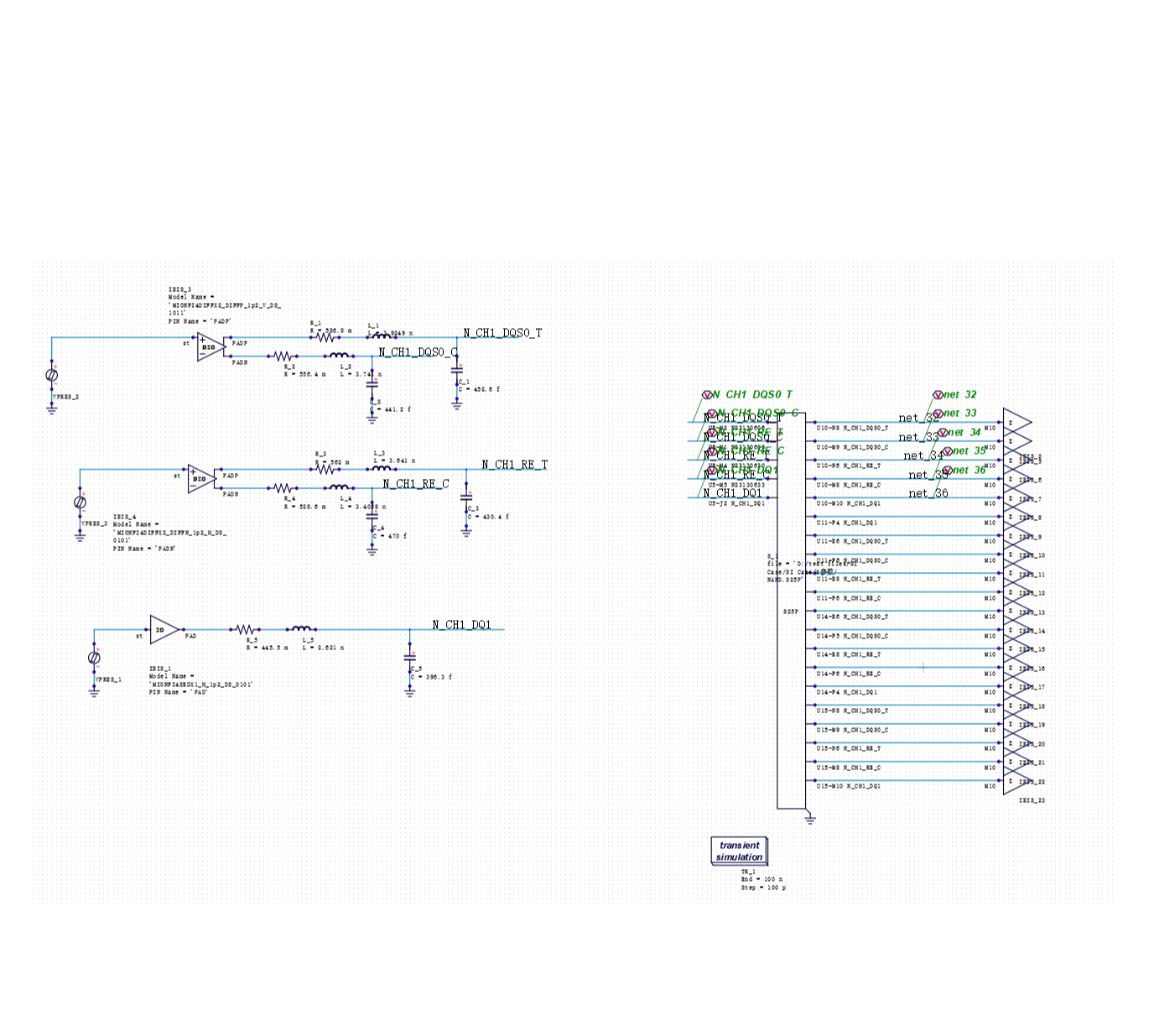

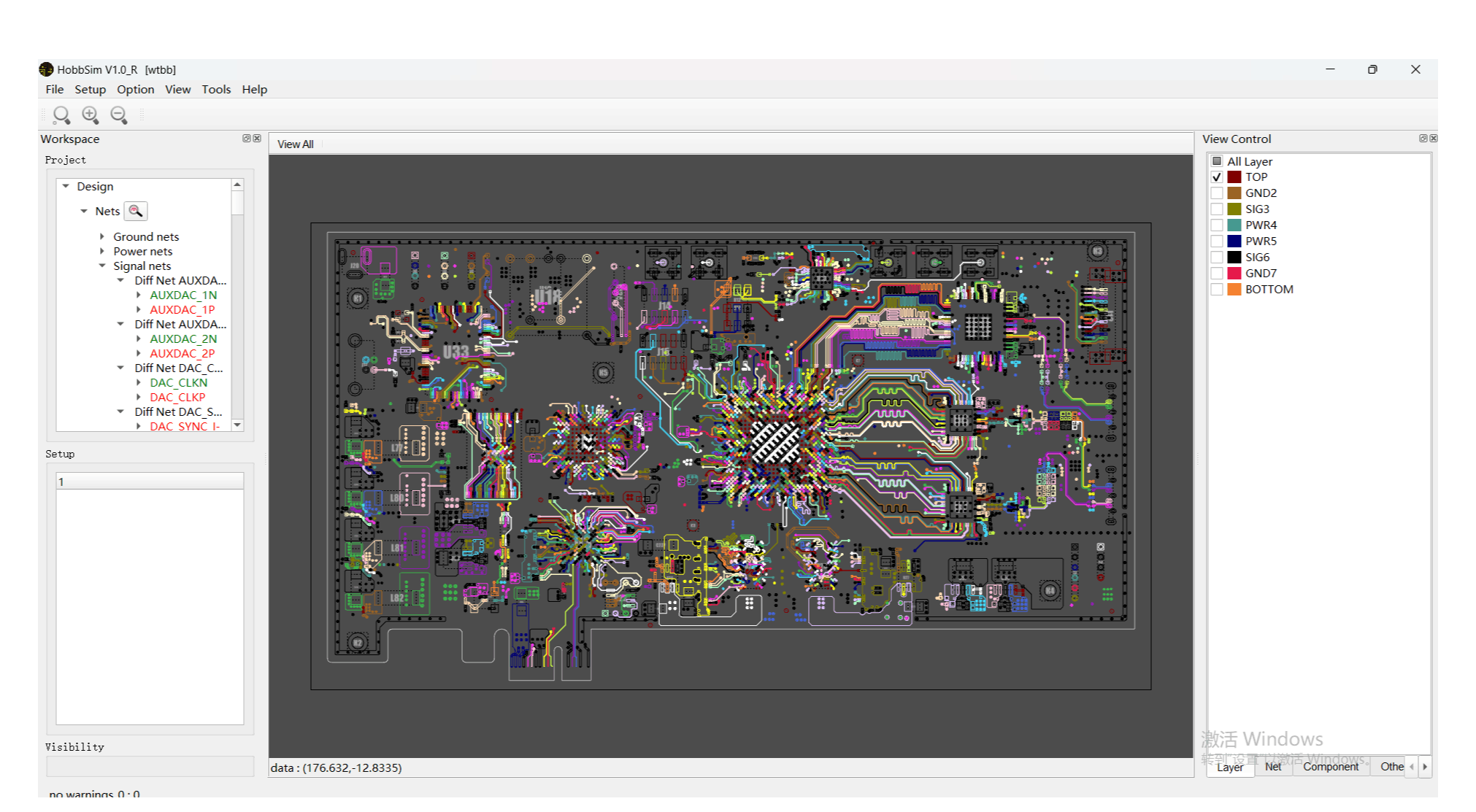

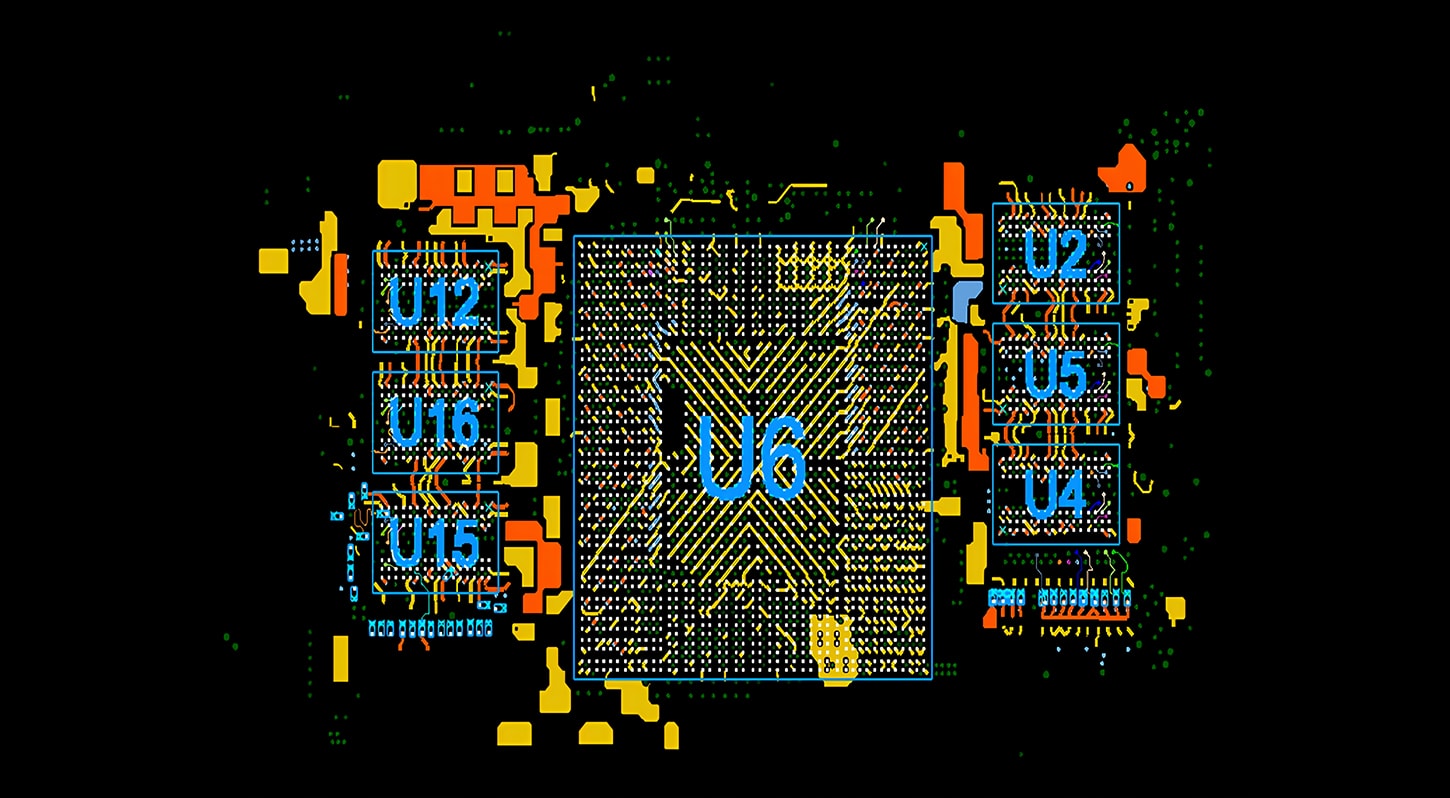

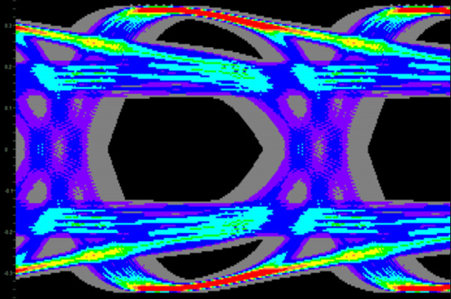

Focusing on the application of signal and power integrity, Julin has released the GUI-based general-purpose circuit simulation platform, which owns a built-in industry-standard SPICE engine. SIDesigner can do quick what-if analysis to get the best layout decisions in signal integrity and power integrity perspectives during pre-layout stage. With the help of 3rd party 3D full-wave modeling solver, SIDesigner can do all signal integrity timing sign-off simulation work.

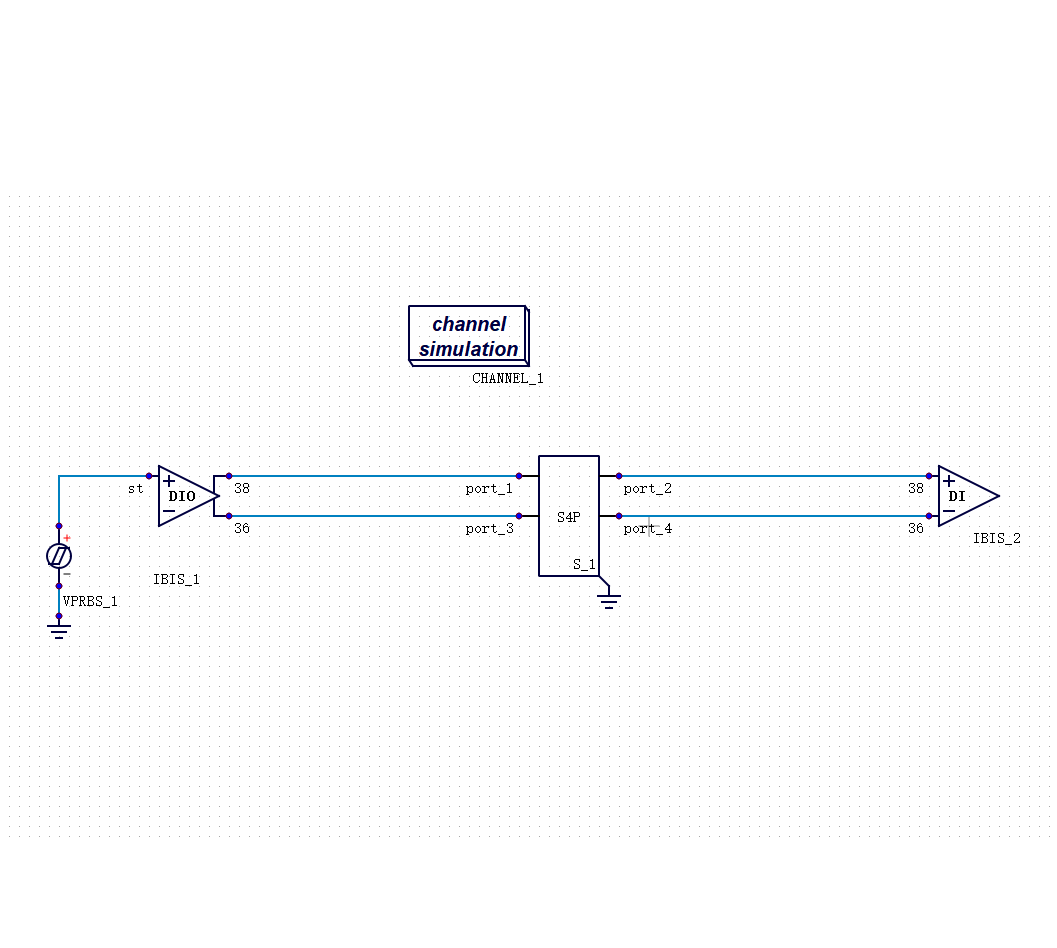

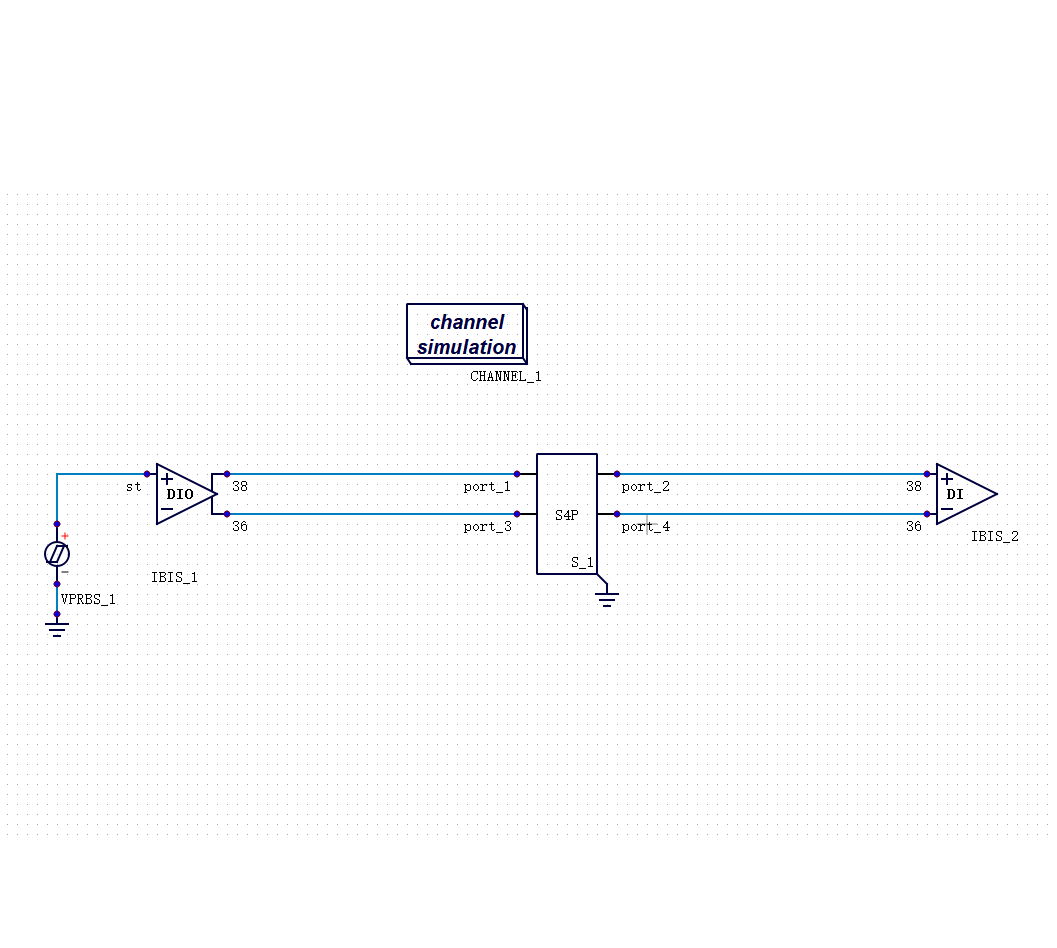

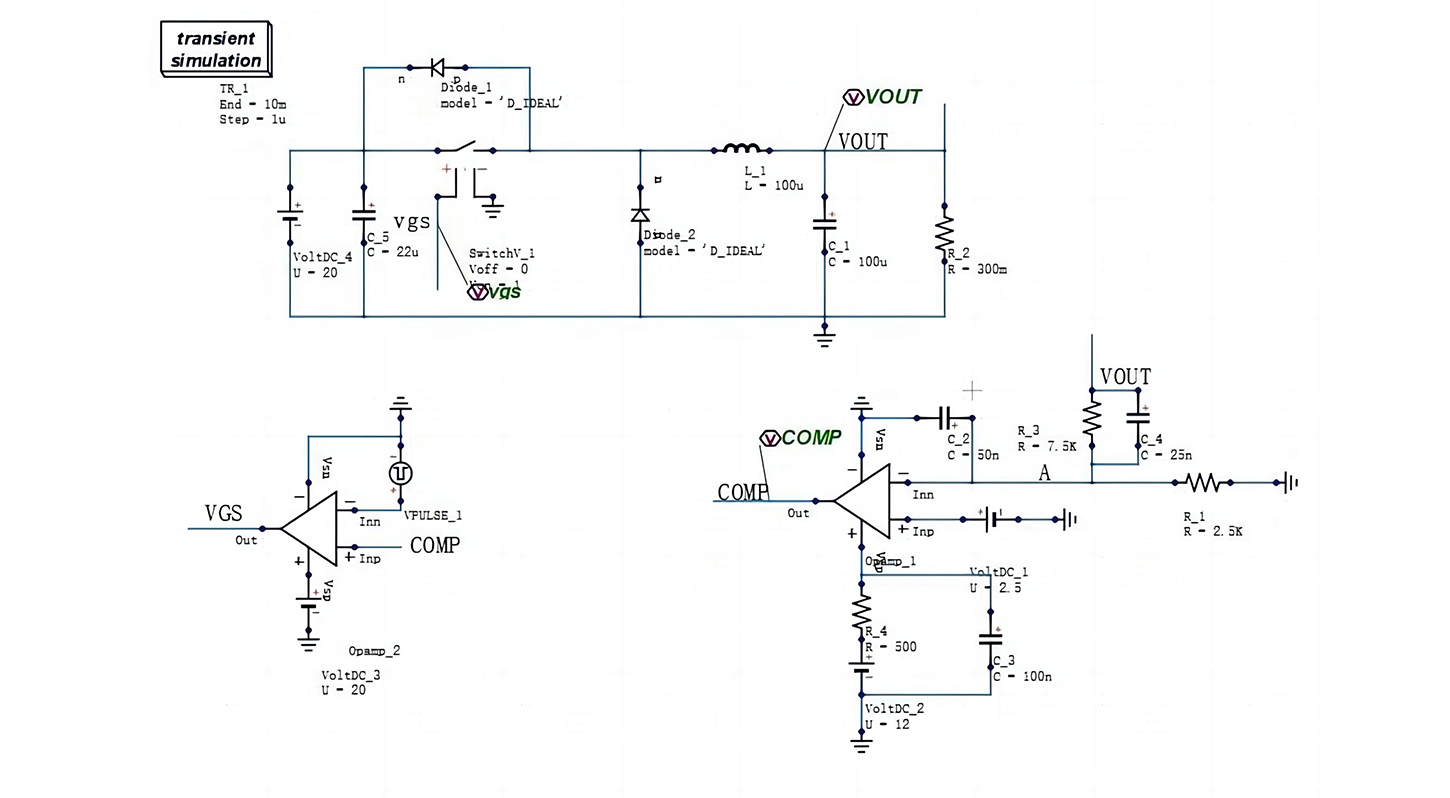

In addition, SI-PI co-simulation is supported with the help of SIDesigner’s free style circuit-deck building, with which SIDesigner users can set up a signal integrity or power integrity simulation by simply drag & drop operations. The general purpose circuit simulation, which consists of any kinds of common circuit elements, is also supported.

The main functions of SIDesigner:

SIDesigner’s ease of use flow enables the beginner to quickly get familiar with signal integrity and power integrity analysis flow, and saves the expert much flow setting time.

SIDesigner supports all parallel interfaces’power-aware SI analysis with built-in industry-standard SPICE engine. Users can do thorough what-if digging of design parameters to obtain the optimal design option.

SIDesigner supports all commonly used circuit elements and power delivery network can be easily built to perform AC/DC/Transient analysis. It can also include VRM model and chip power model (CPM) for system-level power integrity analysis.

By exploring different parts combinations of PDN, what-if analysis can be easily done to optimize PDN design.

SIDesigner supports general-purpose circuit topologies simulation, which enables the users to simulate what they want to verify and improve design’s performance while not being limited to pre-built channel blocks and topologies.

Recommended

-

Julin: Never Thought of Domestic Substitution, but Julin's Chiplet Package Design SI Simulation Products Reach Industry Leadership Levels2025.04.09

Julin: Never Thought of Domestic Substitution, but Julin's Chiplet Package Design SI Simulation Products Reach Industry Leadership Levels2025.04.09 -

Julin Technology Wins“Quality Enterprise of Semiconductor EDA Market Development”and Promoting industrial ecosystem upgrades through independent innovation.2025.03.26

Julin Technology Wins“Quality Enterprise of Semiconductor EDA Market Development”and Promoting industrial ecosystem upgrades through independent innovation.2025.03.26 -

Julin Technology Wins 2024 Shenzhen IC Industry"Innovative Chip Rising Star Award"!2025.03.10

Julin Technology Wins 2024 Shenzhen IC Industry"Innovative Chip Rising Star Award"!2025.03.10