Pre-simulation of differential signals: a key assistant in PCB design

-

2024.10.14

一、差分信号前仿真

在当今高速电路设计中,差分信号传输已成为高速信号传输的重要方式。然而,如何在PCB布线之前就能预知潜在问题并优化设计呢?答案就是:差分信号前仿真。

二、SIDesigner 仿真案例分析

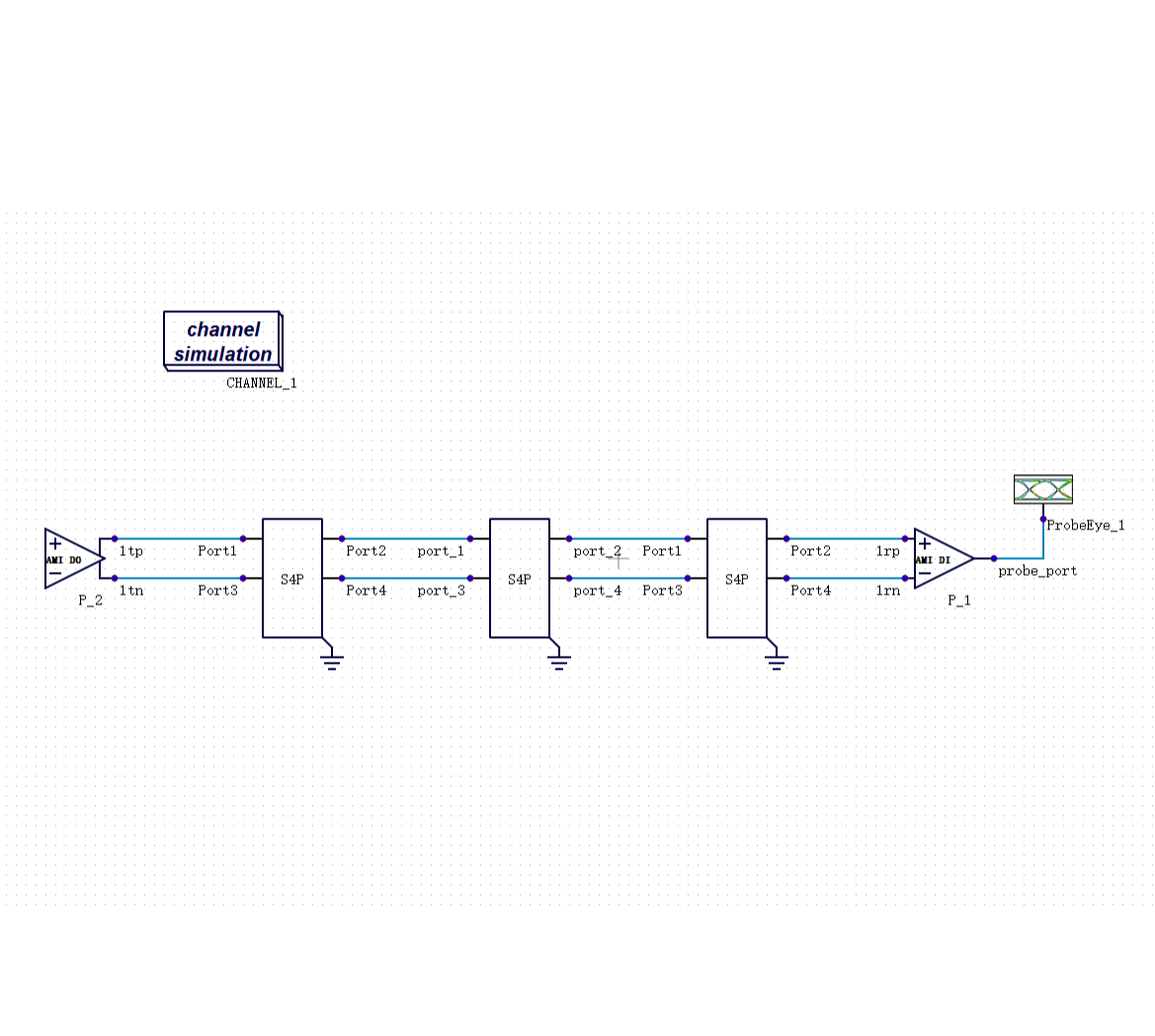

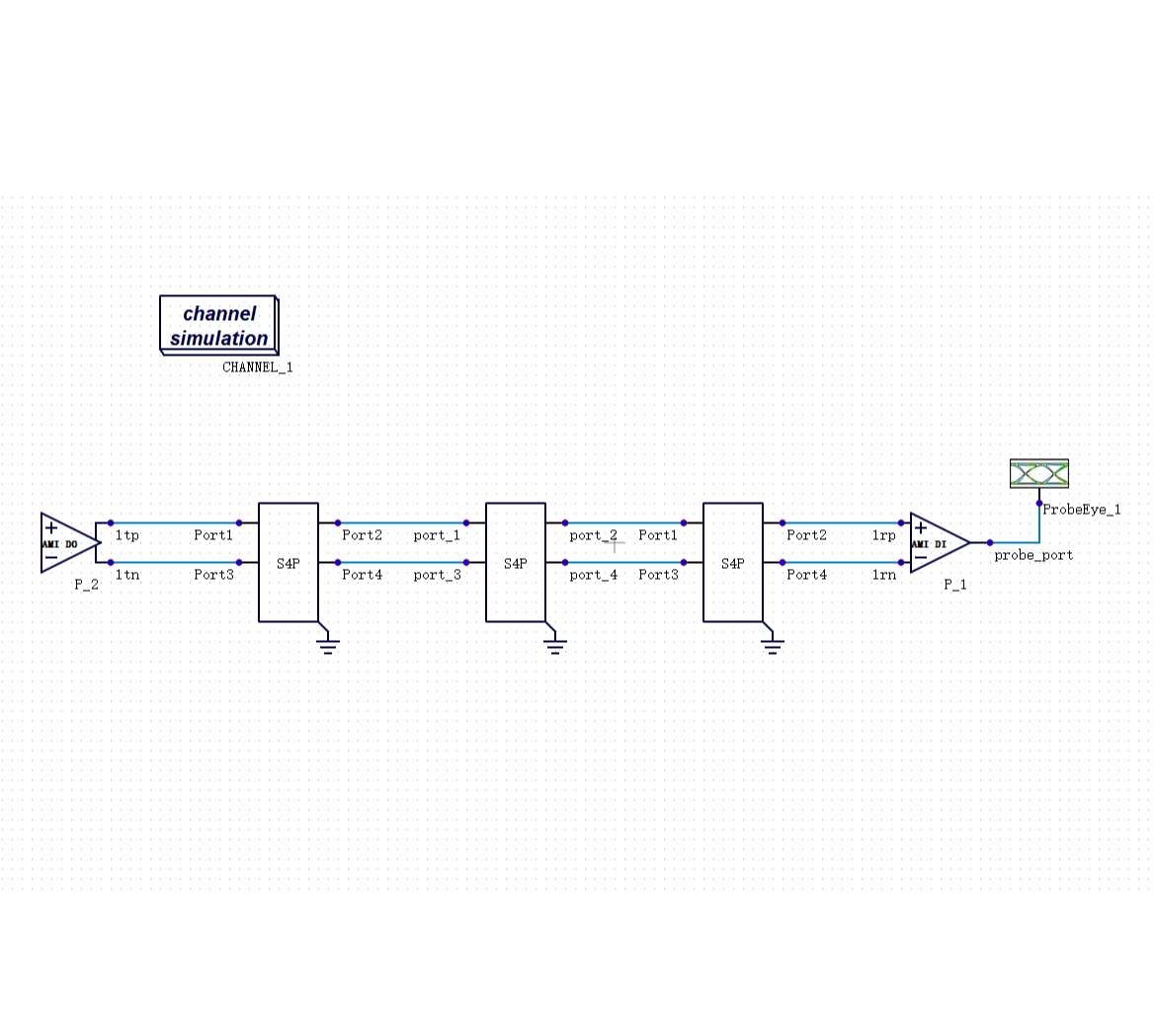

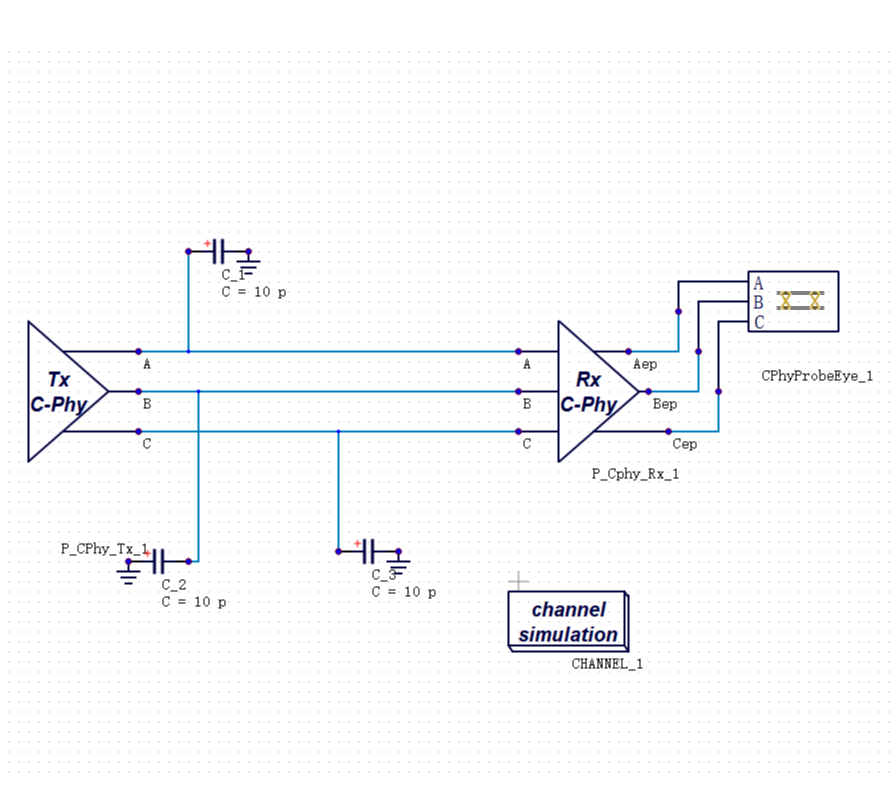

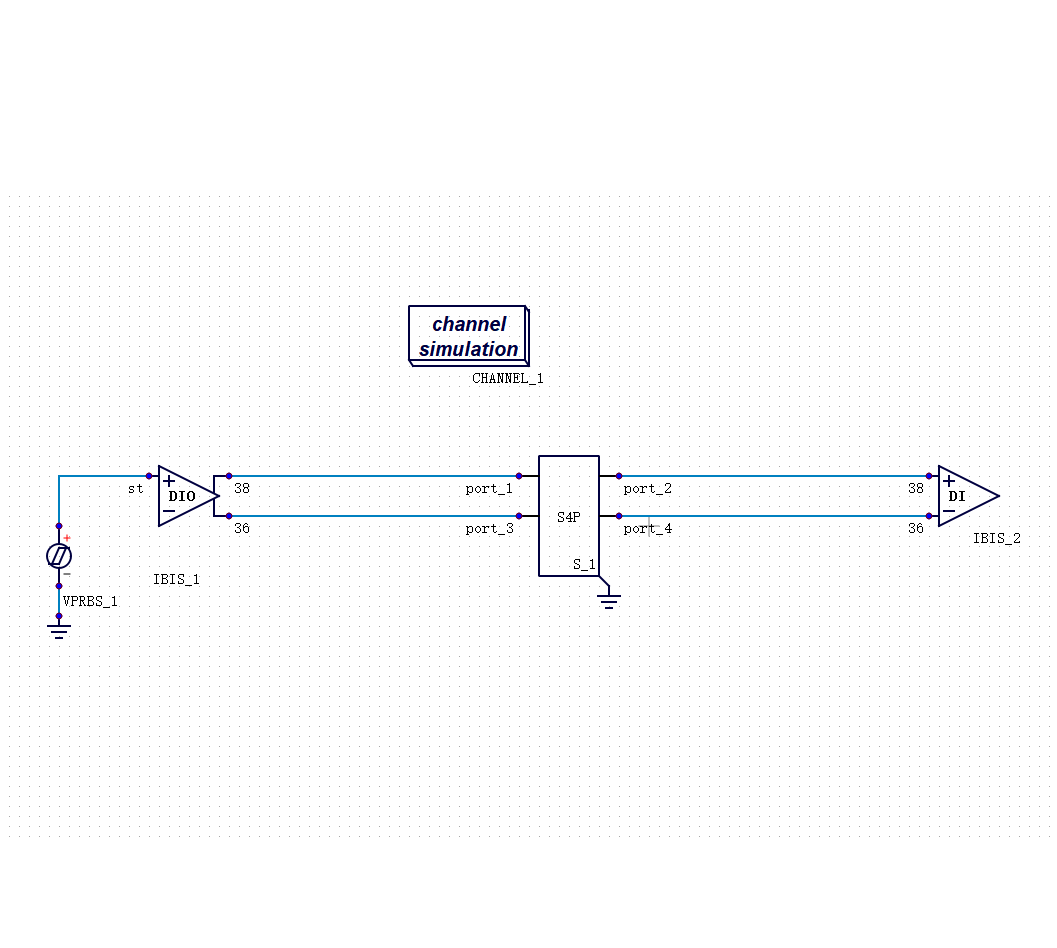

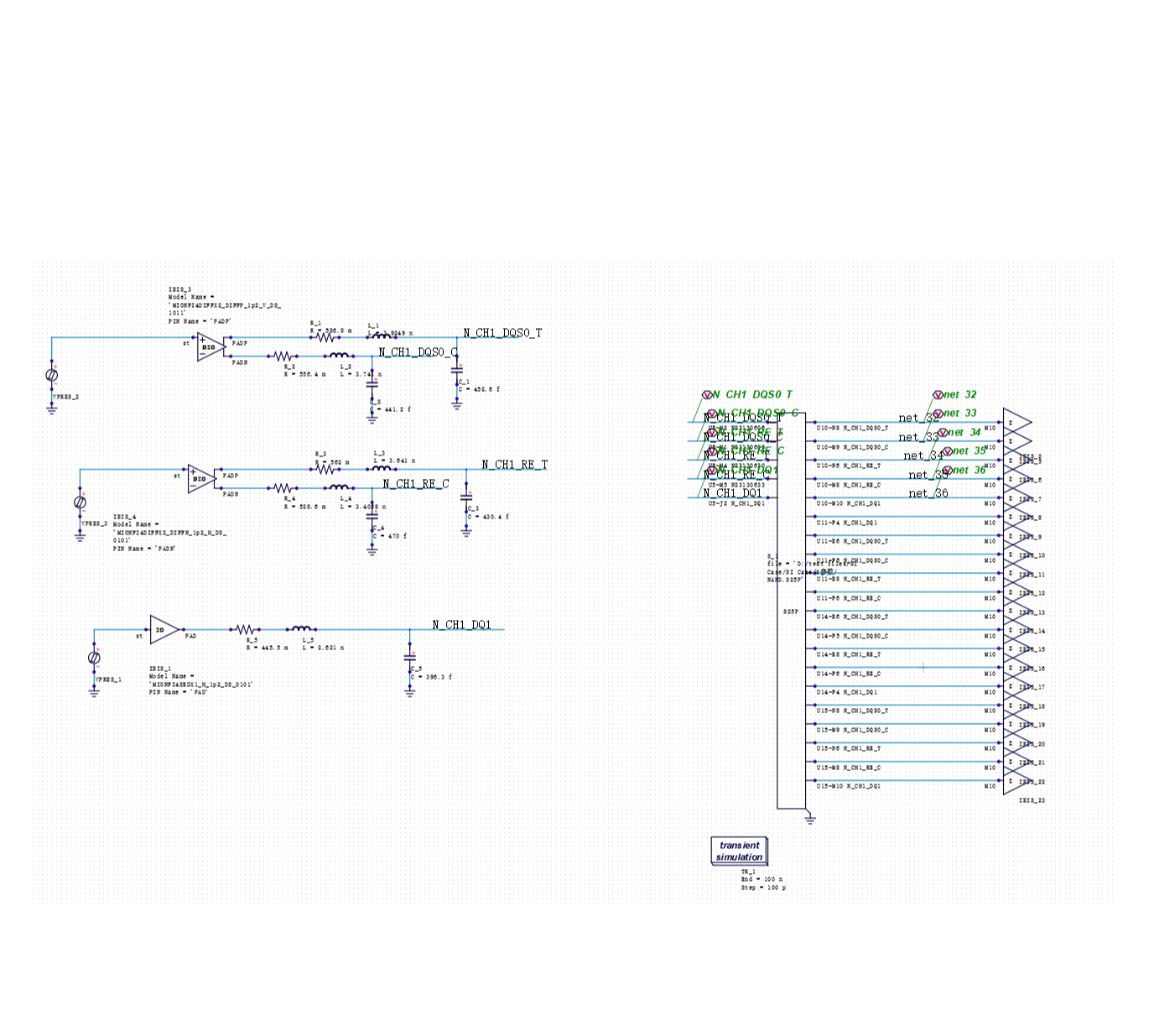

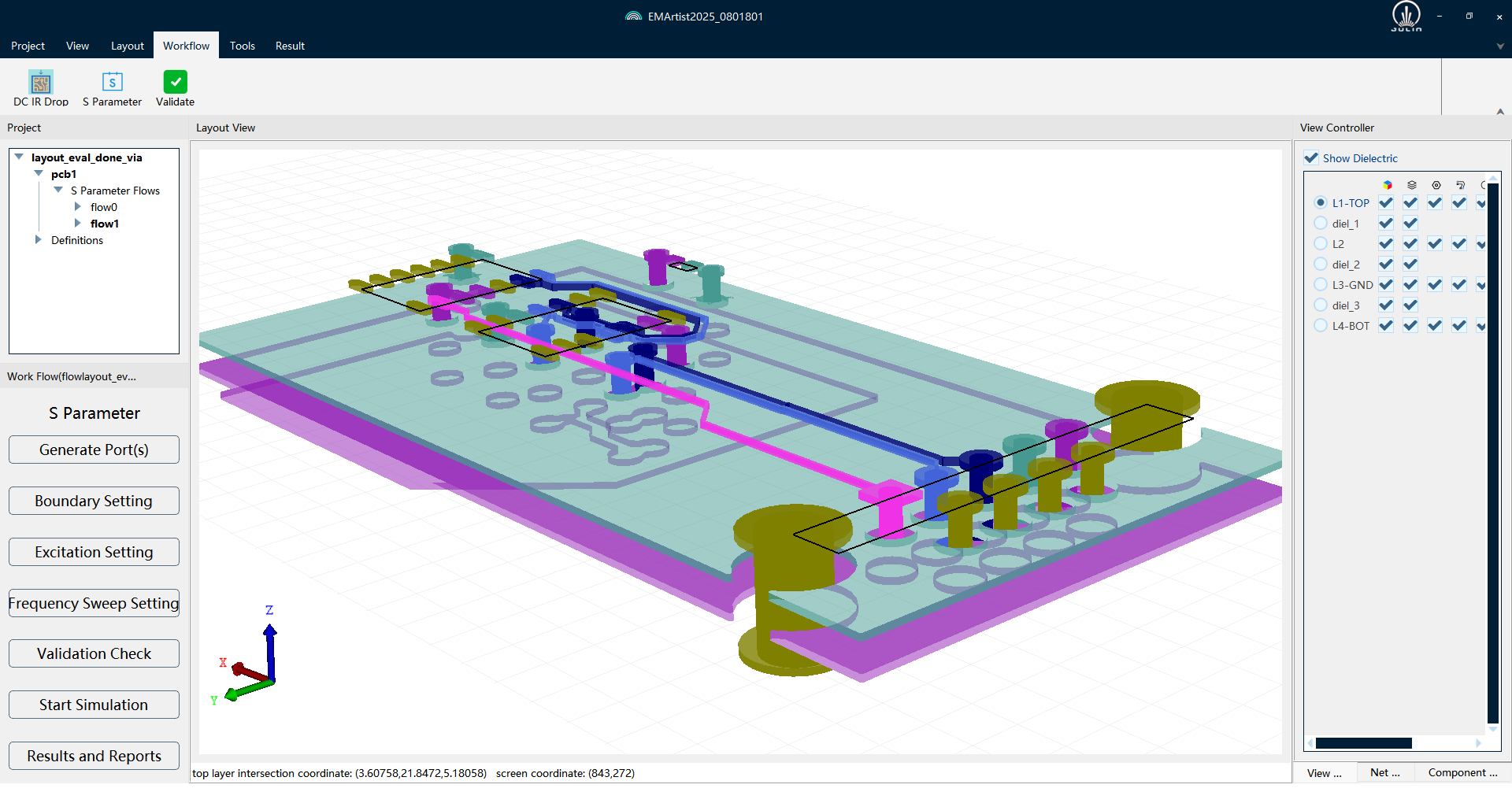

接下来,我们看下使用巨霖SIDesigner进行差分信号走线长度匹配仿真过程。这是差分信号前仿真中一个非常重要的环节,对于保证高速信号的完整性至关重要。

1、首先要确定目标信号:

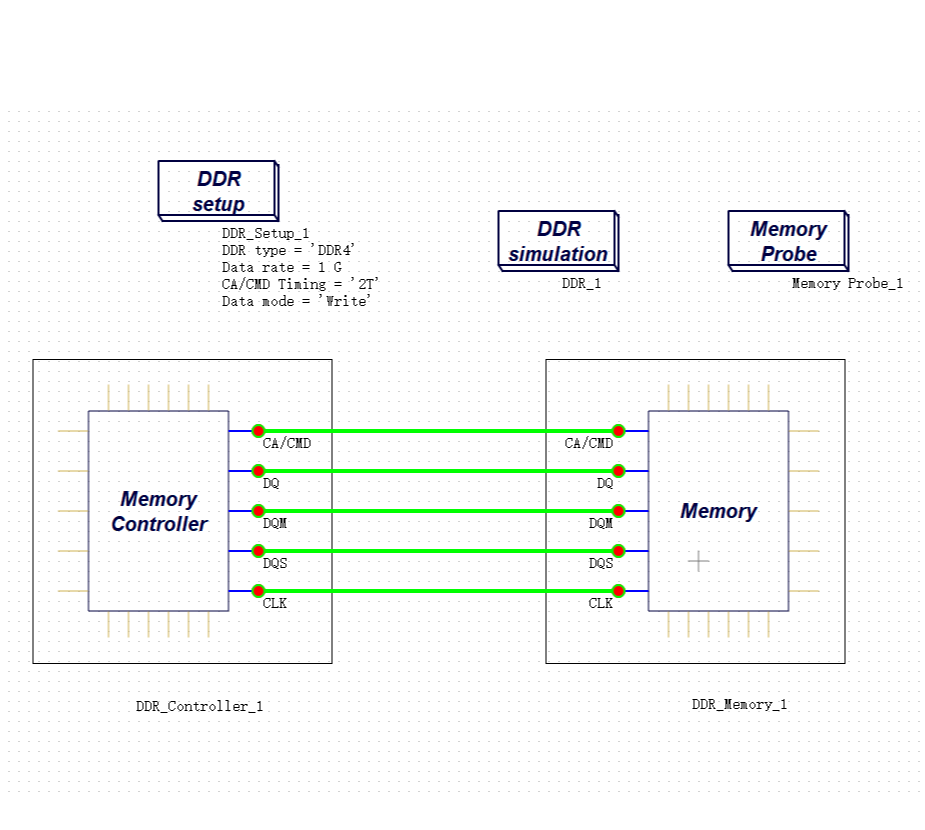

首先确定需要进行长度匹配的差分对。例如,我们以DDR4接口的时钟线(DQS/DQS_n)为例。

2、设置初始参数:

在仿真软件中设置以下初始参数:

·信号频率:例如DDR4-3200为1600MHz

·PCB材料属性:如FR-4的介电常数(Dk)和损耗因子(Df)

·初始差分对长度:假设为2英寸(约50.8mm)

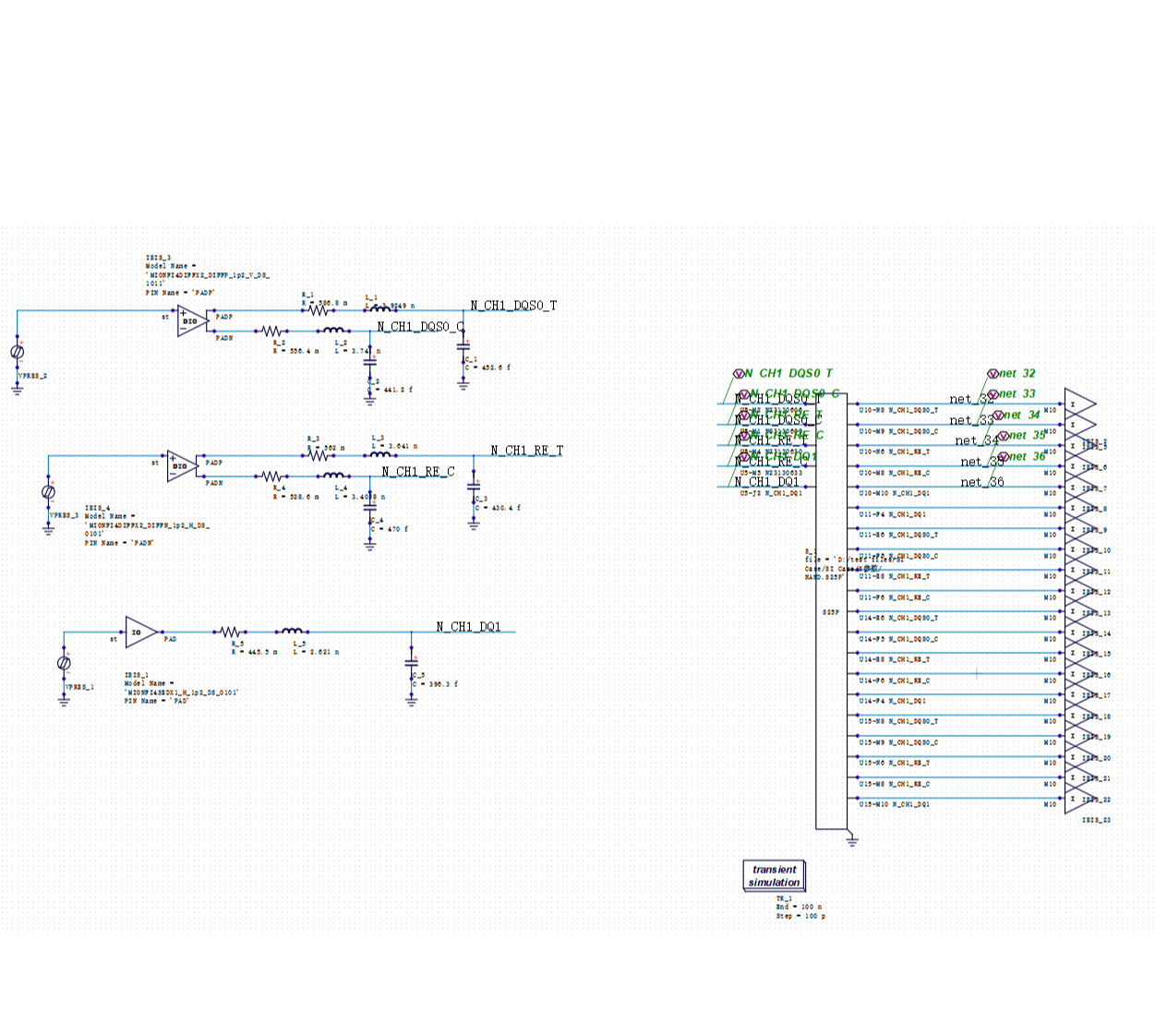

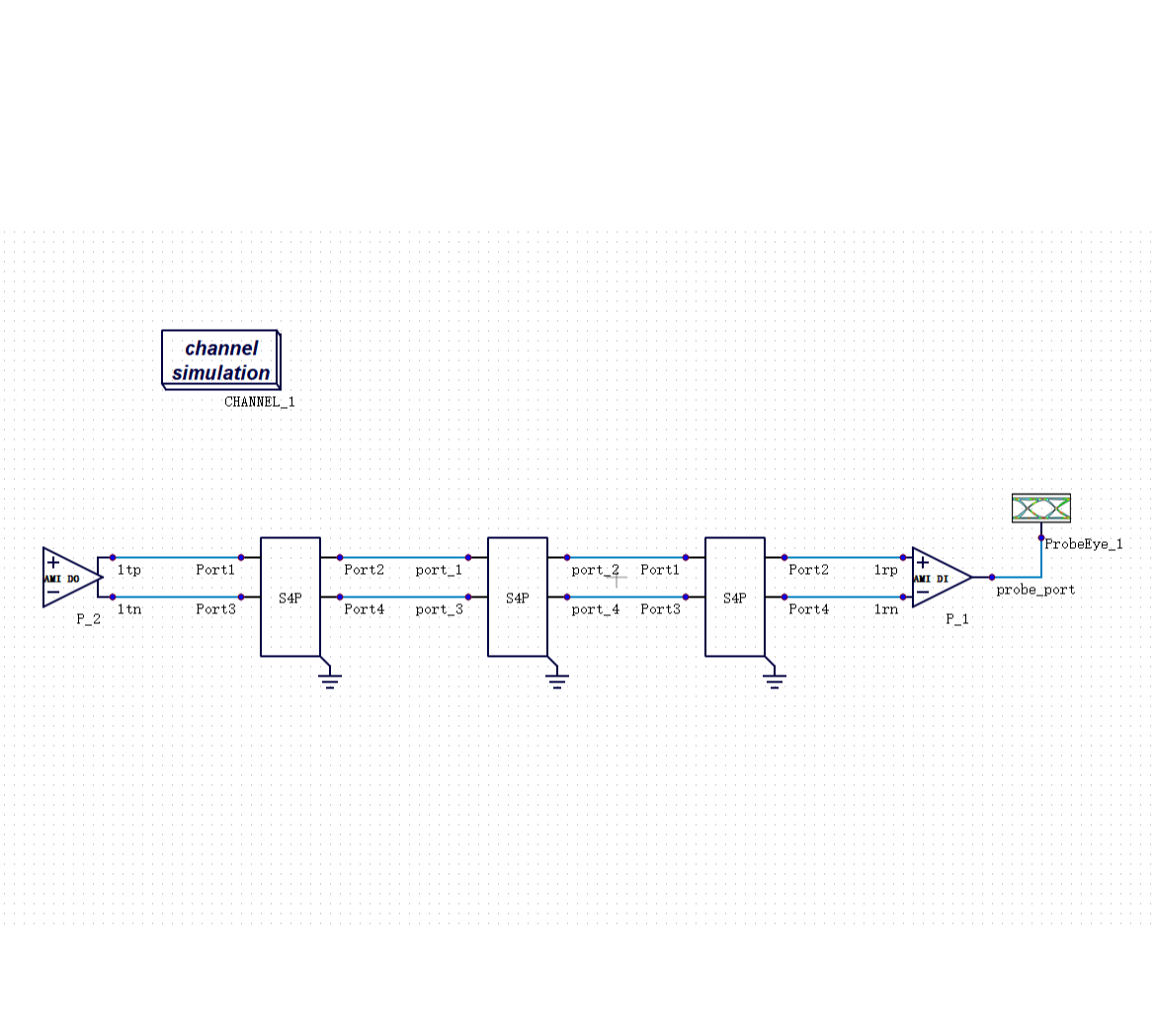

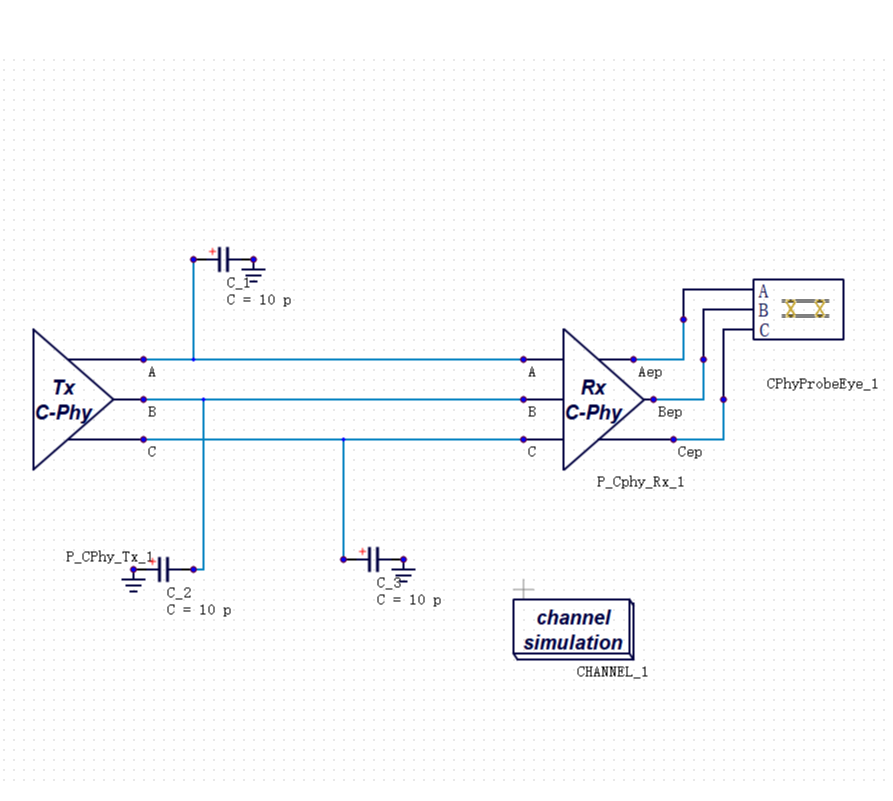

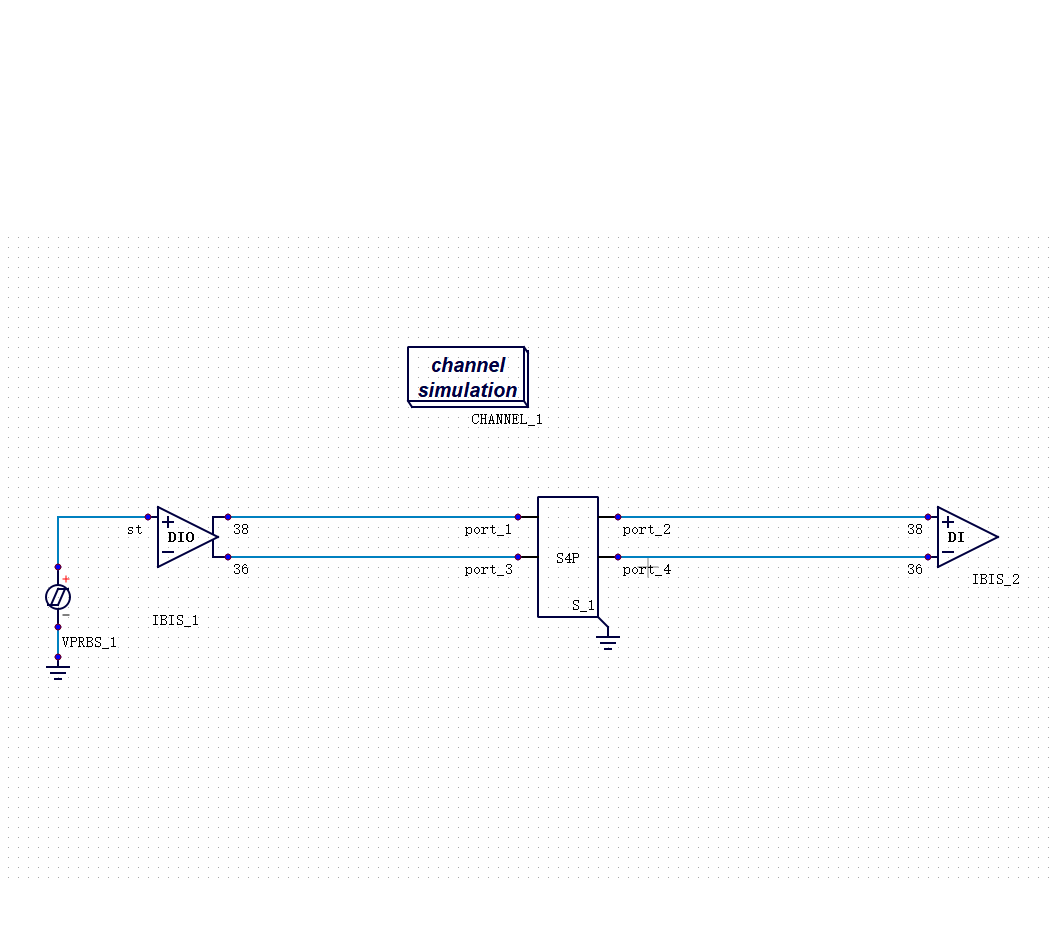

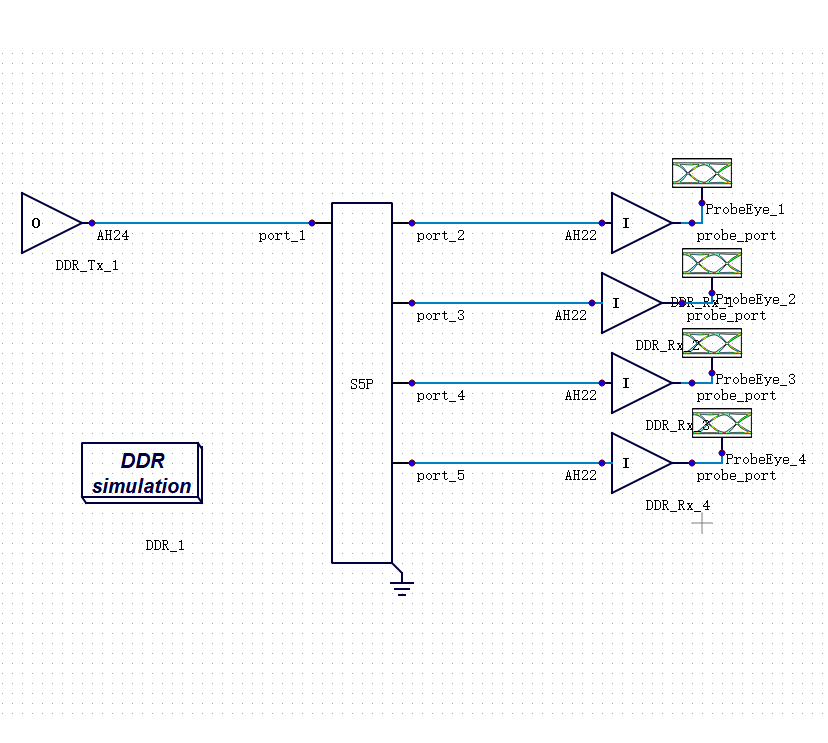

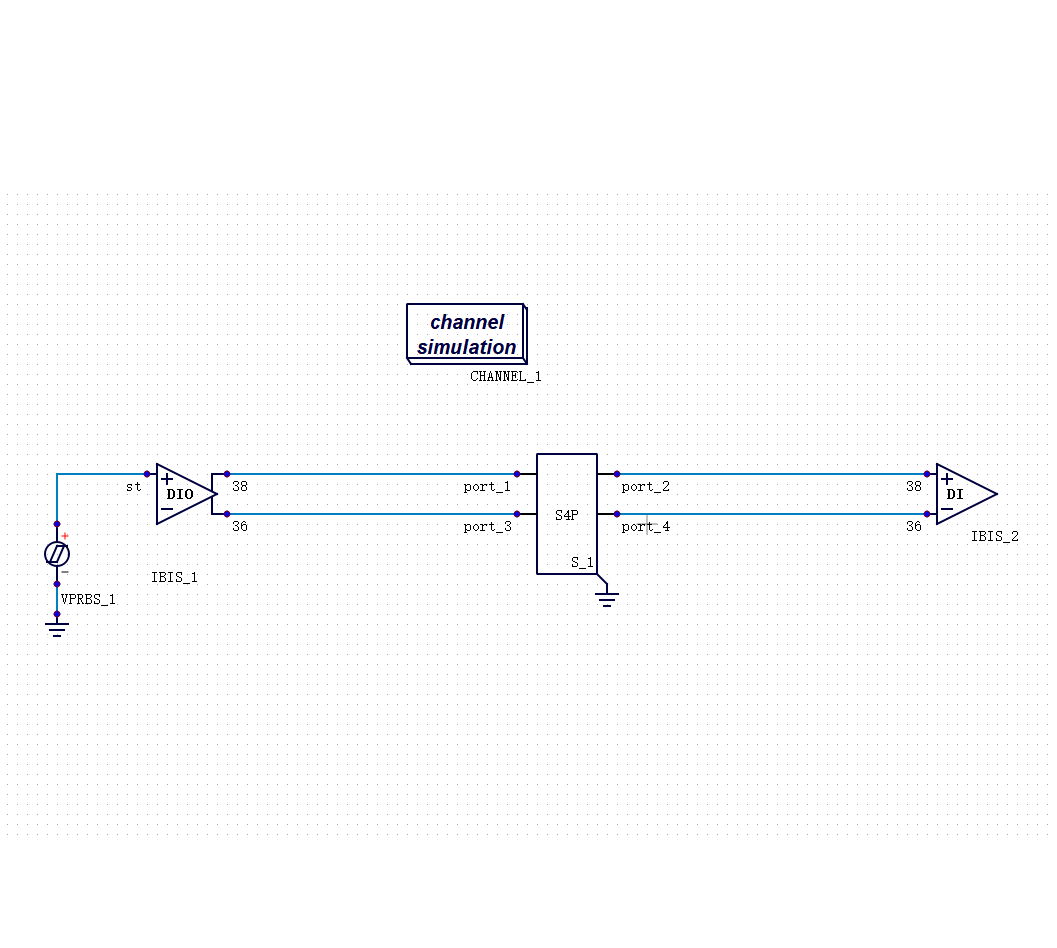

在SIDesigner中完成原理图如下:

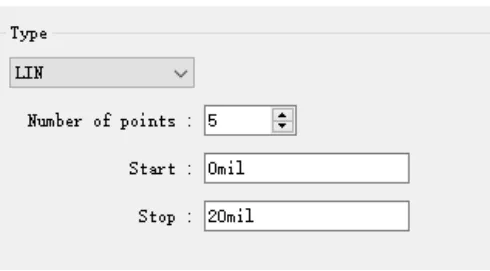

3、长度失配扫描:

进行参数扫描,逐步增加差分对中一条线(此例中选择DQS)的长度,范围从0mil到20mil,步进5mil。

4、分析扫描结果:

对每个长度失配值仿真出来的波形以及自定义波形功能共模电压波形进行分析:

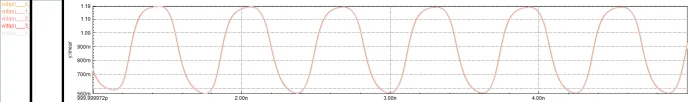

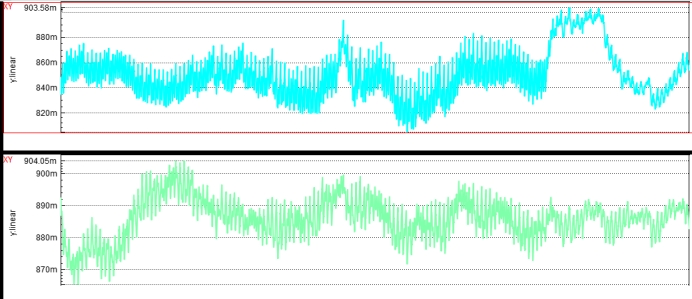

DQS信号5个扫描波形叠加波形如下:

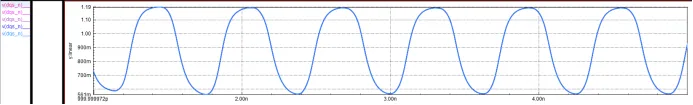

DQS_n信号5个扫描波形叠加波形如下:

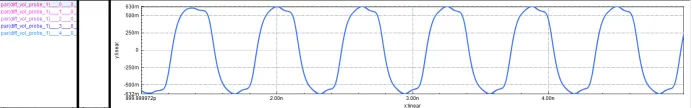

DQS-DQS_n差分波形5个扫描波形叠加波形如下:

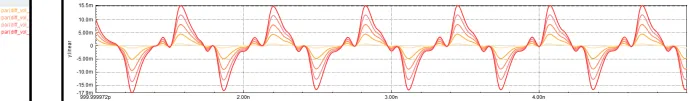

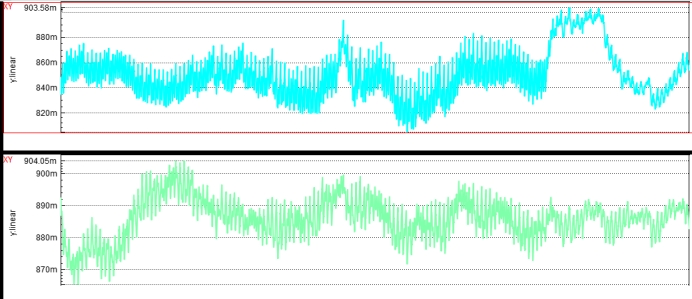

(DQS+DQS_n)/2-Vcom共模电压信号5个扫描波形叠加波形如下:

5、确定最佳匹配长度:

通过观察和分析上述波形,我们可以得出以下结论:

a. DQS差分对的单端信号分析:

当直接观察DQS差分对的单端信号波形时,这些波形叠加在一起,没有显示出明显的差异。

这种情况下,仅依靠单端信号波形难以判断长度匹配的质量。

b. 共模信号分析:

当我们转而观察共模信号时,情况变得更加清晰。

共模信号能够更敏感地反映出差分对中的不平衡,因此成为判断长度匹配质量的关键指标。

c. 长度失配的影响:

·当长度失配在5mil以内时:

共模电压波形振幅很小,保持在5mV以内。

这表明在这个范围内,差分对的平衡性保持得较好。

·当长度失配超过5mil时:

共模电压明显增大,超过5mV。

在观察到的数据中,最大共模电压达到了17.3mV。

这表明长度失配超过5mil会显著影响差分对的平衡性。

d. 最佳匹配长度的确定:

基于上述观察,我们可以将5mil作为一个关键阈值。

将长度失配控制在5mil以内可以有效地将共模干扰控制在可接受的水平(5mV以下)。

e. 进一步的考虑:

信号完整性:保持较低的共模电压有助于减少EMI辐射和提高信号完整性。

制造可行性:考虑到PCB制造的公差,5mil的匹配要求是一个相对合理且可实现的目标。

性能与成本平衡:虽然进一步减小长度失配可能会带来更好的性能,但也会增加设计和制造的复杂性及成本。

f. 建议:

在设计中,应将DQS差分对的长度匹配控制在5mil以内。

对于特别关键或高速的信号,可以考虑更严格的匹配标准,如3mil以内。

在实际设计中,应结合具体的信号速率、板层堆叠、阻抗控制等因素来微调这个标准。

g. 验证方法:

在实际设计中,建议使用时域反射仪(TDR)或矢量网络分析仪(VNA)来精确测量和验证差分对的长度匹配。

同时,应在原型板上进行实际的信号质量和EMI测试,以确认长度匹配的效果。

通过这种详细的分析和明确的标准,我们可以在设计阶段就有效控制DQS差分对的长度匹配,从而确保高速信号的完整性和系统的整体性能。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

Recommended

-

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20 -

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13 -

Chiplet packaging design faces multidimensional simulation challenges, with signal and power integrity becoming key technical bottlenecks.2025.10.29

Chiplet packaging design faces multidimensional simulation challenges, with signal and power integrity becoming key technical bottlenecks.2025.10.29 -

Power Supply Noise: The “Reef” of Electronic Systems and Strategies for Coping with It2025.07.28

Power Supply Noise: The “Reef” of Electronic Systems and Strategies for Coping with It2025.07.28