Introduction to Jitter and

Simulation Case Studies

-

2024.09.25

引言

在高速信号传输系统中,Jitter是指信号到达时间的不可预测变化,这种变化可能会导致信号失真、数据错误以及系统性能下降,尤其是在高频应用中,如数据通信、视频传输和高速数字电路,Jitter直接影响着信号的完整性和系统的可靠性。

一、Jitter的定义

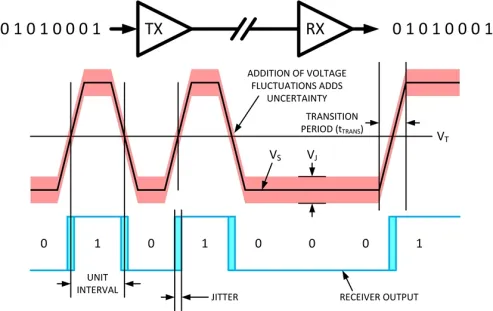

理想的数字信号的时钟周期不会产生变化,每个数据UI(Unit Interval, 即每个bit的时间长度)也都严格相等,但在真实世界里,由于热噪声和各种因素的影响,时钟或数据的边沿往往存在不确定性,其真实位置和理想位置之间的偏差,就是所谓的抖动。当时钟信号或数据信号存在较大的抖动时,接收端在识别信息时就会出错,导致信息传递出现“误码”(Bit Error)。

时序抖动的来源多种多样,数字信号中总抖动的大小很大程度上取决于不同噪声源的影响程度。依据不同噪声源引起的时序抖动的概率密度函数特征,可以将时序抖动分为确定性抖动(deterministic jitter, DJ)和随机抖动(random jitter, RJ)两大部分。确定性抖动又可以分为周期性抖动(periodic Jitter,PJ)和数据相关性抖动( data dependent jitter, DDJ),周期性抖动由由系统时钟或周期性干扰引起,通常表现为可预测的模式,由于任何周期波形都可以分解成傅里叶序列的谐波相关正弦曲线,这类抖动又被称为正弦曲线抖动(sinusoidal jitter,SJ)数据相关性抖动与数据的码型有关,数据当前比特位的波形会受到之前几个比特位跳变时刻的影响。占空比失真(duty cycle distortion, DCD)和符号间干扰( inter-symbol interference, ISI)是数据相关性抖动的两个主要组成部分。随机抖动由随机噪声或信号干扰引起,无法预测,通常通过统计方法来分析,随机抖动符合高斯正态分布。随机抖动的峰峰值和测量的样本数(总bits数量)息息相关,理论上只要测量的时间足够长,随机抖动可以增加到无穷大。抖动分析时,随机抖动的测量值一般用RMS值来表示,即正态分布的σ值。

二、Jitter的优化策略

在实际电路中Jitter主要由以下几个方面引起:时钟源本身的不稳定性带来的抖动,电路设计中的缺陷:如电源噪声、地弹效应等,都可能引起信号抖动。信号传输过程中,信号的反射、串扰,信号经历衰减和噪声干扰,会导致信号波形畸变,进而产生Jitter。当采样时钟与数据信号之间的相位差发生变化时,会导致采样点偏离理想位置,产生Jitter。

为了降低接收端的Jitter,可以采取以下措施:选用低jitter时钟源,确保时钟信号的稳定性。使用适当的滤波器和去耦电容,减少噪声。使用高性能的连接器和电缆,减少传输中的信号损失确保信号路径短且直接,降低信号损耗。使用差分信号传输,减少共模噪声影响。加强信号滤波和噪声抑制技术,降低噪声对信号的影响。精确匹配阻抗,减少反射和信号干扰。改进时钟恢复算法,提高时钟恢复精度。使用锁相环(PLL)等同步技术,保持采样时钟与数据信号的同步。

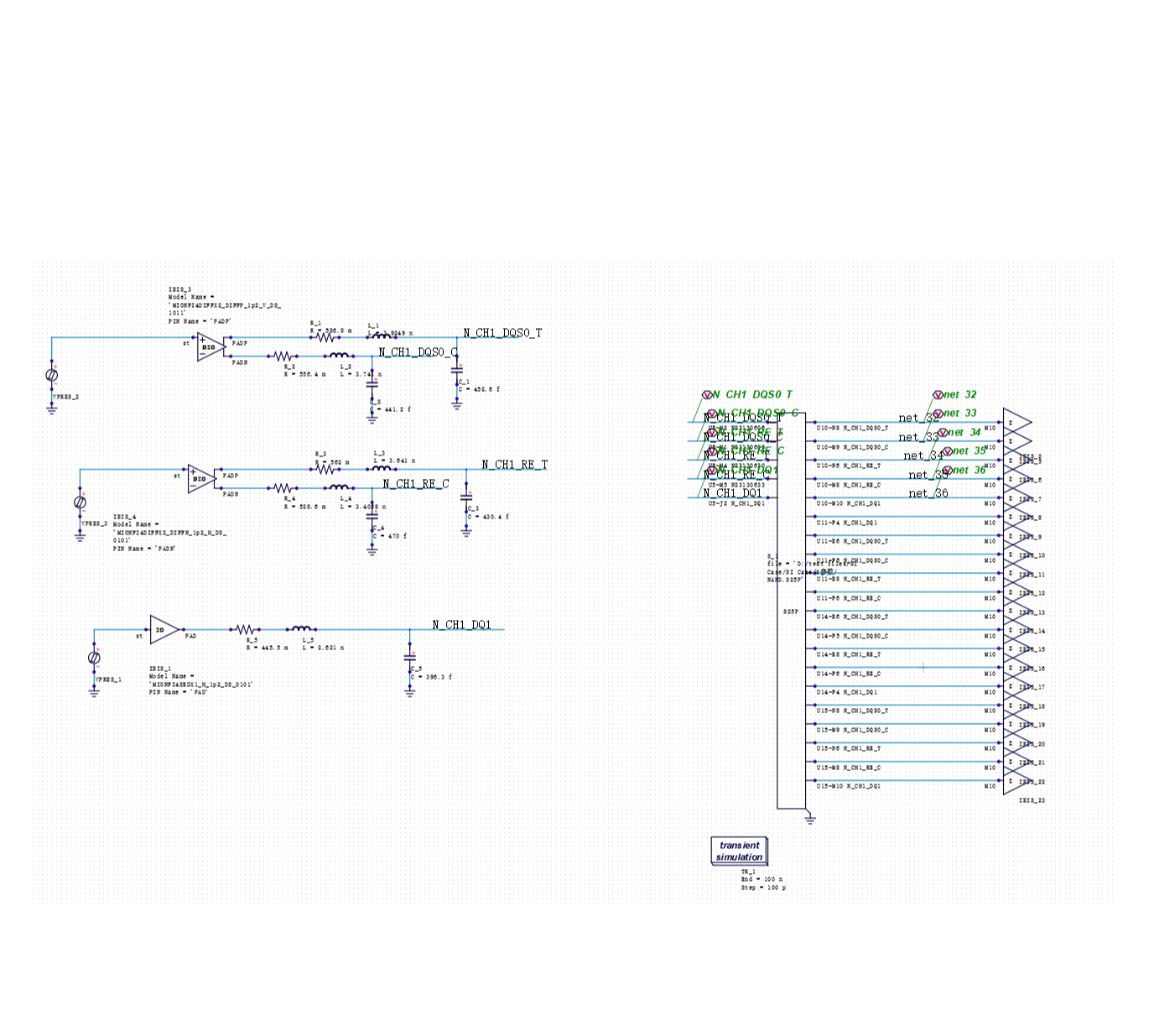

三、使用SIDesigner进行实际应用

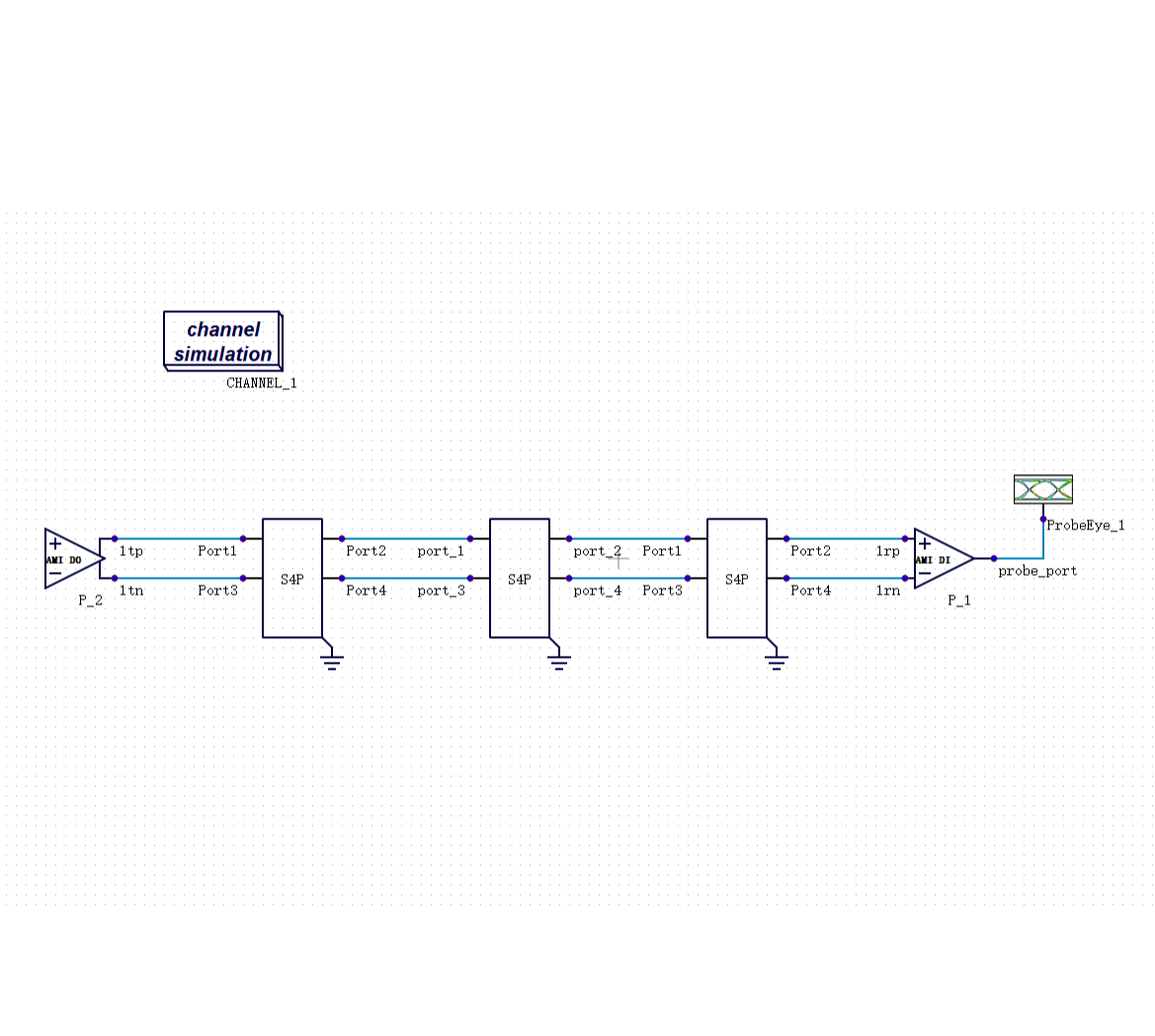

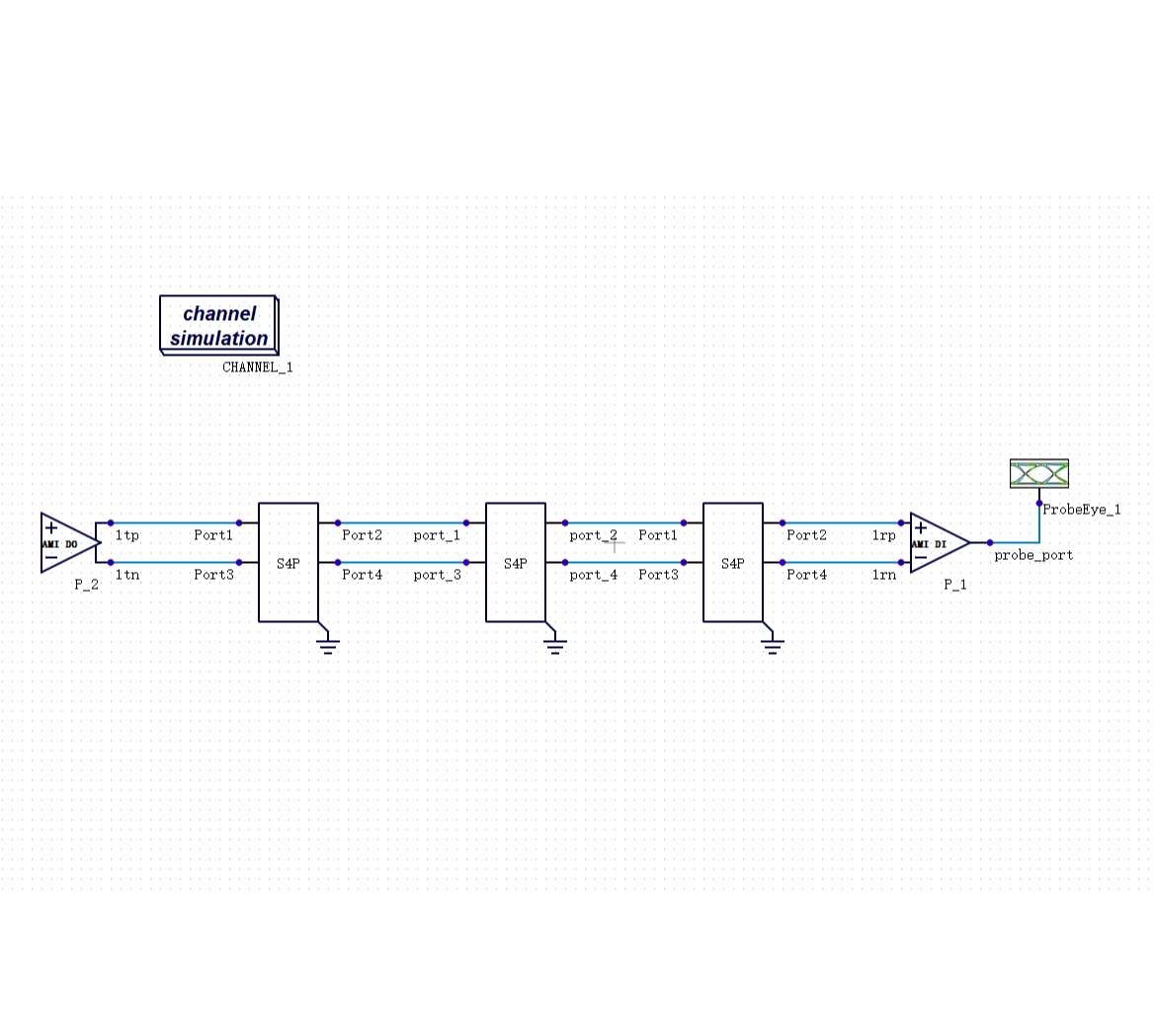

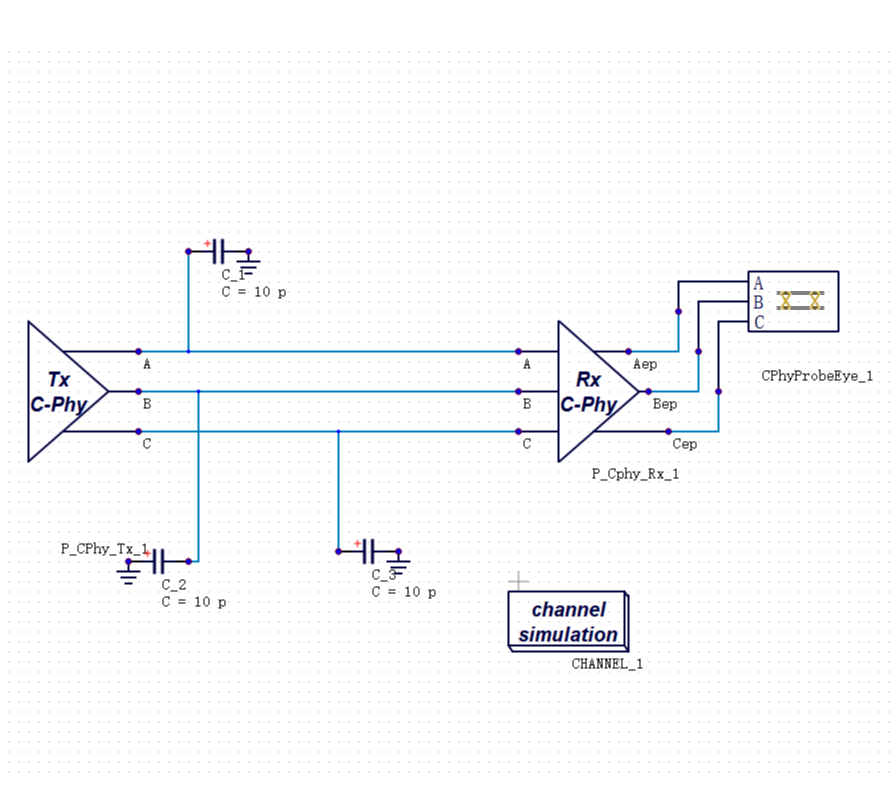

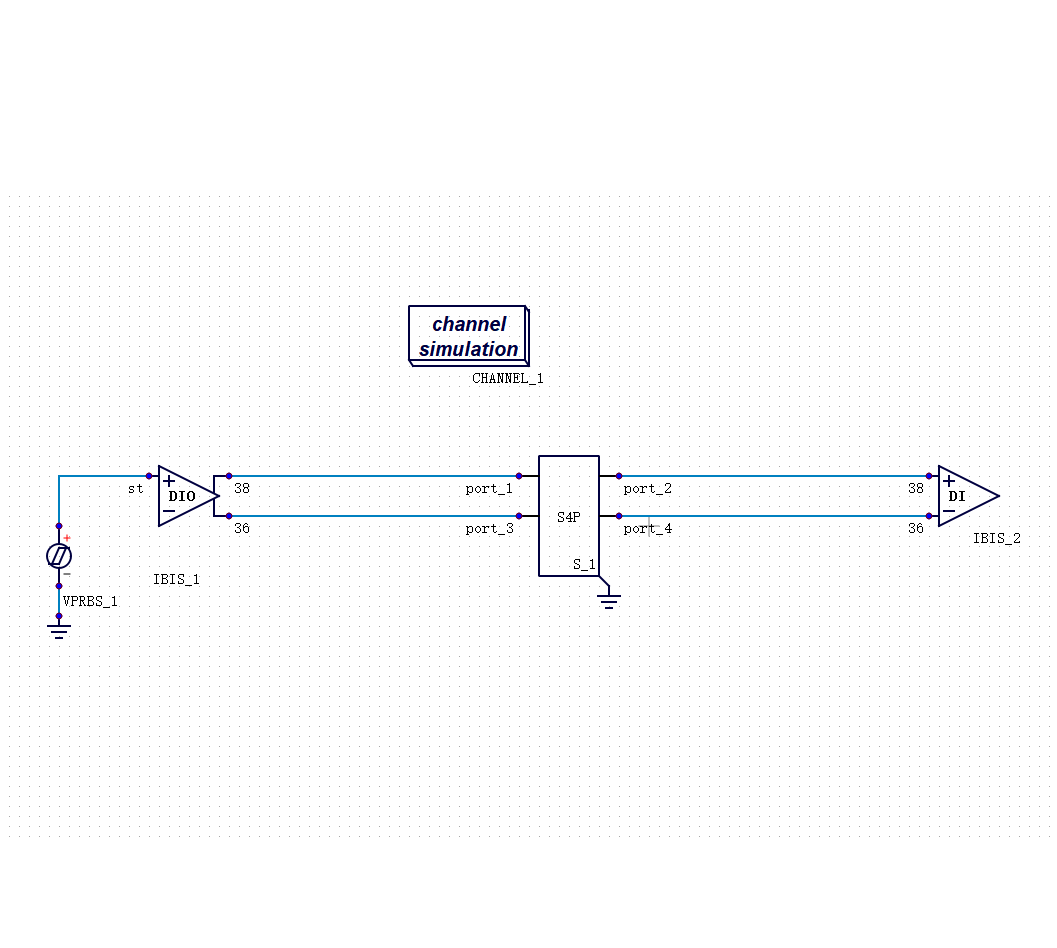

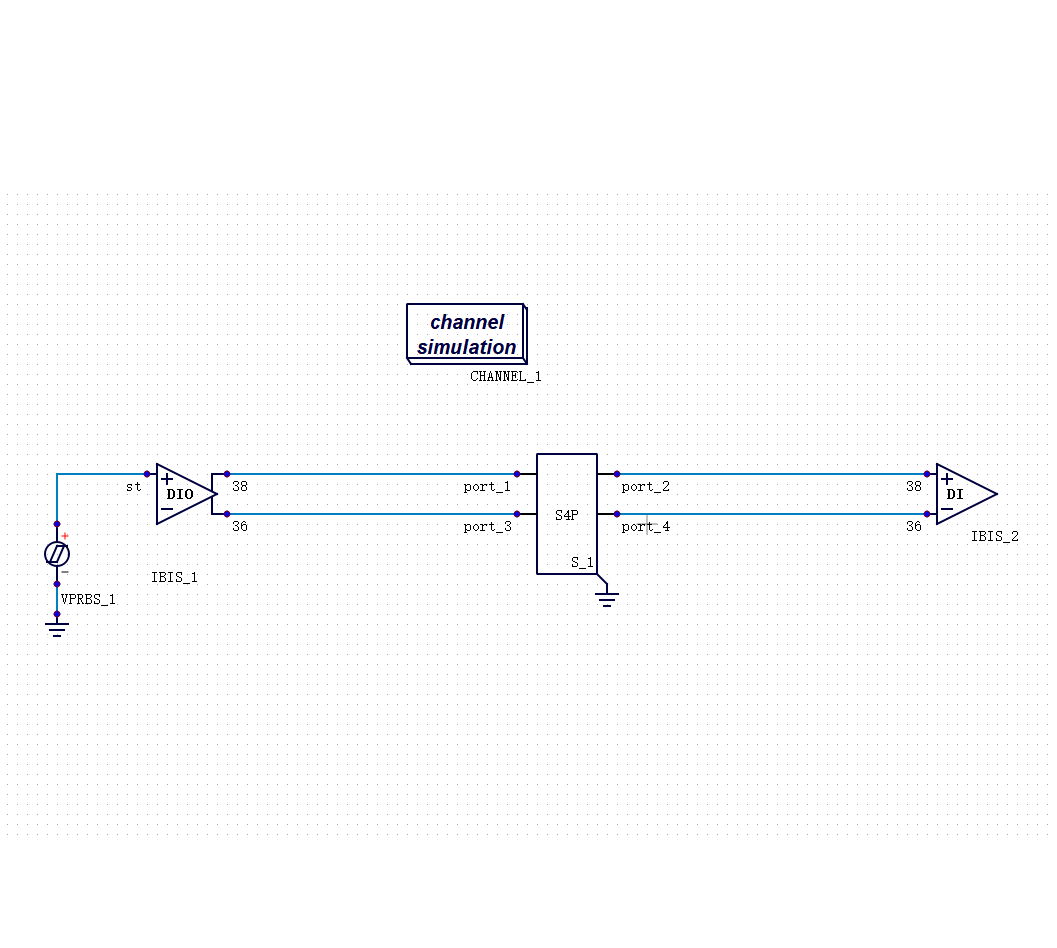

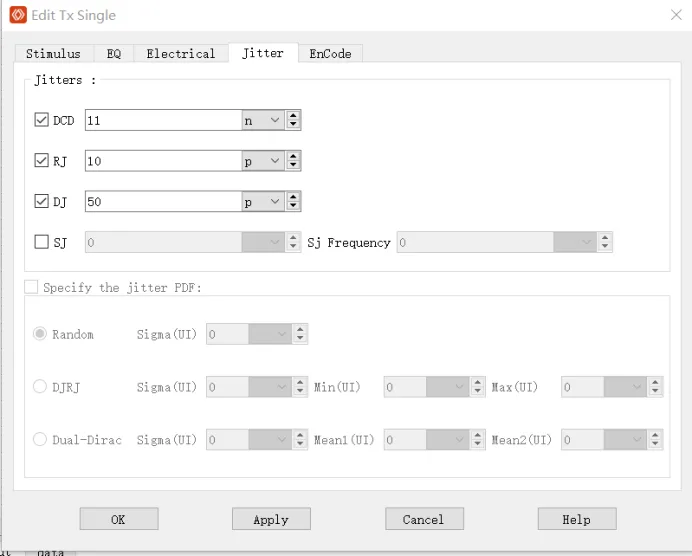

在仿真中,可以主动加入Jitter,在通过调整时钟源的稳定性、优化电路设计、改善信号完整性等方法来降低Jitter,达到信号的高质量传输。

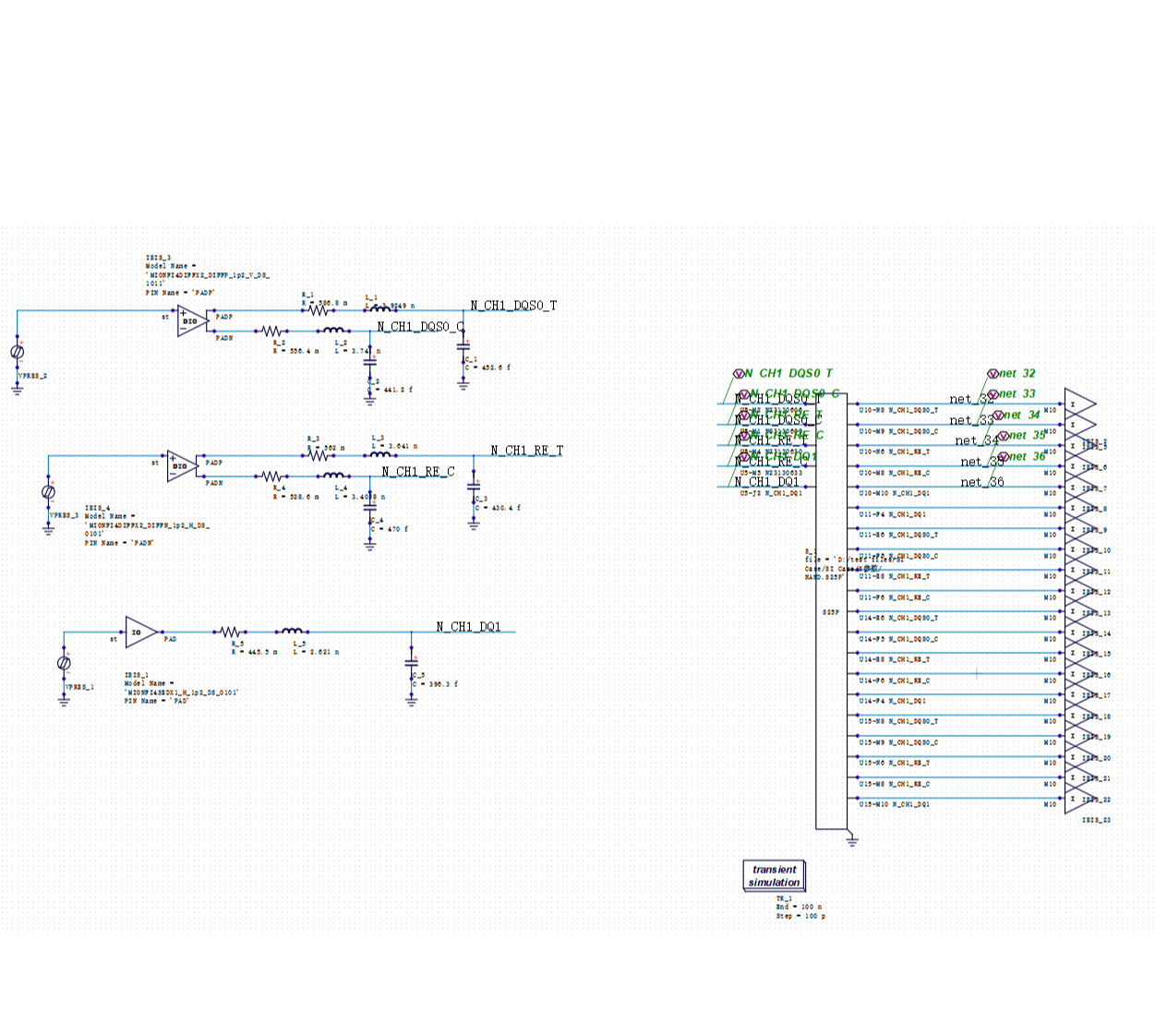

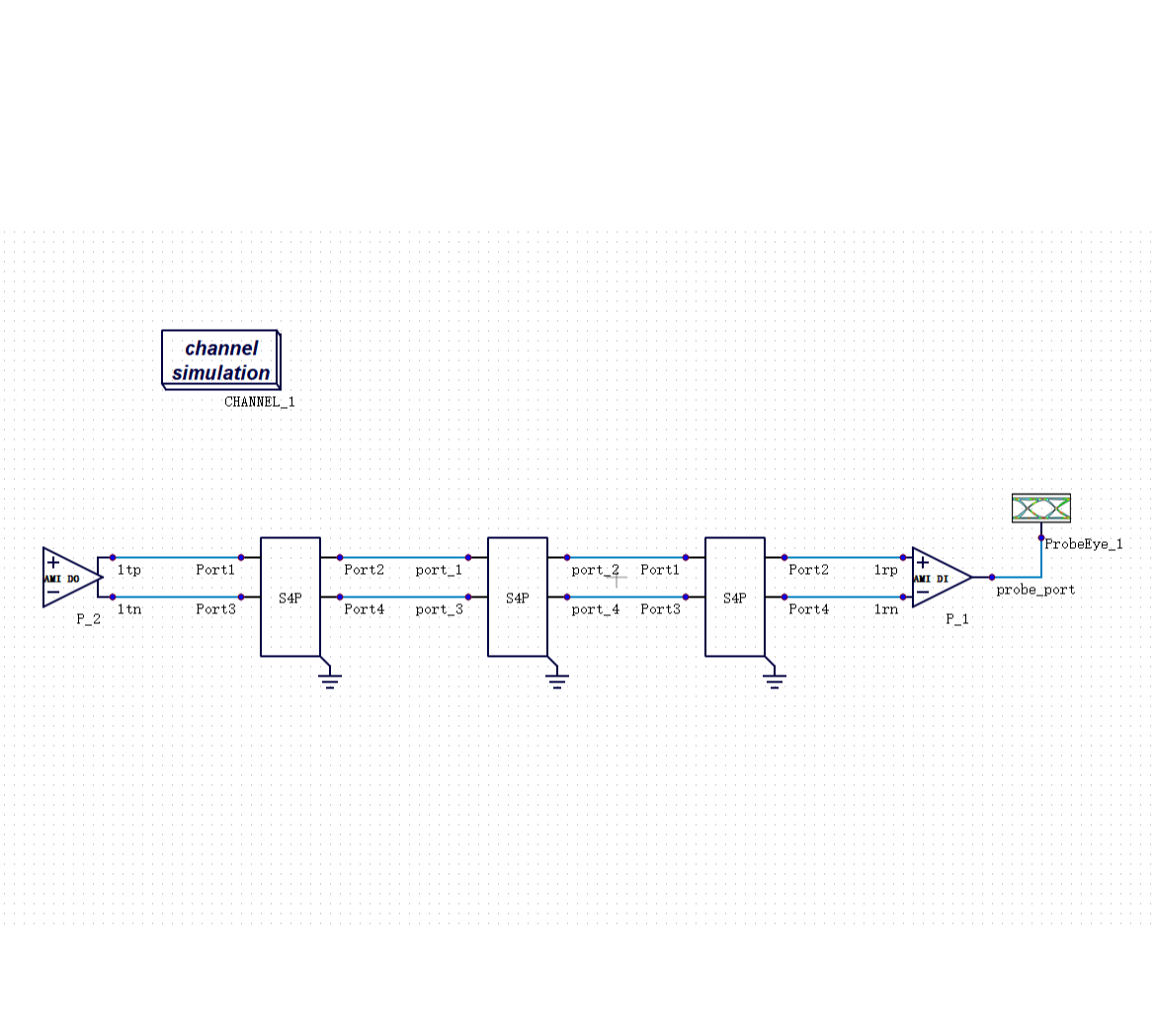

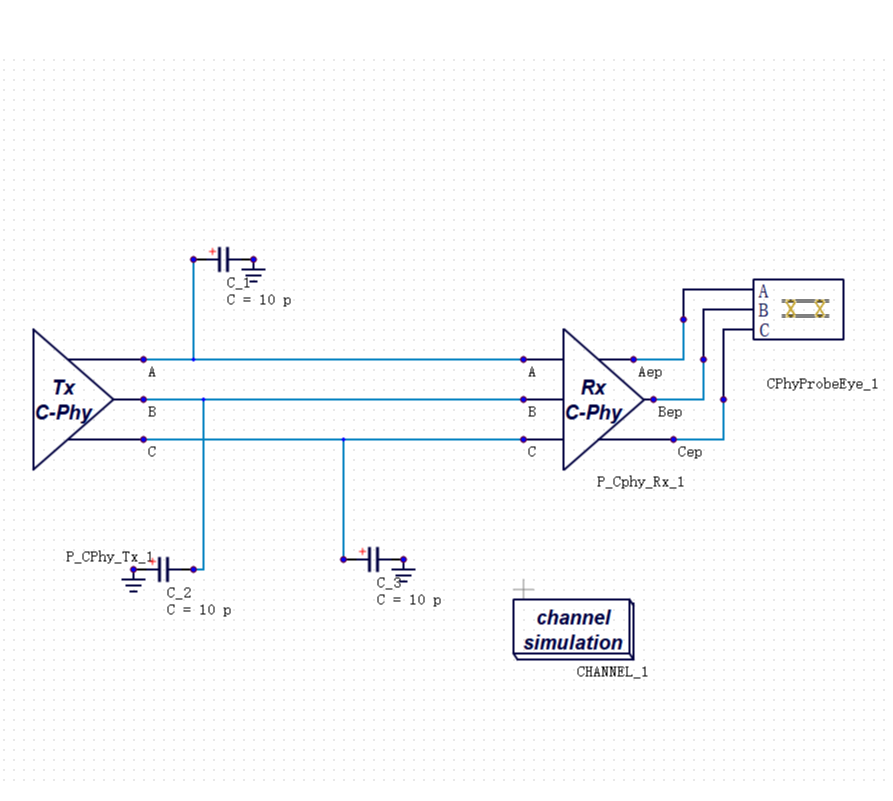

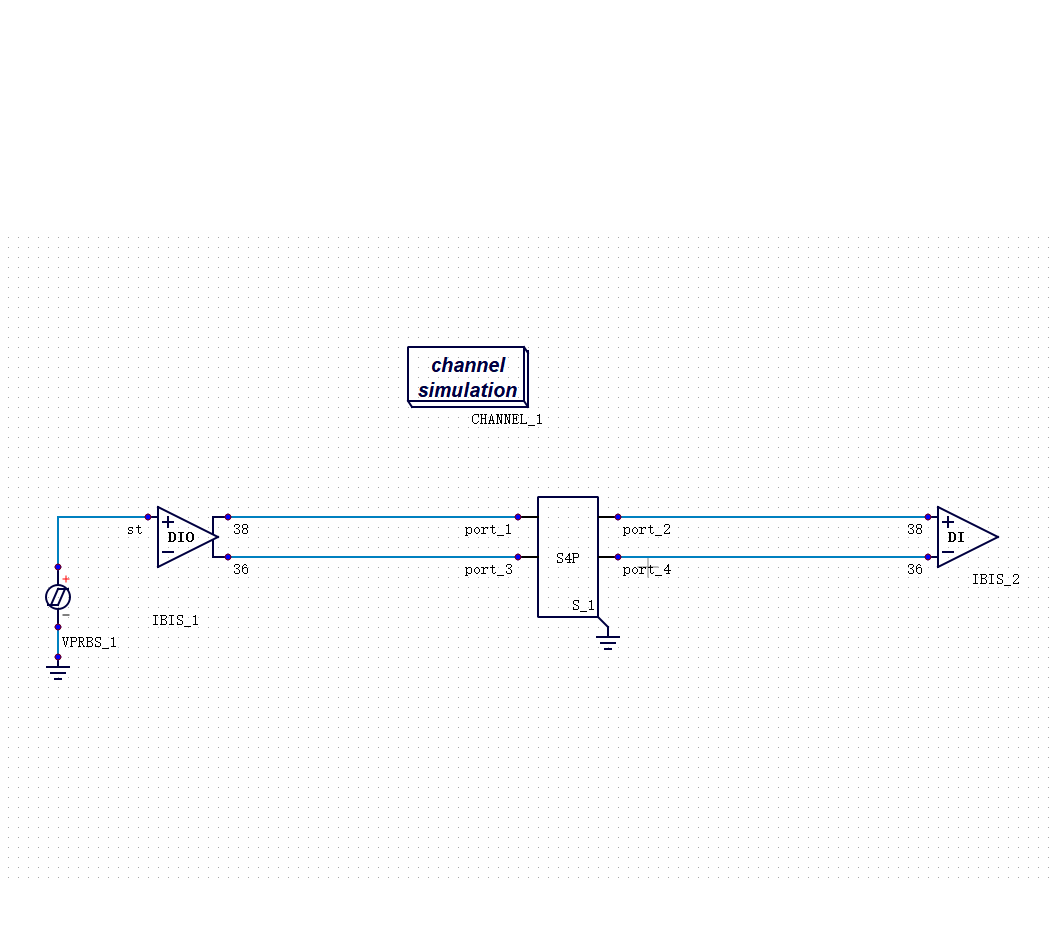

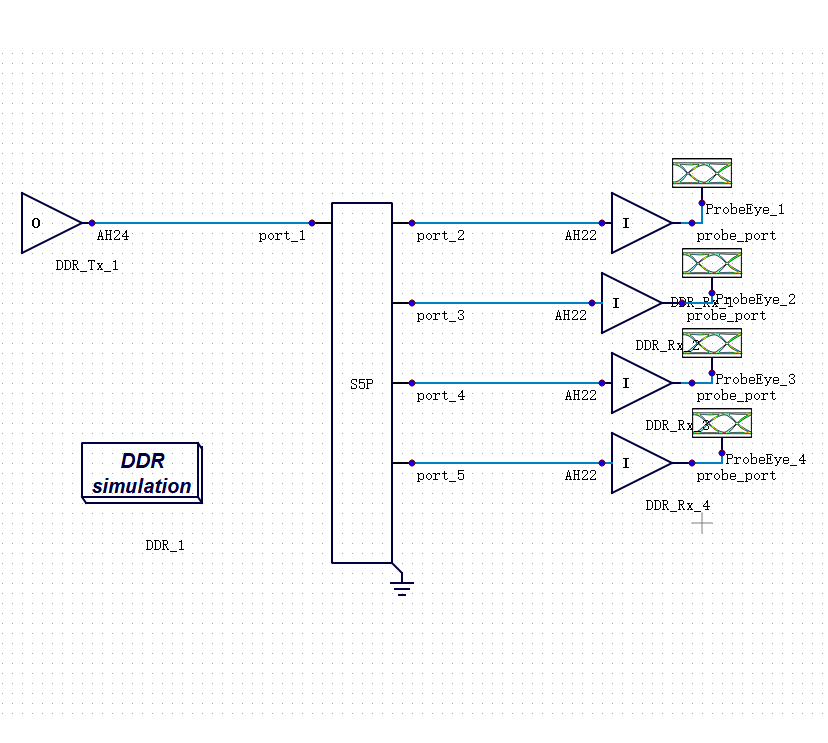

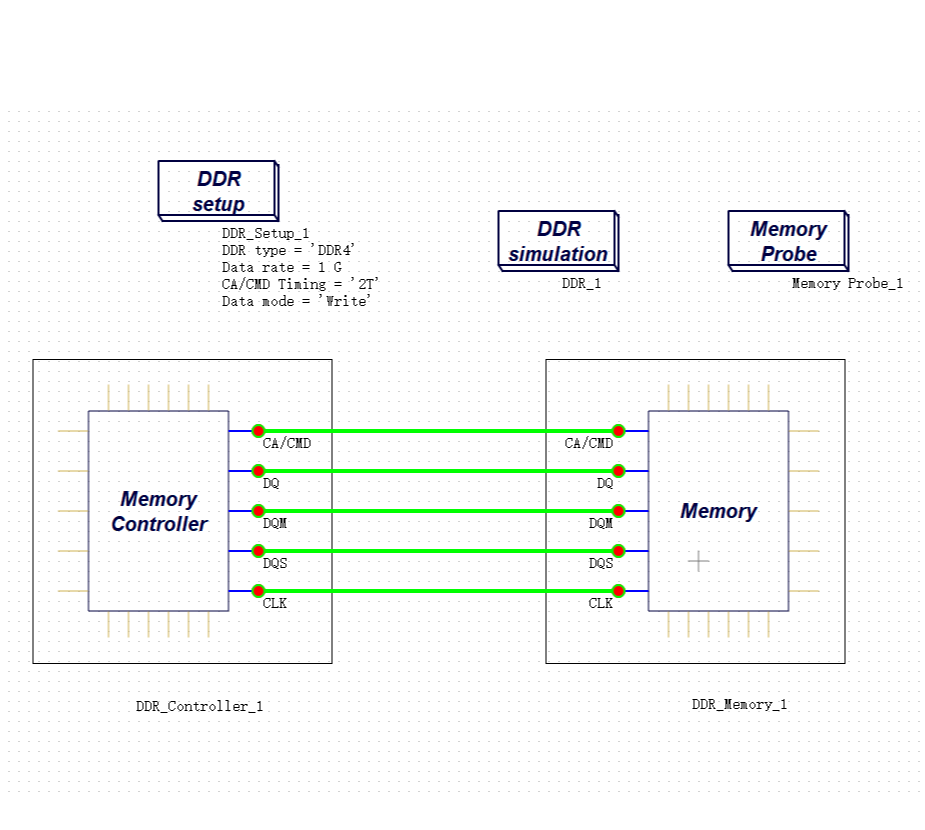

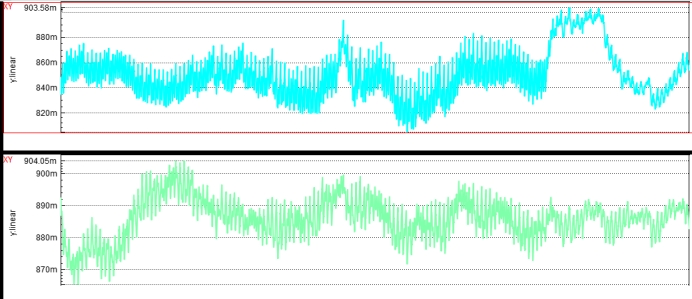

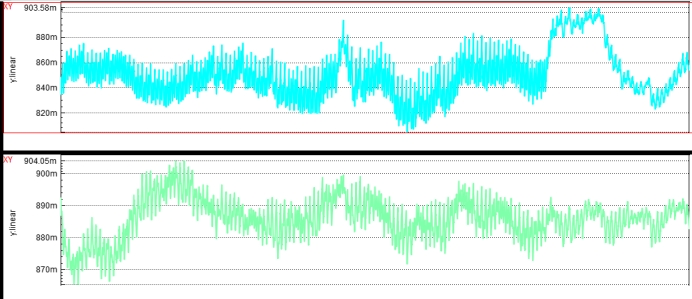

在巨霖的SIDesigner中,可以在发射端和接收端添加Jitter。

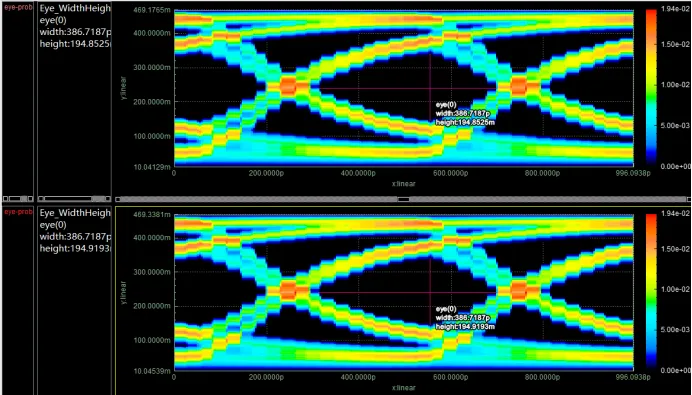

添加完Jitter进行仿真,通过眼高眼宽的测量对比前后眼图差异。

综上可知,通过巨霖SIDesigner进行Jitter仿真可帮助工程师更好地理解和控制信号在传输过程中的不稳定因素,为信号的高质量传输提供可靠支持。

欢迎点击 软件试用 申请试用我们的软件,过程中的任何疑问可联系support技术人员,期待与您的交流!

Recommended

-

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20

PanosSPICE: Establishing the "Golden Foundation" for Chip-Level Simulation2026.03.20 -

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13

The Dilemma of SPICE Simulation in Complex Chip Design: The Trade-off Between Accuracy and Efficiency2026.03.13 -

Chiplet packaging design faces multidimensional simulation challenges, with signal and power integrity becoming key technical bottlenecks.2025.10.29

Chiplet packaging design faces multidimensional simulation challenges, with signal and power integrity becoming key technical bottlenecks.2025.10.29 -

Power Supply Noise: The “Reef” of Electronic Systems and Strategies for Coping with It2025.07.28

Power Supply Noise: The “Reef” of Electronic Systems and Strategies for Coping with It2025.07.28